局部增强压焊块铝层厚度的工艺方法

2011-06-28马万里赵文魁

马万里,赵文魁

(深圳方正微电子有限公司,广东深圳 518116)

芯片封装打线工艺的发展趋势是逐步采用铜线做打线的线材,代替金线和铝线。主要是由于铜线有低的电阻率、高的热导率、价钱低等一系列的优势。但是铜线相对于金线和铝线,其硬度比较高,且容易氧化,打线的时候,容易将芯片压焊块打穿,所以用铜线在封装打线的时候,对芯片压焊块金属层厚度的要求也更高,并且越粗的铜线,对压焊块的金属层厚度要求越厚。而芯片制造工艺由于存在一定的局限性,并不能完全满足此要求,所以这种矛盾目前越来越突出。

1 铜线封装的常规做法

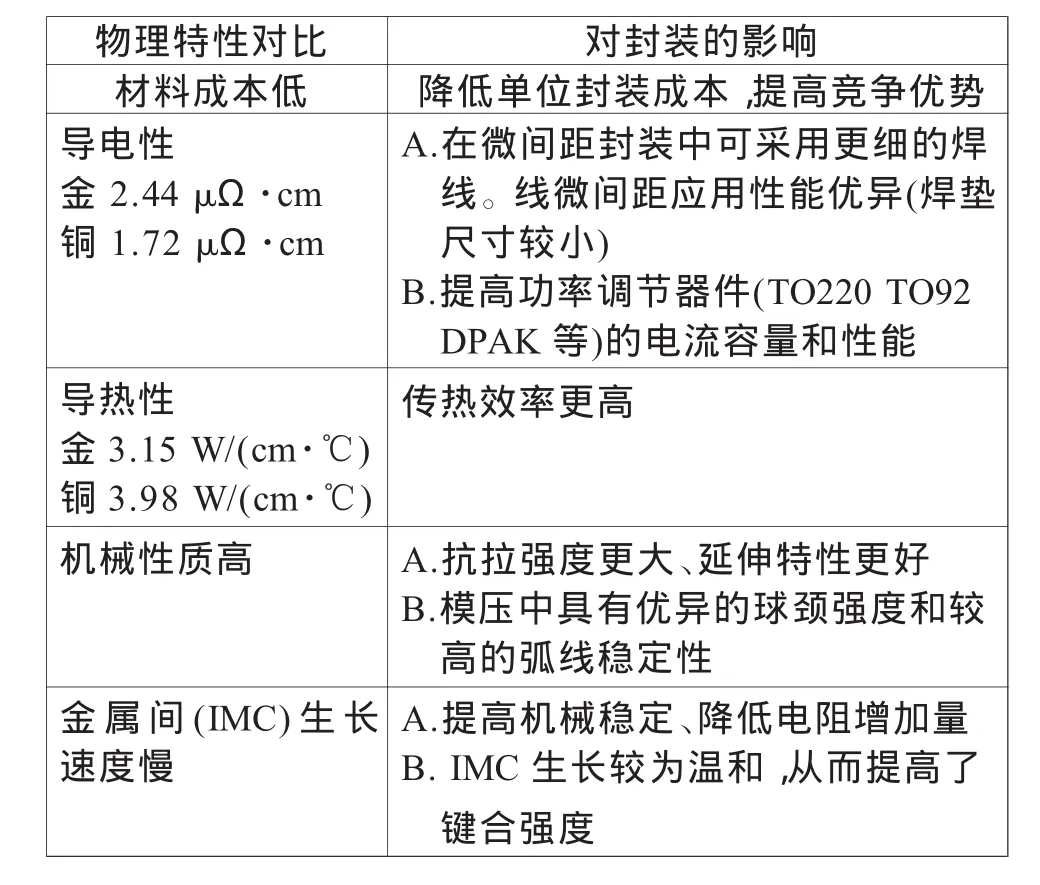

近年来随着金价的飞速上涨,铜线封装作为一种降成本手段,在加上原本的低电阻率等诸多优点(如表1所示),故越来越多的客户要求采用铜线封装代替金线。

表1 铜线封装的优点(与金焊线相比)

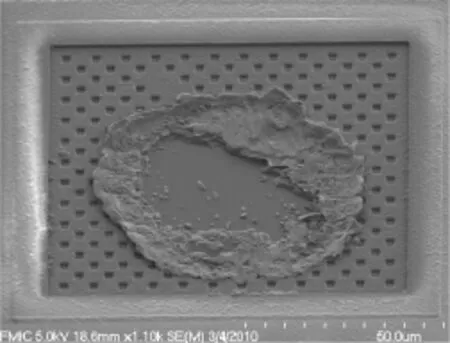

采用铜线封装时,不同封装厂的设备、工艺,对芯片压焊块铝层的厚度要求不同,如果铝层厚度不够,就会出现压焊块打穿的问题,如图1所示。

图1 打铜线时芯片压焊块的铝层被打穿

越是成熟的铜线封装工艺,对压焊块铝层厚度要求越低。一般情况下,不同粗细的铜线封装时对压焊块铝层厚度的要求不同,如表2所示。

目前已有的芯片制造工艺,压焊块的金属层厚度就不能完全满足铜线打线的要求。如果直接单纯的加厚的芯片制造工艺的金属层厚度,那会给金属层的线宽控制、刻蚀带来很大的麻烦。同样的金属条宽度/间距,金属层越厚,金属线条的高度/宽度比越大,金属刻蚀的困难就越大(如图2所示)。

表2 铜线封装对压焊块金属层厚度的要求

图2 薄金属层与厚金属层在刻蚀时的差异

目前的解决办法是,封装厂在不断地优化改进铜线封装水平,以便当芯片压焊块金属不额外增厚的情况下,能将打线工艺完成。但是,这个改进,一直没有达到理想的水平。能够做好铜线封装的厂家,并不多。更关键的是,现在越来越多的客户,为了降低封装成本,陆续都采用铜线封装,不断地要求芯片制造厂要满足铜线封装工艺,这个问题在近两年内显得非常突出,这就要求芯片制造工艺必须做某些改善。

2 钝化层反版局部加厚压焊块金属层

2.1 局部加厚压焊块金属层的方法

在钝化层制作以后,再进行一次金属溅射、光刻、刻蚀,不过此时采用的掩模版,需要将压焊块区域的金属保留下来。其他的金属全部在酸槽中腐蚀掉。具体做法如下:

第一步:金属层的溅射、光刻、刻蚀。此步需要根据芯片功能需要,完成芯片内的金属走线,同时形成压焊块,此时压焊块表面的金属与芯片内金属走线的金属厚度一样。因为走线的线条宽度与间距是比较小的,所以此工序不能生长太厚的金属层。

第二步:钝化层的生长、光刻、刻蚀。生长钝化保护层,并且将压焊块的区域刻蚀出来。此时压焊块上金属层厚度,可以满足金线和铝线的打线要求,但是不能满足铜线的要求。

第三步:第二次金属层的溅射(溅射后如图3所示)、光刻、刻蚀(刻蚀后如图4所示)。目的是在压焊块区域上,再做上一层金属,而芯片内,金属走线的金属层没有被加厚,所以此时d1>d2。此处生长的金属层,其对均匀性/反射率等参数,要求并不高,生产线可以安排较陈旧的溅射/蒸镀设备来作业,以提高设备的利用率。并且由于压焊块的尺寸以及间距都很大(都在几十微米以上),故此处完全没有了金属层细线条/间距对刻蚀的影响限制,所以可以生长很厚的金属层(可达数微米厚),并且后续的刻蚀也是完全没有问题的,可以采用湿法刻蚀,工艺成本也不高,速度也快,常规湿法铝腐蚀液成份为:H3PO4:HNO3:CH3COOH:H2O=16:1:1:2。

图3 第二次金属层溅射以后的结构

图4 第二次金属层刻蚀以后的结构

采用如上的方法,可以只将芯片的压焊块区域的铝层加厚,而其它区域的铝层不受影响。图5 、图6是钝化层上生长铝前后的对比。

后续在进行打铜线时,压焊块区域就能够满足打线需求。验证实验中,采用直径为20 μm的铜线,在Eagle60AP型号的打线机上进行打线,对于铝层总厚度为1.8 μm的压焊块(第一层铝0.8 μm,利用PAD反版又加厚了1μm),打线失效率仅为0.76%。完全能满足打铜线量产的质量要求。

图5 未加厚铝层前的压焊块

图6 加厚铝层后的压焊块

2.2 局部加厚压焊块铝层的工艺控制要点

2.2.1 铝层的刻蚀

由于最后一次生长的铝层位于钝化层之上,后续刻蚀需要保证不能损伤钝化层,故只能采取湿法腐蚀的方式进行,并且此层腐蚀的图形只是一系列与压焊块大小的铝块,线宽在几十微米以上,所以过蚀量可以设置的大一些(100%以上),确保钝化层表面不残留有铝。

2.2.2 最后一层铝的生长

此层铝用于打线,并且做完湿法腐蚀后,不会再进行其它方式的刻蚀,所以此层铝的表层不能生长抗反射层TiN。再者此层线宽很大,光刻也不存在问题,所以也没有必要再生长TiN。

2.2.3 在加厚的铝层生长后进行光刻时的胶残留

在钝化层表面生长金属以及进行涂胶,会产生一种特殊的问题,由于钝化层覆盖在金属条上以后,会在金属条之间形成一系列很小的缝隙,此时生长金属或者涂胶时,就会有一些金属长进去或者光刻胶流进去,同时由于这些缝隙太小,会造成显影无法将缝隙中的光刻胶去除,刻蚀也无法将缝隙中的铝腐蚀掉,试验中,加厚的铝层为M2i溅射机生长的1 μm铝层,涂胶为1.3 μm的正性光刻胶,显影后的情形如图7所示。可以看到,钝化层的缝隙之间存在无法去除的光刻胶。这会在最后的合金化步骤中,因为光刻胶的受热碳化而污染炉管,这是我们不能接受的。

图7 钝化层上生长铝层/涂胶/显影后的情形

为了避免污染炉管,实验中尝试采用先合金,再进行光刻的办法。就是当加厚的铝层生长好以后,先进行合金化,然后再进行光刻步骤。此时,即使光刻时会在小缝隙中残留光刻胶,也不会污染炉管。但这又会产生另一个问题,由于铝膜在经过合金化后,膜层表面会生长出一些凸起,俗称hill lock。然后在后续的PAD反版光刻工艺时,由于这些Al凸起对光线的散射/反射等因素,造成了光刻机套准的困难。通过设置合适的对准模式(FIA),可以解决套准不通过的问题。

3 其它方式局部加厚压焊块铝层工艺

(1)先将压焊块局部加厚,再做常规金属层生长刻蚀。先进行铝层生长,通过光刻/湿法刻蚀,只将压焊块区域的铝层留下来,然后进行金属层的生长,刻蚀出金属线条。

(2)一次性生长厚的铝层,再进行两次刻蚀。

先一次性生长足够厚的铝层,通过光刻/湿法刻蚀,将压焊块区域的厚铝全部保留下来,但其它区域的厚铝只刻蚀一半的厚度,对剩下的铝层,再进行光刻/刻蚀,做出金属走线。

4 结束语

目前采用铜线封装工艺是大势所趋,在各个封装厂的铜打线工艺能力良莠不齐的情况下,对芯片压焊块铝层厚度的要求也是差异很大,为了满足客户的要求,芯片制造工艺就不得不做出一些必要的优化。

将来随着封装厂铜线工艺能力的提高,对芯片压焊块的铝层厚度依赖度就会逐渐降低,芯片制造就不必为此进行这些额外的工艺。

[1]Dr.Christopher.微电子器件封装中铜与金球键合的比较[J].电子工业专用设备,2009,38(7):29-32.

[2]鲁凯,任春岭.铜丝球键合工艺及可靠性机理[J].电子与封装,2010,10(2):5-10.

[3]常红军,王晓春.铜丝键合工艺研究[J].电子工业专用设备,2009,38(5):20-24.

[4]丁雨田,曹军.电子封装Cu键合丝的研究及应用[J].铸造技术,2006,27(9):971-974.

[5]吴建得,罗宏伟.铜键合线的发展与面临的挑战[J].电子产品可靠性与环境试验,2008,26(6):42-45.

[6]H.K.CharlesJR,K.J.Mach,S.J.Lehtonen.Wire Bonding atHigher UltrasonicFrequencies[J].ReliabilityandProcess Implications.Microelectronics Reliability,2003,43(1):141-153.

[7]毕向东.半导体封装业中铜线键合工艺的应用[J].电子与封装,2010,10(8):1-4.

[8]鲁凯,王春青.Cu引线超声键合FAB工艺及影响研究[J].电子工艺技术,2008,29(4):192-207.