新型超宽带探地雷达数字采样接收机设计

2011-06-04叶盛波方广有

叶盛波 周 斌 方广有

(1.中国科学院研究生院,北京 100190;2.中国科学院电子学研究所,北京 100190)

1.引 言

探地雷达(GPR)是利用超高频脉冲电磁波探测地下介质分布的一种地球物理勘探方法,它具有快速、简便的对浅层目标和结构进行无损探测的特点,已被广泛应用于城建、交通、地质、考古、国防等部门[1]。由于具有分辨率高、电路系统接收简单等优点,已被产品化的探地雷达基本上都采用无载频毫微秒脉冲信号体制。

在宽带脉冲探地雷达系统中,雷达接收机多采用等效时间采样技术[2]。该方法需要一个模拟采样门电路将周期重复的高频降频为低频信号。常见的取样门主要有桥式肖特基二极管取样门[3-5]或者由取样相位检测器(SPD)构成的取样门[6-7]。这些采样门的带宽能达到数GHz以上,但基于这些采样门结构的接收机属于模拟接收机,信号在降频的过程中,可能会丢失部分原始信息。同时这种接收机不仅回波利用率较低,而且电路调试难度大。

与模拟接收机不同的是,数字接收利用高速模数转换(A/D)对信号进行实时采样,回波利用率很高,电路灵活性好。实时采样不需要对信号进行降频,从而保留了信号的所有信息[8]。然而高速A/D芯片的成本一般成本高、功耗大。另外,由于高速A/D需要的时钟频率高,容易产生电磁干扰。同时,高速A/D输出的数据码流高,增加了后续的存储、处理等电路的复杂度。

综合考虑模拟接收机和数字接收机的优缺点,结合等效时间采样和实时采样,论文提出了一种新的探地雷达采样技术——等效数字采样[9]。该方法的基本思想是通过现场可编程门阵列(FPGA)编程,对脉冲回波信号进行1比特采样并进行均匀量化,实现脉冲回波信号的等效接收和数字化。利用该思想,本文研制出无集成A/D的探地雷达数字接收机。该接收机的模拟带宽达500MHz,可应用于中心频率低于300MHz的超宽带探地雷达系统中。同时它具有等效7位、4.096GHz采样率的模数转换功能,从周期性的雷达回波得到任意点的A-scan波形仅需经历512个回波周期。与传统探地雷达接收机相比,电路结构简单、功耗低、回波利用率高。

2.数字接收机采样原理分析

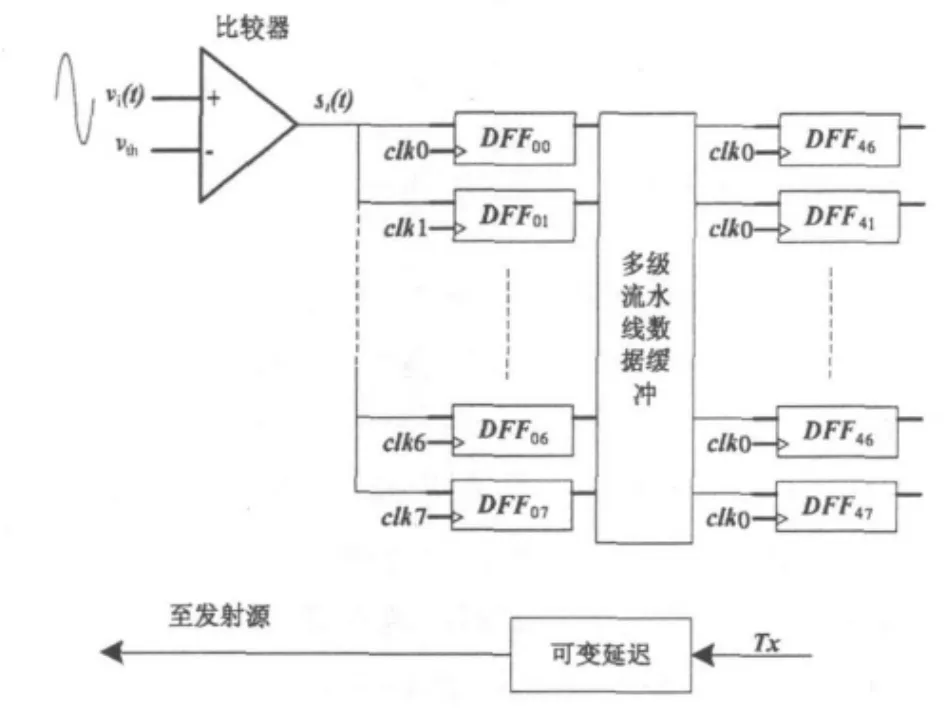

数字接收机采样原理图如图1所示。其电路基本结构主要包括采样接收电路和触发延迟电路。采样基本过程通过1比特并行交替实时采样、延迟采样和均匀量化3部分来完成。

图1 数字接收机采样原理框图

2.1 1比特并行交替实时采样

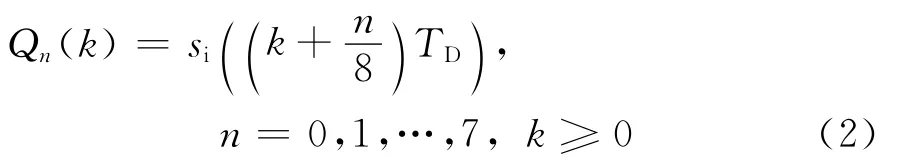

设比较器后级的八个D采样触发器DFF00~DFF07的输入时钟分别为clk0~clk7,频率均为fD,相邻相位差为45°。则第n个D采样触发器输出序列为

式中TD=1/fD.

将Q0(k)~Q7(k)这8个序列按照时间先后进行排序后,可以得到等效采样率为8fD的1比特的实时采样,即

2.2 延迟采样

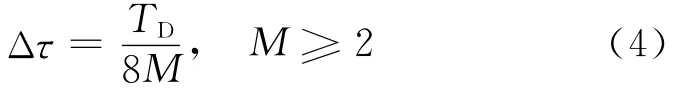

为了进一步提高采样率,将发射机的同步触发信号Tx经过可变延迟单元延迟一个小的时间间隔,同时保持相同的采样时刻。设可变延迟单元的延迟步进量为Δτ,并且满足

设第m次延迟量为Δt(m),且满足:则Tx经过Δt(m)的延迟后,得到的1比特交替并行实时采样的结果ym(k)为

经过M次延迟后,将M次延迟触发后的1比特交替并行实时采样的结果y1(k)~yM(k)构造为二维数据矩阵Y[m][k],且有

对该矩阵数据元素按列读取,即可得到延迟采样后的1比特数据so(k)为

可以看到,经过M次延迟采样后,可以得到等效采样率fs为

采样率提高了M倍。

2.3 均匀量化

为提高量化精度,改变比较器反相端的阈值电压vth,设第j个阈值电压vth(j)满足

式中:v0为初值;Δv为递增量。设在vth(j)下得到的8MfD的1比特采样序列为soj(k),则经过J次比较后,将J次的1比特采样序列soj(k)进行累积,可以得到第k个采样点的等效量化值d(k)为

等效量化位数Nbit为

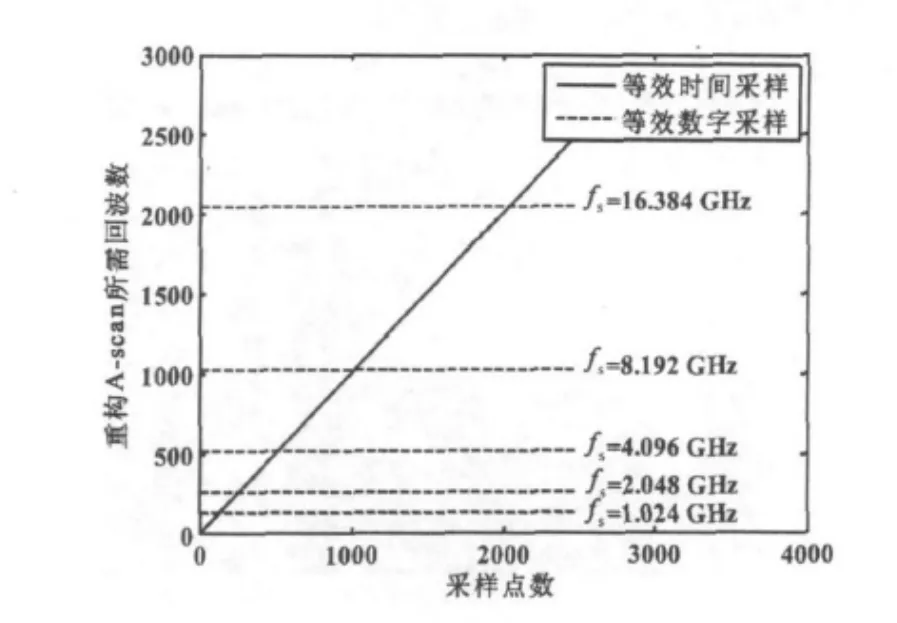

从上面的结果可以得到:经过M×J个相同的输入信号后,可以得到等效Nbit位、8fDM采样率的模数转换,该结果和直接用Nbit位、8fDM采样率的集成商用A/D的结果是等效的。在实际应用中,Δv可根据比较器允许的输入电压范围以及系统等效量化位数Nbit来确定。为减小重构A-scan所需要的回波数,一般Nbit选择7或8。图2为Nbit=7,fD=128MHz和不同的fs下,等效时间采样以及等效数字采样重构A-scan所需要的回波数与采样点数的关系曲线图。以fs=4.096GHz为例,当采样点数大于512点时,等效数字采样的回波利用率要优于等效时间采样。

图2 重构A-scan所需要的回波数与采样点数的关系曲线图

3.数字接收机的实现

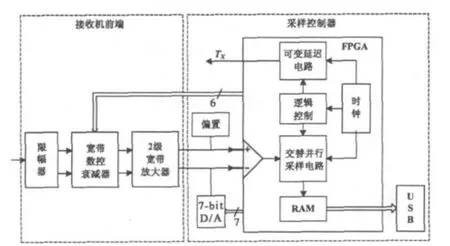

设计的数字接收机的原理框图如图3所示。接收机主要由接收机前端和采样控制器两大部分组成。接收机前端的作用是对雷达回波信号进行预处理,从而改善接收机的动态范围。采样控制器除了完成等效7-bit、4.096GHz采样率的模数转换功能外,还要完成接收机前端的衰减控制功能、发射机触发控制功能以及通过通用串行总线(USB)接口与PC机进行数据通信等功能。

图3 数字接收机原理图

3.1 接收机前端

从接收天线得到的差分雷达回波信号首先进行限幅,以保护后级的射频器件;然后经过数控宽带衰减器,衰减器最大衰减范围是50dB,最小衰减步长为1dB;最后,信号再经过两级宽带放大器进行放大,两级放大增益为50dB;放大后的差分信号经过适当的直流偏置后接到采样控制器进行模数转换。

3.2 采样控制器

采样控制器主要由 FPGA、7-bit D/A 以及USB控制器组成。其中FPGA是整个控制器的核心,所用的FPGA是Xilinx公司的XC3S400系列。该款FPGA不仅具有丰富的逻辑资源和存储资源,而且还具有时钟管理单元等。另外它还支持多种不同标准的差分端口,如2.5V低压正极性发射极耦合逻辑(LVPECL)、2.5V 低压差分信号(LVDS)等。等效数字采样系统由FPGA的LVPECL差分输入端口、7-bit D/A以及FPGA内部D触发器构成,整个数字采样系统等效采样率为4.096GHz,7-bit量化位数,最小量化电压为4.3mV.

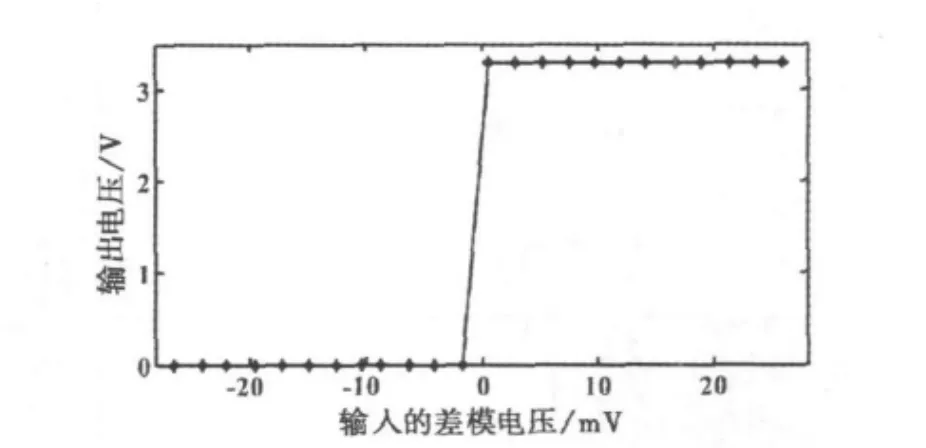

差分输入端口作为等效数字采样系统中的高速比较器[10]。LVPECL差分端口支持的最高速率能达数GHz以上,为保证正确输出,理论上要求差分端口输入的差模电压()大于100mV,但实际测量结果表明,当小于2mV时,LVPECL差分端口仍然能正常工作。图4为差分端口实测结果。

7-bit D/A通过权电阻网络来实现等效D/A的功能。D/A的输出作为比较器反相输入的阈值电压,其输出范围为549mV,电压输出分辨率为4.3 mV.电压输出值通过FPGA的7位端口对权电阻网络进行控制。

图4 差分输入端口特性测试图

采样电路中的8个D触发器的工作频率均为128MHz,由FPGA内部的数字时钟管理(DCM)来实现相邻两个时钟间45°的相位差,由于时钟是在FPGA内部产生,既减小了对外围电路的电磁干扰,同时还能很好的保证时钟间的相位关系。

量化累积的算法以及数据排列的算法都在FPGA中进行,以减小数据量和上位机的工作量。采样得到的数据最终通过高速USB接口传送到PC机并通过VC界面进行显示。

4.实验结果分析

整个接收机的功耗低于1.5W,采用笔记本电脑对其进行5V供电。在整个雷达接收机中,由于接收机前端较容易满足宽带低噪声的特性,所以采样控制器的性能决定了整个接收机的性能。

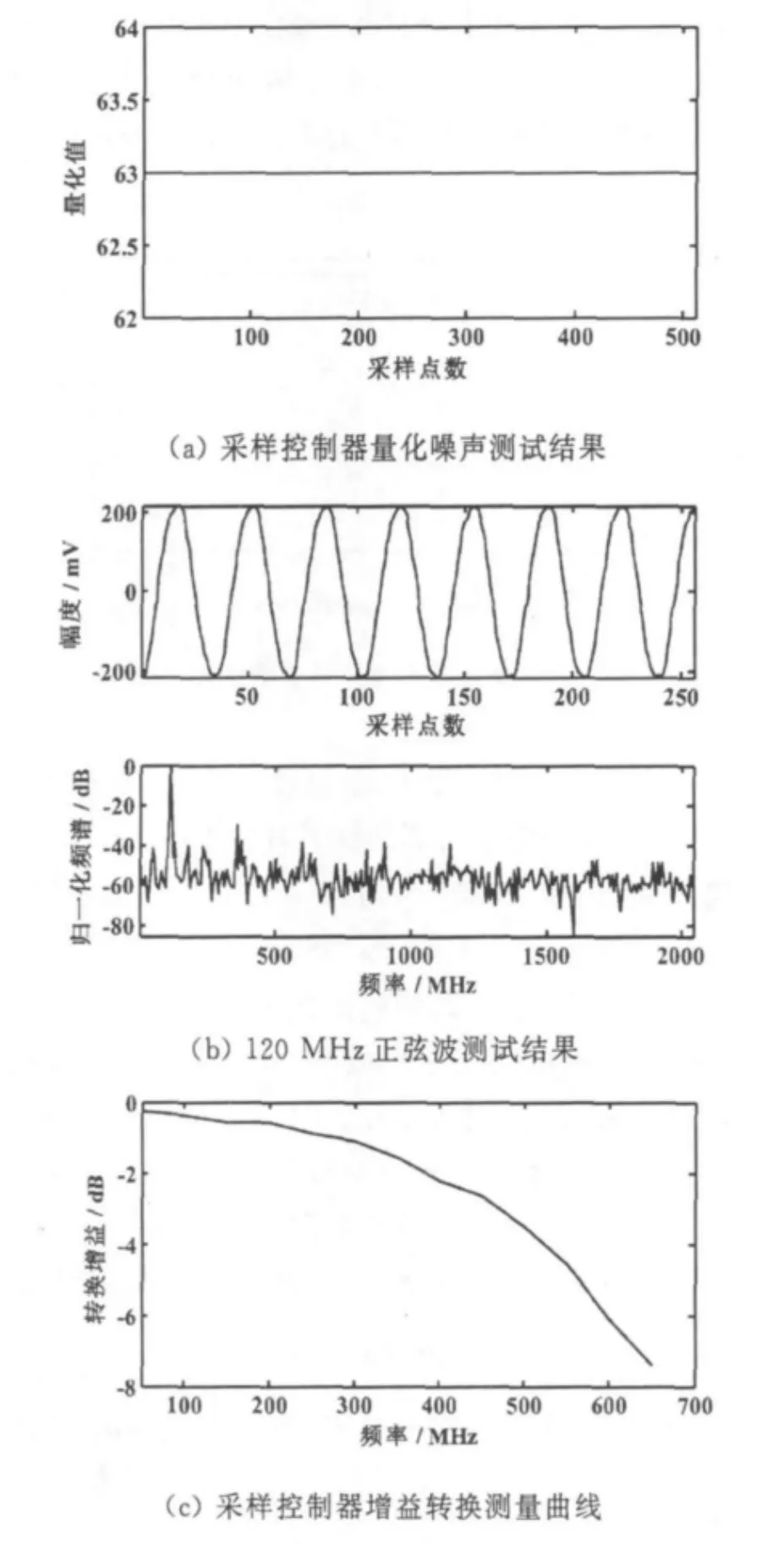

图5(a)为采样控制未接入模拟信号时(比较器同相端有固定直流偏置电压),整个采样控制器量化噪声测试结果。整个采样控制器的噪声来源主要有:D/A的输出电压、偏置电路、电源和地。这些噪声共同作用的结果直接影响了采样控制器的量化噪声水平。从测试的结果来看,512个采样点具有相同的量化值,可知整个采样控制器的量化噪声低于2.2mV,即最小量化电压的一半(0.5Δv)。

图5(b)为采样控制器转换标准信号的测试结果。测试输入信号为120MHz的正弦波信号,信号的峰峰值为450mV,采样控制器触发重复频率为33kHz.从图中给出的结果看,重构后的信号在幅度和周期上与原始输入信号非常吻合,说明该采样控制器在不需要集成A/D的情况下能很好的完成信号的模数转换。

图5 测试结果图

为测试采样控制器的输入带宽,利用信号源AWG7122B产生50~650MHz的正弦波信号,接入采样控制器进行采样。经过测试,该采样控制器的增益转换曲线[11]如图5(c)所示。从曲线上可以看到,该采样控制器的-3dB输入模拟带宽约为500 MHz.

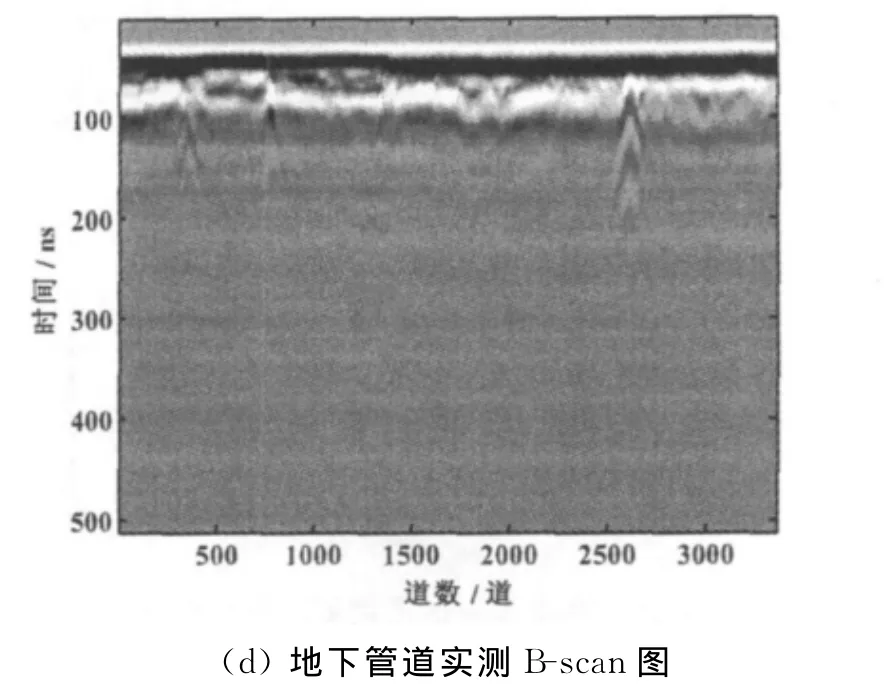

为进一步测试该接收机在实际探地雷达系统中的性能,我们将该接收机和已有的发射机、收发天线集成在一起,研制出一套完整的脉冲探地雷达系统。其中发射机输出的脉冲峰值幅度为±400V,脉宽约为8ns.天线工作的中心频率为100MHz.图5(d)为地下管道测试B-scan图,图中第332道、777道、1338道、1795道、2603道处含有管道散射的较强回波,他们呈明显的双曲线,是管道等线状目标B-scan回波出现的特征。实测结果表明:该雷达系统具有很好的探测性能,同时也证明了设计的接收机具有很好的接收性能,能满足实际探地雷达系统的要求。

5.结 论

论文提出了一种新型的数字采样接收方法——等效数字采样。该采样技术不需要采用集成A/D,而是通过对模拟信号进行1比特并行交替采样、多次量化累积来实现模数转换的功能。该方法不仅克服了传统探地雷达模拟接收机需要模拟采样门而导致的信号丢失、电路调试难度大的缺点,而且还克服了数字接收机需要高速A/D而造成的电路复杂、成本高、功耗大等缺点。基于该采样思想,利用单片FPGA和少量外围器件实现等效4.096GHz采样率、7位精度模数转换功能的数字接收机。整个接收机电路结构简单,性能稳定,整机功耗不超过1.5 W,采用笔记本进行供电。实测结果表明:该接收机具有很低的量化噪声,能很好的重构输入信号,模拟带宽达500MHz,可应用于中心频率低于300MHz的冲击脉冲探地雷达系统中。同时外场试验测试结果也证明了该接收机在实际探地雷达系统中具有很好的性能,能满足实际探地雷达的应用需求。

[1]BASTARD C L,BALTAZART V,WANG Y,et al.Thin-pavement thickness estimation using GPR with high-resolution and superresolution methods [J].IEEE Trans.on Geoscience and Remote Sensing,2007,45(8):2511-2519.

[2]甘 露,甘良才,田 茂,等.高分辨率探地雷达步进系统的研究与实现[J].电波科学学报,2008,23(3):555-559.

GAN Lu,GAN Liangcai,TIAN Mao,et al.Stepsampling system of high resolution ground penetrating radar[J].Chinese Journal of Radio Science,2008,23(3):555-559.(in Chinese)

[3]徐玉清,张国进,高 攀.冲击脉冲雷达探雷[J].电波科学学报,2001,16(4):546-550.

XU Yuqing,ZHANG Guojin,GAO Pan.Land-mine detection with impulse radar[J].Chinese Journal of Radio Science,2001,16(4):546-550.(in Chinese)

[4]ZHANG Ceming,FATHY A E.Performance enhancement of a sub-sampling circuit for ultra-wideband signal processing[J].IEEE Microwave and Wireless Components Letters,2007,17(2):873-875.

[5]刘丽华,陈 洁,方广有.平衡馈电超宽带探地雷达系统的研究与实现[J].电波科学学报,2010,25(2):313-317.

LIU Lihua,CHEN Jie,FANG Guangyou.Research and implementation of the balanced feeding UWB ground penetrating radar system[J].Chinese Journal of Radio Science,2010,25(2):313-317.(in Chinese)

[6]REISENZAHN A,BUCHEGGER T,KAINEDER G,et al.Phase synchronization in UWB receivers with sampling phase detectors[C]//Proc.IEEE MTT-S.Long Beach,CA,2005:1887-1890.

[7]LIU Lihua,FANG Guangyou.A novel UWB sampling receiver and its applications for impulse GPR systems[J].IEEE Geoscience and Remote Sensing Letters,2010,7(4):690-693.

[8]TSUI J Y,STEPHENS J P.Digital microwave receiver technology[J].IEEE Trans.Microwave Theory and Techniques,2002,50(3):699-705.

[9]叶盛波,周 斌,方广有.新型探地雷达内同步接收机设计[J].仪器仪表学报,2010,31(10):2363-2367.

YE Shengbo,ZHOU Bin,FANG Guangyou.Design of a new internal synchronous ground penetrating radar receiver[J].Chinese Journal of Scientific Instrument.2010,31(10):2363-2367.(in Chinese)

[10]SOUSA F,MAUER V,DUARTE N,et al.Taking Advantage of LVDS Input Buffers to Implement Sigma-Delta A/D Converters In FPGAs[C]//Circuits and Systems,Proceedings of the 2004International Symposium,2004,1:I-1088-1091.

[11]YAN Ming,TIAN Mao,GAN Lu.Impulse ground penetrating radar hardware system design[C]//Proc.6th International Conference on ITS Telecommunications Proceedings.Chengdu,2006:1244-1247.