通孔微结构对Cu/低-k应力诱生空洞的影响*

2011-03-15林晓玲侯通贤章晓文姚若河

林晓玲 侯通贤 章晓文 姚若河

(1.华南理工大学电子与信息学院微电子研究所,广东广州510640; 2.工业和信息化部电子第五研究所电子元器件可靠性物理及其应用技术国家级重点实验室,广东广州510640)

随着半导体技术的不断进步,Cu大马士革工艺已成为重要且关键的后端线(BEOL)金属化工艺,但新的Cu互连材料和集成工艺也引发了一系列新的互连可靠性问题.在工艺发展和晶圆制造过程中,电迁移、金属层间与时间有关的层间介质击穿和应力诱生空洞(SIV)成为影响Cu互连可靠性的主要因素.相比于其它BEOL可靠性项目,与SIV相关的失效——Cu通孔内部或通孔底部下面互连的空洞,是跟热应力有关的失效模式,它会导致高电阻甚至电路功能失效.文献[1]中提出了活性扩散体的概念,指出Cu互连SIV与互连尺寸、应力和应力梯度有关.文献[2]中指出宽厚比为1的互连结构具有最大的静水应力.文献[3]中指出当通孔与底部相连接的互连为宽互连时,常在通孔底部互连产生SIV.

互连通孔和通孔阻挡层形成工艺的波动性将影响互连通孔结构的尺寸,由此带来的通孔微结构效应对互连通孔和通孔底部互连SIV的影响需要被更好地理解.文中研究互连通孔和通孔阻挡层形成的工艺波动性对Cu/低-k互连通孔微结构的影响,基于Cu的随动强化模型[4],使用有限元分析(FEA)方法,模拟分析通孔微结构效应对互连通孔和通孔底部互连金属中的热应力分布,分析了不同应力级别与SIV强度之间的关系,探讨了不同BEOL通孔微结构对Cu/低-k互连SIV的影响.

1 通孔微结构依赖性的模拟模型

典型互连SIV测试中,通常采用高温应力作为检测SIV失效和鉴别薄弱工艺的主要方法.SIV导致通孔和Cu互连电阻升高,通孔底部的SIV甚至导致电路断开[5].

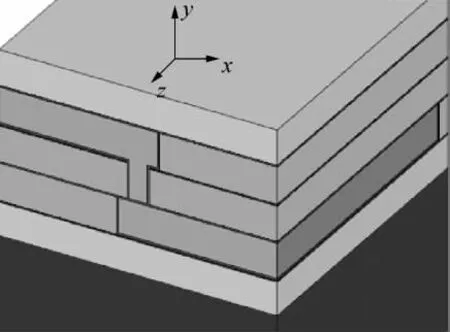

为了分析通孔微结构效应对互连应力特性的影响,建立包括钝化层的双层Cu/低-k互连3D有限元分析(FEA)模型结构,如图1所示.基于65 nm Cu互连工艺,模型开始于500μm厚的Si衬底和380nm高的SiO2.x、y和z轴分别定义了互连线的长度、高度和宽度方向.具有互连线M1(底层金属)和互连线M2(上层金属)的Cu双大马士革结构嵌入于模型中,互连金属高度为380nm.20nm厚的Ta被用作Cu和介质之间的扩散阻挡层.圆柱体互连通孔直径为180 nm.模型还包含了20 nm厚的蚀刻停止层(ESL).根据有关文献报道,通孔底部的SIV失效模式跟M2的尺寸有关[2],通孔底部互连线的SIV失效模式跟M1的尺寸有关[1,3],因此,为了研究通孔微结构效应对通孔和底部互连SIV可靠性的影响,M1和M2的长度都设置为10 μm.在模型中,除Cu以外的所有材料按各向同性和均匀的线性弹性材料处理,而Cu按各向同性的弹性-塑性材料处理,其后屈服行为符合随动强化模型,线性强化率H为77GPa[6].模拟的零应力温度和温度分别设置为350和175℃[1].通孔底部及其周围和通孔底部互连线M1及其周围用均匀尺寸单元进行网格划分.模拟计算结果的收敛性通过不同的网格细化达到.由于结构的对称性,用于数值计算的模型为整个模型的一半,对称面为xy平面.模型中所用材料的性能列于表1[7],其中E为杨氏模量,ν为泊松比,α为热膨胀系数,σy为屈服强度.

图1 SIV模拟有限元分析模型Fig.1 FEA model for SIV simulation

表1 模型中所用材料的特性参数Table 1 Property parameters of materials used in the numerical modeling

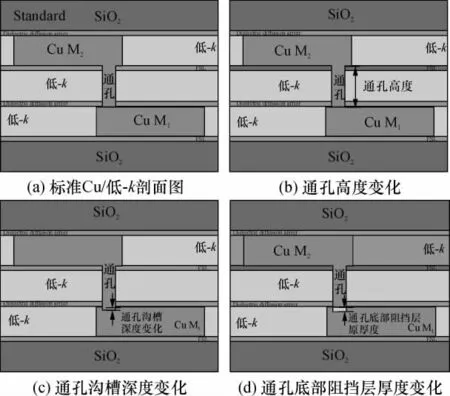

为了研究通孔微结构对互连通孔和通孔底部互连SIV的影响,4种情景被用于FEA模拟,如图2所示.图2(a)示出了通孔高度为380 nm、通孔底部阻挡层厚度为20 nm和无通孔沟槽的参考标准微结构.图2(b)为因电介质薄膜沉积工艺波动造成的通孔高度变化.在现有的Cu互连工艺中,因受到通孔过刻蚀和通孔底部Ar离子溅射清洗工艺的影响,底部互连不可避免地产生一定程度的通孔沟槽,图2 (c)为因过刻蚀和通孔底部Ar离子溅射清洗工艺波动造成的通孔沟槽深度变化.在沉积Cu互连阻挡层时,为了提高通孔阻挡层的质量,沉积完后需要进行通孔阻挡层的回流再溅射.图2(d)为因通孔阻挡层回流再溅射工艺波动造成的通孔底部阻挡层厚度变化.

图2 通孔微结构变化对通孔底部和通孔底部互连SIV的影响Fig.2 Effects of via microstructure variation on interconnected via and bottom interconnection SIV

实验证明,互连经历热烘烤时,通孔SIV跟y轴应力直接相关[8].互连中的静水应力[9]定义为σH= (σxx+σyy+σzz)/3,其中σxx、σyy和σzz分别为x、y、z轴正应力,应力的直接释放是底部互连空洞形成和生长的主要驱动力[1,3,5];互连中的等效塑性应变(von Mises有效塑性应变)表明,塑性诱生晶体缺陷(位错和空位)形成的趋势,会潜在地促进空洞的形成和长大、局域脱粘和随后的电迁移危害[10-12].因此,模拟之后,分别使用通孔底部的最大y轴应力、通孔底部互连M1的最大静水应力和最大等效塑性应变来评价通孔微结构对 Cu/低-k互连 SIV的影响.

2 结果和讨论

通孔微结构效应归为与层间介质薄膜沉积相关的通孔高度变化、与通孔过刻蚀和离子清洗工艺波动相关的通孔沟槽深度变化、与通孔阻挡层回流再溅射相关的通孔底部阻挡层厚度变化.

图3给出了与层间介质薄膜沉积相关的通孔高度变化对通孔底部最大y轴应力、通孔底部互连最大静水应力和最大等效塑性应变的影响.对于本模型结构,在通孔宽度不变的情况下,当通孔高度高于参考标准高度(0.38 μm)时,随着通孔高度的增加,通孔底部的最大y轴应力、通孔底部互连的最大静水应力和最大等效塑性应变不断变大.通孔底部最大y轴应力的相对增幅尤其明显(30.3% ~179.1%),而通孔底部互连的最大静水应力相对增幅(22.8%~30.4%)和最大等效塑性应变相对增幅(9.9%~19.2%)较小.当通孔高度低于参考标准高度时,通孔高度的减少对通孔底部的最大y轴应力、通孔底部互连的最大静水应力和最大等效塑性应变只有轻微的影响.综上所述,因层间介质薄膜沉积工艺波动造成通孔高度的变化,会对Cu/低-k互连SIV产生如下影响:当通孔高度变化造成通孔高宽比大于参考标准高宽比时,会对Cu/低-k通孔和底部互连的SIV产生强烈的影响,对互连通孔SIV的影响尤其突出,通孔内部出现空洞形核和生长的几率都增加.当通孔高度变化造成通孔高宽比小于参考标准高宽比时,对通孔和底部互连的SIV影响可控制在相对稳定的范围内.这也从另一个角度说明高宽比小的互连通孔结构比高宽比大的互连通孔结构具有更好的SIV可靠性.

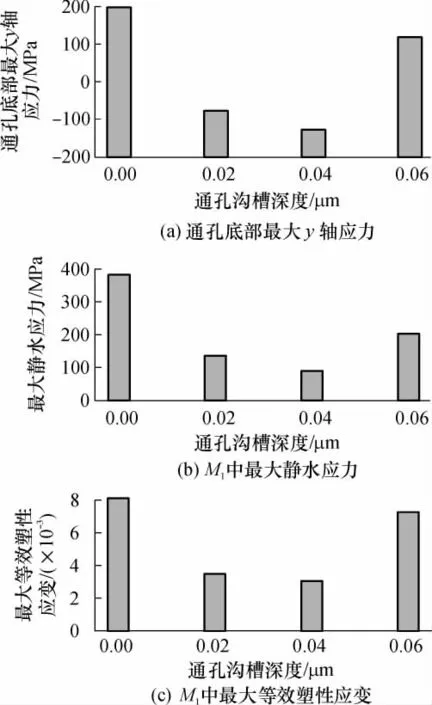

图4给出了不同通孔沟槽深度变化对通孔底部最大y轴应力、通孔底部互连最大静水应力和最大等效塑性应变的影响.通孔沟槽的存在减小了通孔底部的最大y轴应力、通孔底部互连的最大静水应力和最大等效塑性应变,减小的相对幅度分别为43.5%~172.8%,48.5%~79.3%和10.7% ~64.3%.结果表明,通孔沟槽的存在可以提高Cu/低-k互连通孔和通孔底部互连的SIV可靠性.但随着通孔沟槽的加深,通孔底部的最大y轴应力、通孔底部互连的最大静水应力先减小后增加,说明通孔沟槽并不是越深越好.所以,通孔沟槽有助于提高互连SIV可靠性,但为了最优化,需控制过刻蚀和通孔离子溅射清洗工艺波动造成的通孔沟槽深度变化幅度.

图3 通孔高度对通孔底部最大y轴应力、通孔底部互连M1最大静水应力和最大等效塑性应变的影响Fig.3 Effects of via height on the maximum y-axis stress at via bottom,as well as the maximun hydrostatic stress and equivalent plastic strain in M1

图4 通孔沟槽深度对通孔底部最大y轴应力、通孔底部互连M1最大静水应力和最大等效塑性应变的影响Fig.4 Effects of via gouging depth on the maximum y-axis stress at via bottom,as well as the maximum hydrostatic stress and equivalent plastic strain in M

图5给出了Cu互连通孔底部阻挡层厚度变化对最大y轴应力、通孔底部互连的最大静水应力和最大等效塑性应变的影响.通孔底部阻挡层厚度对互连应力特性的影响并不像前面两种通孔微结构那样具有一致性.对于通孔底部最大的y轴应力,较薄的互连通孔底部阻挡层厚度具有较小的最大y轴应力值,而随着通孔底部阻挡层厚度的增加,最大y轴应力先增加后稍微下降(如图5(a)所示).对于通孔底部互连的最大静水应力,较薄的互连通孔底部阻挡层厚度具有较大的静水应力值,而随着通孔底部阻挡层厚度的增加,最大静水应力先减小后稍微增大(如图5(b)所示).通孔底部阻挡层对互连最大塑性应变值的影响并不是很大,随着通孔底部阻挡层厚度的增加,通孔底部互连的最大等效塑性应变值只是轻微的减小(如图5(c)所示).综上所述,互连通孔底部阻挡层厚度变化对互连通孔SIV性能和通孔底部互连SIV性能的影响具有矛盾性,需要折中考虑.如果单纯为了提高通孔的SIV可靠性,那么通孔底部阻挡层厚度就需控制在较薄的范围,但它会使通孔底部互连中具有较大的静水应力;相反,如果单纯考虑通孔底部互连的SIV性能,那么通孔底部阻挡层厚度需控制在较厚范围,但它会使通孔底部具有较大的y轴应力.

图5 通孔底部阻挡层厚度对最大y轴应力、通孔底部互连M1的最大静水应力和最大等效塑性应变的影响Fig.5 Effects of barrier layer thickness in via bottom on the maximum y-axis stress at via bottom,as well as the maximum hydrostatic stress and equivalent plastic strain in M1

3 结语

文中采用有限元分析方法模拟了互连通孔和通孔阻挡层形成工艺波动引起的通孔微结构效应对Cu/低-k互连SIV性能的影响.结果表明,对于通孔高度的变化,SIV对大高宽比的通孔结构很敏感,高宽比小的互连通孔结构比高宽比大的互连通孔结构具有更好的SIV可靠性.通孔沟槽可以有效提高互连SIV可靠性,但需要控制过刻蚀和通孔离子溅射清洗工艺波动造成的通孔沟槽深度变化幅度.通孔底部阻挡层厚度对互连SIV的性能具有矛盾性,需要折中考虑.文中从工艺波动性的角度,研究了通孔微结构对Cu/低-k互连SIV特性的影响,为评价互连靠性提供了很好的参考.

[1] Ogawa E T,McPherson J W,Rosal J A,et al.Stress-induced voiding under vias connected to wide Cu metal leads[C]∥Proceedings of the 40th Annual International Reliability Physics Symposium(IRPS2002).Dallas:IEEE,2002:312-321.

[2] Gan D,Wang G,Ho P S.Effects of dielectric material and linewidth on thermal stress of Cu line structures[C]∥Proceeding of the IEEE 2002 International Interconnect Technology Conference(IITC2002).SanFrancisco: IEEE,2002:271-273.

[3] Lim Y K,Lim Y H,Kamat N R,et al.Stress-induced voiding beneath vias with wide copper metal leads[C]∥Proceeding of the 11th International Symposium on the Physical and Failure Analysis of Intergrated Circuits(IPFA2004).Taipei:IEEE,2004:103-106.

[4] Shen Y L,Ramamurty U.Constitutive response of passivated copper films to thermal cycling[J].Journal of Applied Physics,2003,93(3):1806-1812.

[5] Von Glasow A,Fischer A H,Hierlermann M,et al.Geometrical aspects of stress-induced voiding in Cu interco nnects[C]∥Proceedings of Advanced Metallization Conference (AMC2002).Tokyo:Materials Research Society,2002: 161-167.

[6] Shen Yu-lin.On the elastic assumption for copper lines in interconnect stress modeling[J].IEEE Transactions on Device and Materials Reliability,2008,8(3):600-607.

[7] Lin Xiao-ling,Hou Tong-xian,Zhang Xiao-wen,et al.Thermal stress characteristics of Cu interconnects using air-gap[C]∥Proceedings of ICEPT-HDP 2010.Xi'an,China:IEEE,2010:34-35.

[8] Wang R C J,Chen L D,Yen P C,et al.Interfacial stress characterization for stress-induced voiding in Cu/low-k interconnects[C]∥Proceeding of the 12th International Symposium on the Physical and Failure Analysis (IPFA2005).Singapore:IEEE,2005:96-99.

[9] Li B,Sullivan T D,LEE T C,et al.Reliability challenges for copper interconnect[J].Microelectronics Reliability,2004,44(3):365-380.

[10] Tsai M H,Tsai W J,Shue S L,et al Reliability of dualdamascene Cu metallization[C]∥Proceeding of the IEEE 2000 International Interconnect Technology Conference(IITC 2000).San Francisco:IEEE,2000:214-216.

[11] Hu C K,Rosenberg R,Lee K Y.Electromigration path in Cu thin-film lines[J].Applied Physics Letters,1999,74 (20):2945-2947.

[12] Hau-Riege C S.An introduction to Cu electromigration[J].Microelectronics Reliability,2004,44(2):195-205.