纳米CMOS工艺下互连测试结构的设计与实现

2010-09-05张永红上海第二工业大学实验与实训中心上海201209

张永红,毕 烨(上海第二工业大学实验与实训中心,上海201209)

纳米CMOS工艺下互连测试结构的设计与实现

张永红,毕 烨

(上海第二工业大学实验与实训中心,上海201209)

集成电路制造技术进入纳米时代后,互连线制造过程中出现的半导体材料和工艺物理特性变异已不是仅靠晶圆厂或掩模厂采用的分辨率增强技术所能矫正。结合目前后段制程的工艺特点,设计了平行板电容、层跃平行板电容、叉指型电容、叉指型通孔链电阻等提取标准互连线性能参数的无源测试结构套件,并采用高阶Perl语言将其自动实现,极大地提高了测试结构设计和实现的效率。在此基础上,为建立可制造性设计的物理设计规则和进一步研发纳米工艺中互连线特有的各种新物理现象奠定了基础。

互连线;标准互连线性能参数;测试结构设计;自动实现

0 引言

在集成电路互连线制造过程中,不断交替重复着光刻、刻蚀、淀积、化学机械平坦化等工艺步骤,而这些工艺步骤中存在的一些效应或缺陷又是引起集成电路成品率下降的主要原因[1]。由于超大规模集成电路制造的数量是相当大的,任何一次制造过程中都会有工艺波动的情形出现,因此想要真正地分析一个工艺,必须达到一定数量的统计[2]。由于互连线的制造效应是目前影响集成电路可制造性的主要因素,因此当工艺迅速发展和进步时,需要迅速且准确地知道目前后段工艺的制造状况,并且利用此信息来建立准确的Corner模型。

如何迅速产生所需要的大量正确的互连测试结构,便是大部分人所面临的问题。由于所需的测试结构有许多不同的大小和复杂的内容,因此如果采用传统的请版图工程师完成的方法,是相当没有效率且容易出错的。 在本文中,设计了提取标准互连线性能参数SIPPs (Standard Interconnect Performance Parameters)的无源互连测试结构套件,并结合版图层信息文件和测试结构输入文件,采用高阶Perl语言将其自动实现为CIF格式版图文件,经Cadence版图软件转换成晶圆厂广泛采用的GDSII格式文件并通过电学连接的检查,从而可以快速地缩短测试结构设计和实现的时间,更快地达到更有效率的产能,并具有一定的稳定性和正确性。

1 标准互连线性能参数 (SIPPs)

标准互连线性能参数SIPPs标准是由许多产业界领先的公司参与的一个国际性的组织——Silicon Integration Initiative于1998年制订出来的。它旨在给超大规模集成电路后段工艺金属互连线的效能提供一个标准的方法。在SIPPs里,几乎把所有影响超大规模集成电路后段工艺的因素都提供了一个参数化的表示方法,简化了过于繁杂的因素。

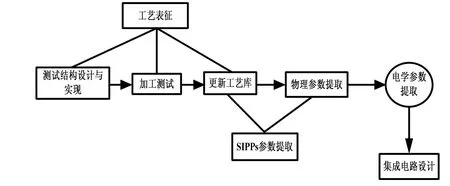

当通过测试结构的测量得到了标准的SIPPs的格式后,晶圆厂使用产业界精准的Field Solver工具建立一个所有各种可能情形的集合,把计算出来的结果储存在数据库当中[3]。设计者在得到这样的数据库之后,利用EDA(Electronic Design Automation)工具从自己的设计中把相关的寄生电性抽取出来,以此预估设计的延时,如图1所示。目前在产业界的EDA工具中,多数是使用这样的方法,比较常用的有SynopsysStar-RCXT和Mentor xCalibre[4-5]。

图1 设计流程中使用SIPPs[6]Fig.1 SIPPs in design flow

设计的测试结构中,针对的目标是表征集成电路后段工艺的金属互连线。这些金属互连线,业界最常用的方法就是将其参数化。SIPPs参数就是金属互连线参数化的一种形式。这些参数代表了大部分金属互连线的特性。它们可以分为两大类:一类是不易变动的参数,主要是关于氮化物和通孔半径的,分别是氮化物A的厚度、氮化物A介电常数、氮化物B厚度、氮化物B介电常数、通孔半径等。在进行RC抽取的时候,不容易变动的参数对于结果的影响并没有像另一类参数那么明显。另一类容易变动的参数是7个SIPPs的必要参数,分别是低K物质A厚度、低K物质A介电常数、通孔电阻、互连线厚度、方块电阻、特征尺寸偏差(CD (Critical Dimension) bias)、低K物质B介电常数。这些参数用来估算超大规模集成电路芯片制造时的工艺波动。除了跟介电常数有关的两个参数外,其它五个参数都会有大于百分之十以上的变动。这对于Corner分析将是非常大的挑战。下面是常见的SIPPs参数,如图2所示。

图2 SIPPs参数与互连线示意图Fig.2 SIPPs parameters and copper interconnect

2 几种主要测试结构的设计

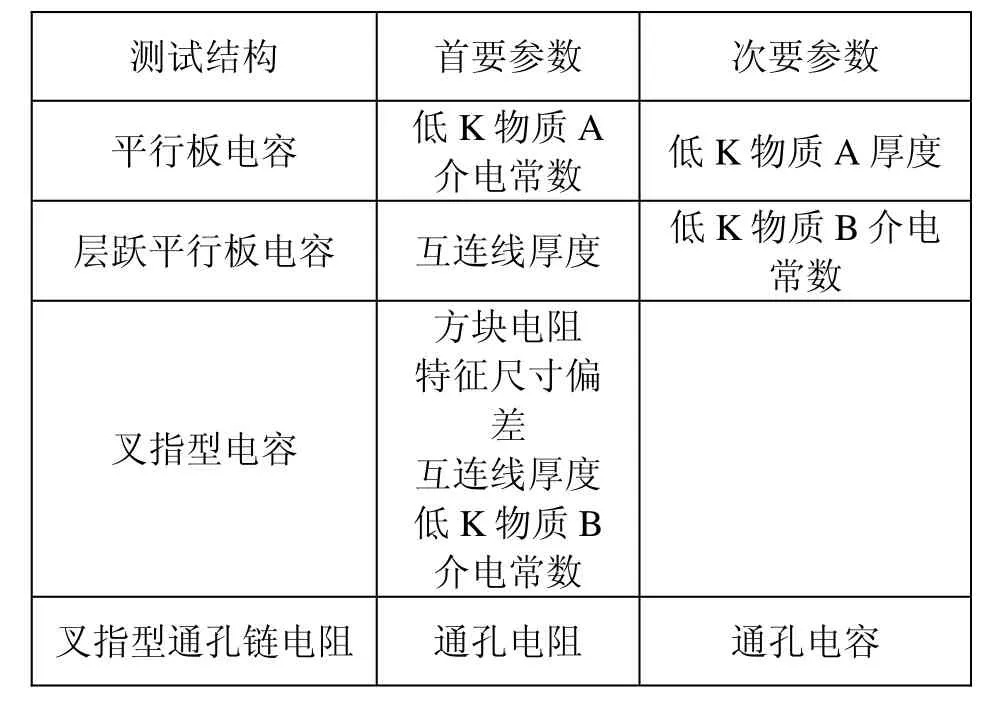

为了提取出如表1所示的SIPPs参数,依次设计了平行板电容测试结构、层跃平行板电容测试结构、叉指型电容测试结构和叉指型通孔链电阻测试结构。设计的方法是利用所谓的敏感度 (Sensitivity):在测试结构设计的过程中,让特定参数的效应加大,而非测试的参数的敏感效应降低。这样所设计的测试结构针对某一个参数的敏感度相当高,以便达到设计的目标。

平行板电容测试结构,顾名思义就是利用两块平板,分别给予不同的电位,而在这两块平行板中间便会存在一个电容,这个电容就是此结构想要测量出来并加以分析的电性。它所代表的意义是上面必要的SIPPs参数中的低K物质A厚度和低K物质A介电常数。也就是说,这一测试结构所要观察的是金属层中间的绝缘体的特性,而对于该绝缘体层的特性影响最多的就是该层的厚度和该层的介电常数。

表1 SIPPs与测试结构对应表Tab.1 SIPPs and corresponding test structures

在设计层跃平行板电容测试结构的时候,忽略了中间一层金属。大体上,跟平行板电容测试结构是相近的,唯一的不同就是跳过了一层金属。例如,若是针对金属层2所设计的测试结构,那么,得到的结构中,只有除了金属层2以外的其它层的平行板。利用这个测试结构,结合下面的叉指型电容测试结构,可以取得SIPPs参数中的互连线厚度参数。

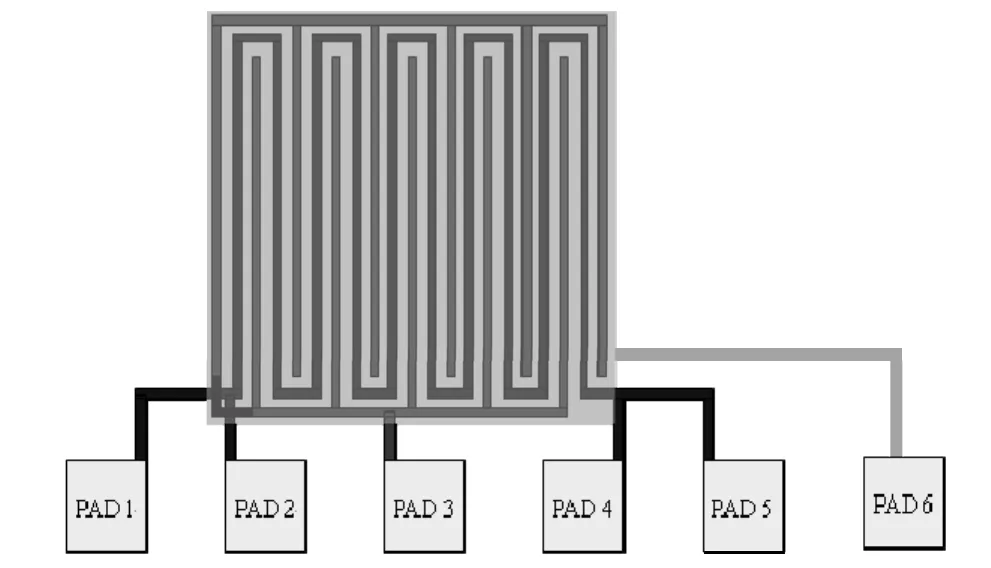

叉指型电容测试结构是一种比较特殊的测试结构,可以用来测量出两种电性,分别是电容和电阻。这样能尽量减少测试结构所占用的面积,又不失去所需要的统计资料,使得制造成本相对降低,而且由于利用该结构,同时测量出电阻和电容,它们的工艺波动是一样的,更有利于提高Corner模型的精确性。图3是叉指型电容测试结构简图。主要的测试结构摆在层 i和层( i+1)。左下角是连接上下两个齿型互连线的部分,为了避免短路现象的产生,两者之间利用通孔拉到另外一层金属进行连接。对于整体结构来说,由于该部分在整体中所占的比例非常低,可以将它对SIPPs参数造成的误差影响忽略。除了这两个金属层以外的金属层都先摆上一个金属平板。

图3 叉指型电容测试结构示意图Fig.3 Comb Meander test structure

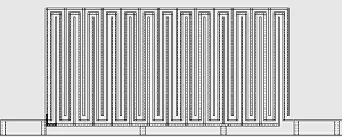

这一测试结构需要占用到6个PAD的宽度,测量出来的电阻值是该测试结构中间的蜿蜒曲折部分。该结构是一个Kelvin的4点电阻测试结构。通过在PAD1和PAD5中间灌入一个电流,在PAD2和PAD4测量到一个电压,利用欧姆定律可以得到该部分的电阻值,进而得到SIPPs中的方块电阻。另外得到的两个电容值,一个存在于上下齿状互连线和中间的蜿蜒曲折互连线之间,另一个存在于该层互连线与上层平行金属板之间。这两个电容可以求得SIPPs参数中的互连线厚度、特征尺寸偏差、低K物质B介电常数。在测量时,一种方式需要将PAD1,PAD2, PAD3,PAD4,PAD5连接到感应端,PAD6连接到驱动端;另一种方式需要将PAD1,PAD2,PAD4,PAD5连接到感应端,PAD3,PAD6连接到驱动端。图4为其自动产生出的结构版图的一部分。

图4 叉指型电容测试结构版图结果Fig.4 Layout of Comb Meander test structure

叉指型通孔链电阻测试结构是另一种测试结构,它和叉指型电容测试结构不同的地方是,图3中的蜿蜒曲折互连线,被换成了需要测量的通孔链,如图5所示。在有限的空间上尽量将蜿蜒曲折的互连线换成测量通孔电阻的通孔链,这样,当使用原来的Kelvin 4点测量的时候,就可以得到一个有许多个通孔串连起来的电阻值。因此可以用此方法得到SIPPs中的通孔电阻,也可以使用这一个测试结构测量得到一个电容,这个电容可以达到之前叉指型电容测试结构所可以推导出来SIPPs参数的互连线厚度、特征尺寸偏差。图6是自动产生出的测试结构版图的一部分。

图5 叉指型通孔链电阻测试结构示意图Fig.5 Comb Meander for Via Resistance test structure

图6 叉指型通孔链电阻测试结构部分版图结果Fig.6 Layout of Comb Meander for Via Resistance test structure

3 测试结构的实现

整个测试结构的实现流程如图7所示

图7 测试结构产生流程图Fig.7 test structure realize Flow chart

首先需要准备相关的版图层信息文件,这样才可以知道每一层金属在版图中所对应的GDSII层数字,进而在使用Perl语言编程时产生正确的版图层;另外一个文件是所要产生的测试结构的信息,包括所要产生的测试结构所在的版图层名称和互连线宽度、间距的大小,这部分信息在设计测试结构时就需要根据结构所要提取的参数设计出来;然后利用Perl语言编辑器编写以下的程序,自动产生出所有的测试结构。

#!/usr/bin/perl

if ($#ARGV != 2) {

print "usage: perl PPC.pl struct_file layer_map out_cif_dir "; exit; }

print "usage OK ";

# Some fixed key words

$struct_key_word = "S65";

$parallel_plate_type = "pp3D";

$comb_meander_type = "comb3D";

$via_resistance_type = "via";

# Declare a CIF file name's prefix

$cif_file_prefix = "dummy";

# Let Perl's memeory start to manage

# the input arguments

$struct_file = $ARGV[0];

$layer_map = $ARGV[1];

$out_cif_dir = $ARGV[2];

# An overall CIF output file dir is good

system ("mkdir -p -m 777 ./$out_cif_dir");

# Initialize some indices and parameters

$total_gds_layer_count = 0;

$total_metal_layer_count = 0;

$width = 0.0;

$spacing = 0.0;

测试结构实现的过程中,采用的平台是Sun的FireV490机器,操作系统是SunOS 5.8,Perl 语言版本为v5.6.0,Cadence IC的版本为5.10.41。在整个试验中,按照设计规则(0.065um Logic 1P8M Salicide 1.0(G) or 1.2(LL)/1.8/2.5.or 3.3V Design Rule, Version 1.0)的规定,产生了目标为抽取出八层互连线SIPPs参数的测试结构,对于每一层互连线都设计了16种不同比例的线宽和间距,共产生了152个测试结构,以此估算执行完整的流程所耗费的时间和资源以及得到的结果。

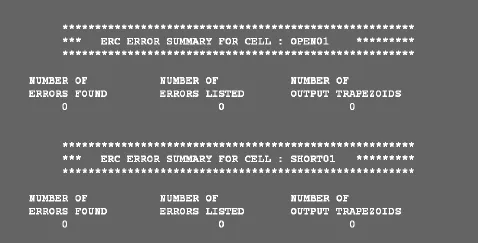

首先读入所有测试结构文件并产生相应的CIF格式文件,一共花了50秒的CPU时间。接着将CIF文件转成Cadence的DFII格式的版图文件并读入,一共花费了15分42秒。接下来将所有的测试线放到同一个单元中,再一次进行所有测试结构的电学连接检查。其检查结果如图8所示。从图中可以看到,无论短路或者开路的检查,都是通过的。最后将所有测试结构转换成晶圆厂适用的GDSII格式。最终所产生的GDSII文件大小是216.4M,第二阶段的这个过程共花费了18分6秒的时间。

图8 测试结构电学连接检查结果Fig.8 Electric Rule Check result of test structures

4 结束语

我们设计了一套完整的测试结构套件并利用高阶语言自动将其实现。该套件主要包括平行板电容测试结构、层跃平行板电容测试结构、叉指型电容测试结构和叉指型通孔链电阻测试结构以及它们的误差消除结构。将几种类型的测试结构和版图中各层对应的GDSII名称分别编写成输入文件形式,然后利用高阶Perl语言自动产生出来。利用高阶语言产生测试结构的方法,使得在测试结构产生的过程中,只需要花时间编写输入文件,就可以在短时间内,实现完整的测试结构,减少由于人力介入产生的错误,提高了测试结构实现的效率。

设计的该测试结构套件主要针对目前纳米工艺技术节点,得到该工艺下的SIPPs,对目前阶段的工艺水平进行准确的评估,以建立工艺的Corner模型和提供可制造性物理设计规则、互连线电阻非线性SPICE模型等。该测试结构的实现方法达到了测试结构对工艺节点的自动跟踪功能,在技术节点的发展过程中,只要将测试结构的输入文件根据工艺节点进行修改,便可以评估该技术节点下后段工艺性能参数。

[1] GEFFKEN R M, MOTSI F W T. International technology roadmap for semiconductors[EB/OL].(2003-12)[2009-07-29] http://www.itrs.net/ Links/2003ITRS/Interconnect2003.pdf.

[2] CHENG Y H. A glance of technology efforts for design-for-manufacturing in nano-scale CMOS processes[J]. Science in China, 2008, 51(6): 807-818.

[3] CHANG K J, LYU D C H. Accurate 3-D capacitance test and characterization of dummy metal fills to achieve design for manufacturability [C]// Proceeding of 10th CMP-MIC Conf., USA: Fremont ,2005.

[4] WILSON J, WALTER N G. Dracula reference version 4.9 [R]. USA, San Jose, 2004.

[5] JOHN K, CARLO G, ANDREZJ J. Design data translator’s reference version 5.1.41 [R]. USA, San Jose, 2004.

[6] ERTUGRUL D, JUDITH M. SIPPs standard interconnect performance parameters [EB/OL]. (2003-09-22)[2009-07-29] http://www.ece.cmu.edu/ ~chraska/tau99/Talks/don_cott.pdf.

Interconnect Test Structures Design and Realized in Nano CMOS Technology

ZHANG Yong-hong, BI Ye

(Practicing and Training Center, Shanghai Second Polytechnic University, Shanghai 201209,P.R.China)

As manufacturing technology of integrate circuit into the nanometer era, the variations of semiconductor materials and processes physical properties during interconnect manufacturing can’t be corrected only by previous resolution enhancement techniques of fab or mask shop. Designed Parallel Plate, Layer-skipping Parallel Plate, Comb Meander, Comb Meander for via Resistance inactive test structure kits to extract Standard Interconnect Performance Parameters SIPPs, and automatically realized them with High-level Perl language. Greatly improved the efficiency of test structure’s design and realized. Lay the foundations for formulation of DFM physical design rules and further research interconnection statistical models under nano technology with more unique physical phenomena.

interconnect; SIPPs; test structures design; automatically realized

TN405

A

1001-4543(2010)01-0016-06

2009-09-07;

2009-12-11

张永红(1982-),女,河南商丘人,硕士,主要研究方向为大规模与超大规模集成电路设计,电子邮件:yhzhang@pc.sspu.cn。

上海第二工业大学校基金(No.QD209012)