面向芯粒间互连的低功耗发射机驱动设计*

2024-04-23任博琳肖立权齐星云庞征斌徐佳庆

任博琳,肖立权,齐星云,张 庚,王 强,罗 章,庞征斌,徐佳庆

(国防科技大学计算机学院,湖南 长沙 410073)

1 引言

随着半导体制造工艺的提升,芯片性能在摩尔定律的指导下不断提高,但由于器件尺寸已经开始逼近物理极限,半导体产业进入了“后摩尔时代”。芯片制造成本随着工艺的提升越来越高,半导体产业一直在寻找解决发展步伐变慢的方法[1]。片上系统SoC(System on Chip)的发展已经遇到瓶颈[2]。单个芯片上集成过多的单元使得芯片面积急剧增大,导致芯片良品率降低,进而增加了成本。芯粒(Chiplet)技术是行业认为延缓摩尔定律的解决方案之一,受到了行业的普遍重视[3]。

Intel、AMD、微软、高通公司、三星和台积电等公司一起建立了一个小芯片互连标准UCIe(Universal Chiplet Interconnect express)。UCIe是一种开放的、支持多协议的封装内互连标准,用于连接同一封装上的多个芯片。UCIe制定了Chiplet之间高速低功耗互连的标准。针对UCIe提出的低功耗、低误码率的互连标准,本文设计了一种低功耗的发射机驱动[4]。

面向UCIe协议提出的芯粒间互连标准,本文介绍了一种采用2-tap前馈均衡的低功耗发射机驱动设计。通过对比分析电压模驱动器SST(Source-Series Terminated)和电流模驱动器CML(Current Mode Logic),电压模驱动器的功耗为电流模驱动器的1/4,采用SST电压模驱动器可以显著降低发射机的整体功耗。发射机采用2-tap的可调前馈均衡器,芯粒间互连由于通信距离短,信道衰减程度小,降低了整体发射机的功耗。根据不同信道的衰减,调整均衡系数,可以降低信号通过信道后的码间串扰。

本文工作主要包括以下4个方面:

(1)分析电流模驱动器与电压模驱动器的电路结构,并对两者功耗进行对比分析,得知电压模驱动器具有功耗低、线性度好等优势,因此本文设计采用电压模驱动器。

(2) 基于电压模驱动器实现2-tap前馈均衡,分析单端传输中SST电压模驱动器实现前馈均衡的工作原理,即通过调整延迟抽头切片(slice)的数量来调整去加重后的电压差,从而改变均衡强度,并对电路进行功耗分析。

(3) 设计了一种基于SST电压模驱动器的低功耗可调均衡发射机驱动,最大均衡强度为-3.7 dB,仿真功耗仅为4.0 mW。根据不同信道衰减程度选取合适的均衡强度,降低信号的码间干扰。

(4) 测量真实信道参数,不同的数据速率对应不同的信道衰减。根据真实信道参数,测试发射机性能以及不同电源电压下发射机的眼图及功耗。

2 发射机结构

2.1 总体结构

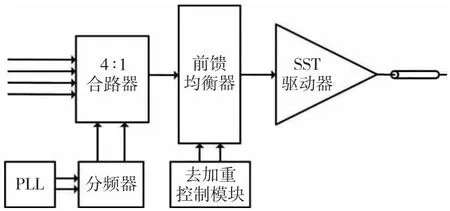

发射机主要架构包括4∶1并转串模块、去加重控制模块、驱动模块及时钟通路。4∶1并转串模块将4路输入信号合成1路高速的32 Gbps信号。时钟由PLL(Phase Lock Loop)产生并通过分频电路将时钟分频后给各个模块。去加重控制模块是通过控制主抽头和延迟抽头驱动器slice的数量来控制输出信号的去加重程度。

Figure 1 Overall structure of transmitter

2.2 驱动器

驱动器是整个发射机功耗最大的部分,常用的2种驱动器如图2和图3所示,图2为电流模驱动器CML[5],图3为电压模驱动器SST[6]。下面分别对电流模驱动器和电压模驱动器的功耗进行分析。

Figure 2 Current mode driver

Figure 3 Voltage mode driver

在电流模驱动器(CML)传输信号的过程中,尾电流为整个电路提供恒定的电流,M1、M2的栅极分别是信号的输入端,M1和M2的尺寸尽量选择大尺寸,输出阻抗近似为负载电阻R。电阻R的阻值为50 Ω,以实现信道的阻抗匹配,降低信道对信号的反射和衰减,当输入信号Vin_n为低电平,Vin_p为高电平时,晶体管M1导通,晶体管M2截止,整个电路的电流如式(1)和式(2)所示:

(1)

(2)

在电压模驱动电路(SST)传输信号的过程中,M1与M2的栅极作为信号Vin_p的输入端,M3与M4的栅极作为信号Vin_n的输入端,信号传输过程中,当输入为高电平时,NMOS管导通,当输入为低电平时,PMOS管导通。设计过程中,NMOS管与PMOS管尺寸应匹配,以保证信号在传输过程中保持稳定。CMOS管导通电阻与串联电阻之和应为50 Ω,以实现与信道的阻抗匹配。当Vin_p为高电平,Vin_n为低电平时,M2、M3导通,整个电路的工作电流为式(3):

I3=I

(3)

通过上面的分析可知,电流模驱动器在工作时,负载中流过的电流为尾电流的1/4,其中3/4的电流被晶体管消耗了。反观电压模驱动电路,电流的利用效率高,输出相同的电压摆幅的情况下,电流模驱动器要消耗4倍的电流。因此,电流模驱动电路的功耗是电压模驱动电路的4倍。UCIe协议中要求芯粒间互连要尽可能地降低功耗,电压模驱动相较于电流模驱动具有功耗低、线性度好等优点,因此本文采用电压模驱动电路,以达到降低功耗的目的。

2.3 前馈均衡

信号在传输过程中,由于信道的非理想性,会受到串扰、反射和噪声等诸多因素干扰,导致信号产生码间干扰ISI(InterSymbol Interference)[7]。为了消除码间干扰,需要在发射端和接收端采用相应的均衡技术,以补偿或抵消信道的衰减。常用的均衡器有前馈均衡器FFE(FeedForward Equalizer)、判决反馈均衡器(Decision Feedback Equalizer)和连续时间线性均衡器(Continuous Time Linear Equalizer)[8]。

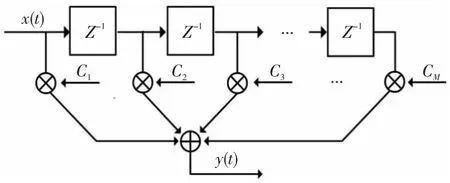

在发射端常用的是前馈均衡器。前馈均衡器的原理图如图4所示,主要由延时单元、乘法单元和加法单元组成。数据通过延迟单元后,分为前抽头、主抽头和后抽头,延迟的数据乘上不同的抽头系数,最后将数据进行叠加。前馈均衡技术主要应用于发射端,该技术可以降低信号前后的干扰,但是由于抽头个数不是无限的,干扰无法完全消除。前馈均衡器(FFE)有2种实现方式。一种是增加信号高频分量来抵消或降低信道对高频信号的衰减,这种方式也被称为预加重;另一种是降低低频分量,确保信号通过信道后的完整性,也被称为去加重。

Figure 4 Principle block diagram of feedforward equalizer

UCIe协议中建议发送端速率在24 Gbps和32 Gbps时,发送端采用前馈均衡的方式,均衡强度为-2.2 dB(±0.5 dB)。当速率较低时,由于信道距离短,不进行发送端均衡,从而降低功耗。

3 电路设计与功耗分析

3.1 可调前馈均衡器总体结构

根据UCIe协议提出的芯粒间互连标准,速率在32 Gbps时,均衡强度为-2.2 dB(±0.5 dB)。本文在设计前馈均衡器时,要求均衡强度至少能够达到-2.7 dB。该驱动器设计的最大均衡强度为-3.7 dB。

前馈均衡器可分为去加重和预加重2种。为了实现低功耗,本文设计采用的是去加重的前馈均衡器,通过调整各个抽头slice的数量,来调整抽头系数,从而实现不同的均衡强度。可调前馈均衡器总体结构如图5所示。

Figure 5 Overall structure of adjustable feedforward equalizer

3.2 可调前馈均衡器设计与功耗分析

SST电压模驱动器主要包括上拉支路和下拉支路,上拉电路由PMOS管和串联电阻组成,下拉电路由NMOS管和串联电阻组成。在设计电路的过程中,使得串联电阻的阻值相等,PMOS管和NMOS管的数量保持一致,方便版图设计。PMOS管和NMOS管的尺寸要匹配,使得信号在传输过程中上下支路的阻抗相等[9]。一个SST电路称为一个slice,其中,单个slice的输出阻抗为N×R,N为SST电压模驱动器的总个数,驱动器之间都是并联的关系;R=50 Ω,为信道的特征阻抗。总的输出阻抗Rout如式(4)所示:

(4)

在设计单个slice时,由于输出阻抗由晶体管的导通电阻和串联电阻组成,随工艺、温度、电压的变化而变化。晶体管的尺寸大小的选取要经过仔细分析,串联电阻的阻值越大,整个输出阻抗受到温度等因素的影响越小。但是,若串联电阻的阻值选取过大,晶体管的尺寸也要变大才能降低晶体管的导通电阻,这样会引起较大的负载电容;同时,晶体管漏极与源极间电压Vds过小也会导致晶体管处于截止状态[10]。在选择晶体管尺寸的过程中需要考虑多个参数,最终本文设计中电路总电阻与串联电阻之比设为4∶3。

利用SST电压模驱动电路来实现FFE均衡,通过串并转换电路的信号经过一个UI的延迟单元后,分为主抽头和延迟抽头,通过控制延迟抽头接入slice的数量来控制均衡强度,在延迟抽头接入slice数量变化时,保持总体的slice数不变,从而使得输出阻抗等于传输信道的特征阻抗,实现阻抗匹配。

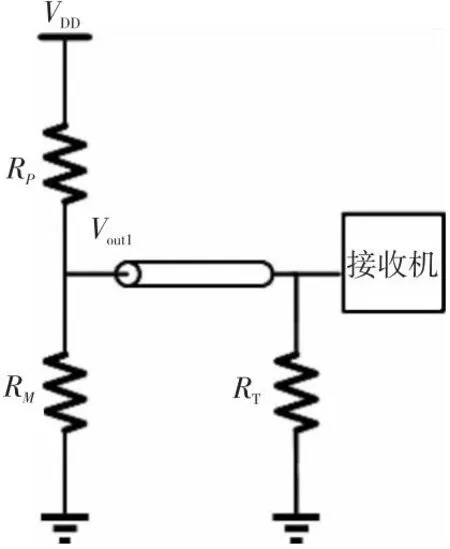

整个电路的简化原理图如图6和图7所示,其中,M表示主抽头对应的slice数,P表示延迟抽头对应的slice数,K表示slice的总数,K=M+P且K=N;RT表示接收端终端对地电阻,RM和RP分别表示主抽头和延迟抽头的等效阻抗。下面分析输入不同信号时,输出电压的变化情形:

Figure 6 Equivalent circuit 1

Figure 7 Equivalent circuit 2

当D[n]=1,D[n-1]=1时,电路等效为图6,输出电压如式(5)所示:

(5)

当D[n]=0,D[n-1]=0时,电路等效为图7,输出电压如式(6)所示:

(6)

其中,RT、RM和RP以及并联之后的电阻分别如式(7)~式(11)所示:

(7)

(8)

(9)

(10)

(11)

将式(10)和式(11)代入式(5)和式(6)后,得到去加重后的输出电压Vout1和Vout2,如式(12)和式(13)所示:

(12)

(13)

可以看出,输出的电压跟抽头的slice数量有关系,通过调整抽头接入的slice数量来实现强度均衡。去加重后输出信号的电压差Vb如式(14)所示:

(14)

当D[n]=1,D[n-1]=0时,无论是主抽头还是延迟抽头都是PMOS管导通,所有slice并联的等效电阻值等于信道的特征阻抗50 Ω,输出电压为VDD/2。当D[n]=0,D[n-1]=1时,无论是主抽头还是延迟抽头都是NMOS管导通,电路中没有电流流过,输出电压为0 V。输出信号没有去加重情况下的电压差Va如式(15)所示:

(15)

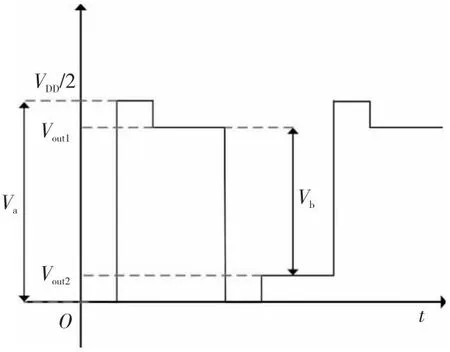

信号经过FFE均衡后的波形如图8所示,信号的摆幅为VDD/2,经过去加重后的输出电压分别为Vout1和Vout2。再通过调整延迟抽头接入slice的数量来改变Vout1和Vout2之间的电压差,接入slice的数量越多,RP的阻值越小,Vout1和Vout2之间的电压差越小,去加重的程度越大。Vout1和Vout2之间的电压差变化的步长为2/K,其中,K为slice的总数。均衡强度公式如式(16)所示:

(16)

Figure 8 Waveform of signal after FFE

本文设计可以实现3 bit 8位的均衡调节。当控制位全为1时,均衡强度最大为-3.7 dB,发射机可以控制去加重程度,以适应不同的信道衰减。

采用0.9 V电源供电时,驱动电路阻抗为50 Ω,理论电流取平均值为4.5 mA。根据式(17),计算得到除去控制电路的驱动器理论功耗为4.05 mW。由第2节推导结论可知,若采用电流模驱动,功耗为该电路的4倍,即16.2 mW。当采用0.8 V电源供电时,理论功耗为3.2 mW;当采用1 V电源供电时,理论功耗为5 mW。

(17)

4 实验与结果分析

4.1 信道传输参数

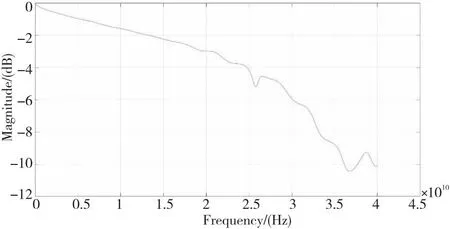

利用网络分析仪对真实21 mm短距离信道参数进行提取,得到的传输信道频率响应曲线如图9所示,发射机数据传输速率为32 Gbit/s,奈奎斯特频率为16 GHz。根据测量得到的传输信道在16 GHz下的衰减为-2.37 dB。可以看出,信号在低频处衰减较小,随着频率的升高,信道质量呈指数型降低。由于是短距离信道,信号衰减程度不大,在发射机设计时,最大的均衡强度为-3.7 dB,该发射机可以在此信道正常传输信号。

Figure 9 Frequency response curve of transmission channel

4.2 输出信号

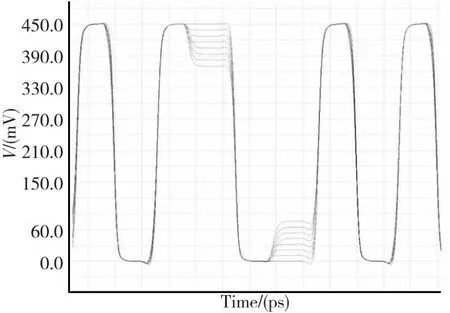

采用CMOS 28 nm工艺进行仿真验证。通过调整去加重控制电路,验证发射机电路的均衡功能。改变8种不同的去加重控制程度,所有仿真波形叠加图如图10所示,信号摆幅为电源电压的一半,即450 mV。不开启均衡和最大强度均衡后的眼图如图11所示,信号经过去加重后的幅度为291 mV,经过计算均衡强度为-3.78 dB,与理论计算的结果基本一致。

Figure 10 Waveforms under different equilibrium intensities

Figure 11 Eye map after turning on equalization

电源电压分别为0.8 V,0.9 V和1 V时,信号摆幅随着电源电压的升高而增大,不同电压下调整合适的均衡强度后,信号经过信道后的眼图如图12所示。信号在0.8 V供电时,眼高为220 mV,眼宽为27.19 ps。信号在0.9 V供电时,眼高为253 mV,眼宽为27 ps。信号在1 V供电时,眼高为282.3 mV,眼宽为26.18 ps。

Figure 12 Eye maps after enabling equalization through channels under different voltages

Figure 13 Transient currents at different voltages

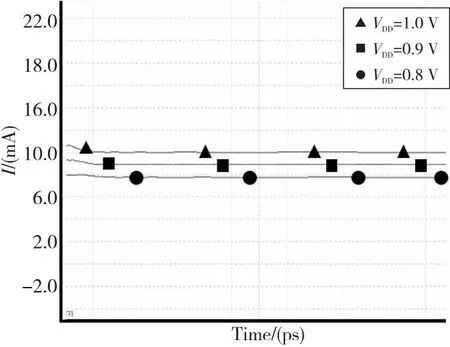

测试发射机驱动电路功耗。该电路功耗由驱动器和控制电路2部分组成。通过对电源输出电流进行积分得到平均电流值来计算功耗,如式(18)所示。通过计算可知,电源电压为0.8 V时,功耗为3.2 mW;电源电压为0.9 V时,功耗为4.0 mW;电源电压为1 V时,功耗为5.1 mW。理论功耗在不同电压下分别为3.2 mW,4.05 mW和5.0 mW,仿真结果与理论计算功耗基本相同。不同电压下的瞬态电流如图13所示。

(18)

本文与其他文献中发射机的参数对比如表1所示。可以看出,本文发射机驱动电路支持更高的传输速率且具有较低的功耗。

Table 1 Comparison of transmitter parameters between this paper and other literature

5 结束语

本文针对UCIe协议提出的芯粒间互连标准,设计并实验了面向芯粒间互连的低功耗发射机驱动,对CML电流模驱动器与SST电压模驱动器的功耗进行了分析,详细介绍了基于SST电压模驱动器实现FFE均衡的工作原理并进行了功耗分析。最后,通过提取真实信道的参数,对发射机进行了仿真验证。测试结果表明,输出信号的眼图以及均衡强度符合设计指标。在28 nm设计工艺下,最大均衡强度为-3.7 dB。0.9 V电源电压下,眼高为253 mV,眼宽为27 ps,功耗仅为4.0 mW。