全息存储中的纠错码研究综述*

2024-04-23谢长生

于 勤,吴 非,张 猛,谢长生

(1.华中科技大学武汉光电国家研究中心,湖北 武汉 430074;2.华中科技大学计算机科学与技术学院,湖北 武汉 430074)

1 引言

随着5G、物联网和人工智能等新一代信息技术的快速发展,全球产生的数据量呈爆炸式增长。在海量的数据中,并非所有的数据都会被频繁访问。根据访问频率由高至低,可以将数据分为热数据、温数据和冷数据。存储在数据中心的大部分数据是冷数据。如何长期、安全和节能地存储海量冷数据是网络信息产业领域面临的难题。

当前主流的存储技术主要有以磁盘为主的磁存储技术,以闪存为代表的电存储技术和以光盘为代表的光存储技术[1-3]。与其他存储方式相比,光存储具有节能、长期保存以及成本低廉等优点,符合当下绿色节能的主题。传统光盘采用按位存储的二维面存储方式,利用激光在光盘表面的记录点是否发生反射来实现0或1的二进制数据读取,其提高记录密度的方法是靠缩小记录点的尺寸实现的,主要有2种途径:(1)采用更小的记录光波长;(2)增大记录物镜的数值孔径。目前蓝光记录光波长已接近不可见光的范围,而数值孔径增大会引起记录信息失真的问题。另外,由于远场记录下光学系统的锐利衍射极限的存在,进一步提升传统光盘的存储密度面临严峻的挑战[4]。以多维光存储、超分辨光存储和全息光存储为代表的新型光存储技术,具有较高的理论存储容量和存储密度,未来可能在云计算、数据中心和大数据分析等领域得到应用[5,6]。全息存储以二维数据页作为读写单位,采用并行读写的方式,并通过借助多种复用技术,存储密度可达1012bit/cm3,数据转换速率可到10 GB/s[7-11]。全息存储有潜力成为现有存储介质的补充方案,尤其是在需要高容量和快速存取的应用场景中,全息存储将会表现出优异的性能和容量优势。

2 全息存储系统

与传统光盘的单光束记录方式不同,全息存储采用参考光和信号光双光束来记录数据。根据参考光与信号光是否共轴,可以将全息存储划分为离轴全息存储和同轴全息存储。离轴全息存储系统结构相对复杂,采用角度复用和静态读写模式,会带来记录介质的部分浪费。同轴全息存储系统结构紧凑,采用位移复用和动态读写模式,记录介质浪费空间少;而且同轴全息存储能和现有的伺服系统匹配,具有更强的兼容性和抗震动性,是全息存储实用化和产品化的重要研究方向[12]。

数据在送至信道传输之前,需要经过纠错编码器和调制编码器。纠错编码的作用是保证数据在记录或信道中传输的可靠性。调制编码对信号进行转换以匹配物理记录介质的特性,性能优异的调制方式不仅能够提升数据存储密度,还能抵抗信道中噪声的干扰。根据调制方式的不同,可以将全息存储系统分为振幅型全息存储与相位型全息存储。振幅型调制编码效率较低,难以突破1的限制,浪费了部分光学信息,无法完全发挥全息存储高密度的优势。相位型编码能够有效地提高编码率,对于M阶相位调制编码而言,每个相位符号表示lbM比特,4阶相位型编码的编码率为2,进一步提高了全息存储密度和容量。

相位调制的阶数越高,每个相位符号表示的比特数目越多,存储密度越高,但是各存储单元状态之间的间距也会越小,抵抗噪声的能力越弱。图1展示了相位型同轴全息存储系统的记录、读取和重建过程。针对相位型同轴全息存储系统已有多种相位调制方法被提出[13-15]。这些编码方式虽然能在一定程度上提升编码效率,但是编码率仍然较低,且解码方式相对复杂且不稳定。另外,相位型全息存储系统目前还面临数据读取过程中需进行相位重建这一严峻挑战。根据相位恢复方法中是否包含干涉操作,可以将相位重建方法分为干涉法[16-21]和非干涉法[22-24]。由于干涉强度易受到环境干扰,导致系统不稳定,因此非干涉法是相位重建的理想选择。迭代傅里叶变换IFT(Iterative Fourier Transform)算法是一种无干涉相位恢复方法,该方法的光路系统简单,相位重建结果稳定,提高了相位重建的精度和速度[25],IFT算法是一种误差逼近算法,重建相位与原始记录相位存在些许偏差。由于重建算法的限制以及信道中多种复杂噪声的干扰[26],相位型全息存储系统需要采用具有强纠错能力的纠错码ECC(Error Correction Code)以保证数据可靠性。

Figure 1 Recording,reading and reconstruction processes of holographic storage system

3 全息存储中的纠错码研究现状

ECC通过在纠错编码时增加冗余校验数据,建立信息数据与校验数据之间的互相制约关系并用于译码纠错,使误码率BER(Bit Error Rate)降低到可接受的水平,从而提高存储系统的可靠性[27,28]。BER定义为一个码字经过ECC纠正后的比特错误数与该码字长度之比。虽然从存储系统获取的原始数据可能包含较多的错误比特,但通过有效地设计ECC可以确保以可容忍的较低错误级别提供给用户。目前应用于全息存储系统的纠错码有多种,其中LDPC(Low-Density Parity-Check)码应用最为广泛,主要原因是LDPC码适合于全息存储系统纠错,不仅是因为LDPC码接近香农极限的纠错性能和可并行的译码方式,而且信道/数据页中噪声分布的先验信息可以用来辅助设计具有强纠错能力的LDPC码。目前关于全息存储的纠错码研究主要包括以下几个方面。

3.1 二维/三维ECC技术

与磁记录或传统的光存储通道不同,全息数据存储通道具有三维结构,因为它在空间上是二维数组,在时间上是数据页流。 与一维突发错误模式(本质上是一串连续的错误)不同,二维突发错误以依赖于存储通道的特定几何形状的簇的形式出现。 Imai[29]引入了二维循环码,用于纠正多次出现的单个突发错误。在不改变编码率或者最小距离的条件下,Blahut[30]提出了改进的二维BCH(Bose、Ray- Chaudhuri 与Hocquenghem)码。Madhusudhana等[31]对文献[30]的二维BCH码译码算法进行了扩展,用于突发纠错,该方案能够纠正特定形状的突发错误,但不能处理多重不相交的突发错误。 Roy等[32]构建了原生二进制二维循环码,能够使用频域技术纠正多次出现的二维错误。该方案中的每个错误形状的起始位置都是使用一种基于公共零集的新型解码算法确定的,并且提出了一种通用的编码结构。与传统的二维BCH码相比,其具有更高的编码率。里德-所罗门RS(Reed-Solomon)码是最常见的纠错码之一,可以有效地纠正信道中的突发错误,并可以应用于不同的维度。针对全息数据存储信道,Hwang等[33]提出了迭代体纠错方案RSVC(Reed-Solomon Volumetric Code),通过2个连续的编码器(Product ECC和Page ECC)对严重退化的数据页进行纠错。相比一维RS和二维RS码,RSVC具有更好的误差控制性能。进一步,Hwang 等[34,35]利用压缩的ECC奇偶校验符号进行迭代译码,可以有效地进行纠错。实验结果显示,该方案具有与传统ECC相当的性能,但具有更高的编码率和较低的编码开销,实现了编码率与ECC性能之间的良好权衡。Gu等[36]通过充分利用全息存储信道中误差模式的先验信息,提出了一种基于匹配交织的全息数据存储三维纠错方案。该方案结合了三维纠错方案和匹配交错方案的优点,使误差分布更加均匀,实现了数据的三维迭代译码,有效降低了BER。基于空间耦合低密度奇偶校验SC-LDPC(Spatially Coupled Low-Density Parity-Check)码的编码器具有通用性,Ishii等[37]讨论了SC-LDPC码对差分调制码的适用性以及再现数据的可纠错特性,实验结果显示,SC-LDPC码纠错容忍度可达到0.08。

3.2 与交织/均衡/检测技术相结合的ECC技术

由于成像光学器件的限制和对准偏差等因素造成的二维符号间干扰,会导致全息存储系统的信噪比SNR(Signal-to-Noise Ratio)降低,BER增加。一些有效的数据处理方案能够使存储的数据可靠地检索。数据预处理和数据后处理是常见的数据处理方法。交织编码将一个大面积的突发错误分散成随机错误,起到数据预处理的作用。均衡/检测能够降低符号间干扰的影响,是常见的数据后处理方法。将纠错码与交织/均衡/检测技术相结合能够获得更好的纠错性能。 通过分析由透镜像差和准直误差引起的相关误差模式,并将其作为先验信息,Chou等[38]提出了一种将二维交织码与RS纠错码相结合的方案,以降低二维错误,并从BER和存储容量2个角度分析了交织码和ECC的性能。Pansatiankul等[39]提出了基于RS码的三维交织ECC方案,以提升性能和错误容忍度。 Ramamoorthy等[40]提出了一种结合LDPC码的二维最小均方误差MMSE(Minimum Mean Squared Error)均衡方法,并研究了LDPC译码器在不同孔径大小和SNR下的译码性能。根据译码能力确定每个SNR下的最小孔径尺寸。在这些孔径下,采用与均衡结合的LDPC码在12次迭代后实现零错误率,而未使用均衡的LDPC码即使在25次迭代后仍会存在一些错误。Park等[41]提出了一种全息数据存储通道迭代的3/4音控软编码方案,并采用信道迭代模拟了LDPC码的性能。当BER为10-7时,经过一次信道迭代,其性能相比未经过信道迭代的LDPC码提高了0.8 dB。 基于二维软输出维特比算法SOVA(Soft Output Viterbi Algorithm)的BER明显低于一维Viterbi检测算法的BER,Kim等[42]将LDPC码与二维SOVA检测输出相结合,应用于全息存储系统,能够显著降低BER。通过将向量初始对数似然比LLR(Log Likelihood Ratio)信息转换为比特LLR,Kim等[43]提出了一种将全息数据存储的二维SOVA和纠错调制码融合的迭代译码方法。这种迭代方法虽然增加了算法的复杂度,但在抵抗噪声方面表现出良好的性能。通过将RS译码器的附加信息与决策反馈相结合,Sütó等[44]提出了一种基于二维页面访问光存储器中的数据检测技术,该技术降低了BER并将数据记录密度提高了11%。通过将RLL(Run-Length Limited)调制器和解调器作为纠错过程的一部分,Nakamura等[45]提出将游程长度受限RLL调制码与turbo码相结合的RLL-turbo码。实验结果显示,RLL-turbo码相比传统的LDPC码具有更高的纠错能力,且可以将数据密度提高1.78倍。

3.3 基于编码设计的优化方案

针对全息存储系统的特点,设计合适的纠错编码方案是提升可靠性的重要途径之一。全息信道中的串扰噪声使得重建数据页边缘的符号错误率高于中心位置的错误率,Garrett等[46]提出了一种将原始的等效错误保护转换为不等效错误保护的编码算法,为页面中的所有信息位提供不同程度的保护。当原始误码率为10-5到10-4时,该方案能够将BER分别降低到10-14和10-12。利用基于页面的全息存储器格式以及数据库记录的表格排列特性,Goertzen等[47]提出了一种适用于体全息存储系统中关系数据库信息编码的ECC,具有简单的解码硬件架构、较强的纠错能力以及较低的系统响应延迟等优点。针对页面间交叉干扰和边缘处噪声强的特征,Choi等[48]提出一种具有前向滤波自适应决策反馈的混合纠错方案,用于消除二维数据采集过程中产生的符号间干扰。为解决RS译码器的硬件复杂性和数据处理速率问题,Wu等[49]展示了用于体全息存储的16符号纠错(255,223)RS译码器结构的VLSI实现,设计了GF(28)快速乘法和流水线结构,数据处理速率可达200 Mbit/s。针对LDPC码硬件实现复杂、开发周期长以及硬件性能要求高的问题,Zhang等[50]利用高层次综合技术对LDPC译码算法进行硬件实现,通过分析不同因素下LDPC码的纠错性能,确定适合的译码器参数,以降低实现复杂度。

3.4 初始LLR信息优化

提高初始LLR信息的精度是提高LDPC译码性能的重要途径之一。Hayashi等[51]提出了一种利用重建像素之间的亮度差异来计算LLR信息的方法,在LDPC译码器的性能和复杂度之间取得了良好的平衡。在信噪比为12.5 dB,原始BER为1.3×10-2的情形下,LDPC译码器完全校正了全息记录再现信号中的比特错误。Yoon等[52]开发并评估了全息数据存储系统的位似然映射技术,利用中间译码步骤的反馈信息使LLR快速收敛到一个较大的值。通过额外的选择性概率部分补偿以降低迭代译码过程中由相邻像素带来的负面影响,Chung等[53]提出了一种改进的全息数据存储LDPC译码方案,提高了像素不对齐时的整体纠错性能。仿真结果表明,该方案优于传统的LLR置信传播算法。通过分析并利用相位解调特性识别可靠比特,Zhao等[54]提出了一种可靠比特感知的LDPC码优化方法,为可靠比特分配更精确的初始LLR的权重,优化后的初始LLR能更准确地反映解调数据的可靠性,进而提升了译码纠错性能。Yu等[55]利用重建的相位分布特征,提出了一种相位分布感知的LDPC码优化方案,通过施加多个相位检测阈值,提升了待纠正比特的初始LLR信息精确度,从而提高LDPC软判决译码的纠错能力。

综上所述,现有的LDPC码优化方案主要从多维纠错、与交织/均衡/检测技术相结合、编码方法优化以及初始LLR信息优化等方面开展研究,为提高全息存储可靠性提供重要技术支撑。提高初始LLR信息的精度相对于其他优化方式会更加易于实施,复杂度也相对较低,且能获得相当的甚至更高的译码纠错性能。然而,目前全息存储中的纠错码主要是面对振幅型全息存储的研究,缺少面向相位型全息存储纠错码的深入研究。下面详细介绍文献[56]提出的一种面向相位型同轴全息存储的参考光辅助的LDPC码ReLDPC (Reference-beam assisted LDPC)优化方案。

全息存储系统在进行译码之前,首先需要利用信道信息获取初始LLR信息,其幅值反映了比特的可靠性,幅值精度影响LDPC码的译码性能[55]。利用参考光的信息在记录和读取的过程中总是已知的,将参考光作为先验信息优化初始LLR信息精度,进而提升全息存储的可靠性。在配置每个待纠正比特的LLR时,需要考虑极性和幅值。在比特极性正确的情况下,LLR的幅值越大,可信度越高。在LDPC译码时,由于参考光所携带的数据(以下称为参考比特)在记录和读取的过程中都是已知的,因此参考比特的可信度远高于未知的信息比特和校验比特的可信度。首先确定极性,比特1的极性设定为“+”,比特0的极性设定为“-”;然后确定幅值。如图2所示,对于信息比特和校验比特,若为比特0,则初始LLR为-1;若为比特1,则初始LLR为+1。设定参考比特中的比特0的LLR为p;参考比特1的LLR为m(p+m=0,m>1),其中m>1保证了参考比特的LLR幅值大于信息比特和校验比特LLR的幅值[56]。传统LDPC硬判决译码在进行比特信息量化时没有考虑比特之间的可靠性差异,LLR精度较低,导致译码延迟高[57]。ReLDPC方案通过放大参考比特的LLR幅值,提高LLR信息的精度,进而提升LDPC译码纠错性能。该方法操作步骤如下:

Figure 2 Reference beam-assisted LDPC coding optimization scheme

步骤1信息比特连同相同数目的参考比特构成待编码的数据,随后进行LDPC编码生成校验比特。信息比特、参考比特和校验比特一起构成LDPC码字。

步骤2生成的LDPC码字被调制成二维数据页。调制规则为00→0,01→π/2,11→π,10→3π/2。调制后的二维相位数据页左半部分为信息数据和校验数据,右半部分为参考相位。

步骤3将调制后生成的二维相位数据页送入全息信道进行传输。在对数据进行读取时,读取后的数据形式为互补金属氧化物半导体CMOS(Complementary Metal Oxide Semiconductor)传感器捕捉到的傅里叶强度图。利用IFT算法重建相位数据页,重建后相位数据页的左半部分为未知的信息数据和校验数据,右半部分为已知的参考数据,重建后的相位页包含一定数目的错误相位。

步骤4将重建后的二维相位数据页进行相位判决和解调。取相邻相位的中间值作为判决阈值,解调规则如下:0→00,π/2→01,π→11,3π/2→10。

步骤5获取待纠正比特的初始LLR信息。LLR获取规则如下:当参考比特为1时,初始LLR设为m(m>1);当参考比特为0时,初始LLR设为p(m+p=0)。对于其他比特若为1,初始LLR设为+1,否则设为-1。

步骤6将获取的初始LLR信息送入LDPC最小和译码算法进行迭代译码[58,59]。

首先进行仿真实验以验证ReLDPC方案的有效性,随机生成长度为1 KB的信息比特流和长度为1 KB的参考比特流,组合成2 KB的数据进行LDPC编码(码率为0.89)生成0.25 KB的冗余比特。码字长度为18 432个bit,之后被调制成10个二维相位数据页。每幅相位页的大小为32×32=1024。基于相位调制规则,每幅相位页表示2 048个比特(32×32×2=2048)。生成的10幅相位页中右半部分为参考相位,前8幅相位页的左半部分为信息相位,后2幅相位页的左半部分为冗余相位。所有的参考相位是随机生成的已知相位。将生成的10幅相位页送入全息信道,每幅相位页被上载到空间光调制器SLM(Spatial Light Modulator)以生成信息光和参考光。为提高数据记录的准确性,每幅相位数据用SLM上的2×2个像素进行表示。在读取数据时,数据以傅里叶强度图的形式被CMOS捕获,并加入高斯随机噪声以模拟信道中的噪声[60,61]。当CMOS接收到傅里叶强度图时,每幅傅里叶强度图的灰度值被标准化为0~255。透镜焦距为150 mm,波长为532 nm,SLM像素尺寸为20 μm,CMOS像素尺寸为5.86 μm,CMOS 的动态范围是8 bit。利用接收到的强度图使用IFT算法对相位页进行重建。IFT最大迭代次数设为100,迭代阈值设为5.0×10-3。将重建后的相位进行判决并解调成一维的比特流进行LDPC译码,参考比特的LLR设为p=-5,m=5,译码最大迭代次数设为30次。在每次迭代结束后,分别统计了BER、译码迭代次数和译码成功的概率。

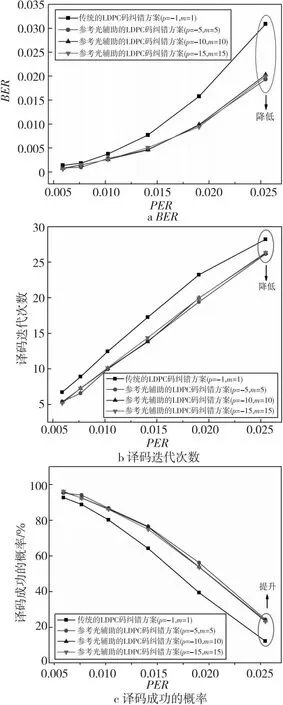

统计了在不同PER下,使用传统的LDPC码纠错方案和提出的ReLDPC方案分别对应的BER、译码迭代次数和译码成功率的变化[56],如图3所示。传统LDPC码指的是未经优化的标准LDPC码。随着PER的增加,使用提出的ReLDPC方案具有较少的译码迭代次数和较小的BER。与传统LDPC码纠错方案相比,如图3a所示,当PER为0.027 5时,BER平均可降低 38.8%;如图3b所示,当PER为0.019时, ReLDPC方案可减少约14.8%的译码迭代次数;如图3c所示,当PER为0.019时,ReLDPC方案的译码成功率提高了约38.4%。

Figure 3 Variation of the number of decoding iterations and BER for different reference beam weights

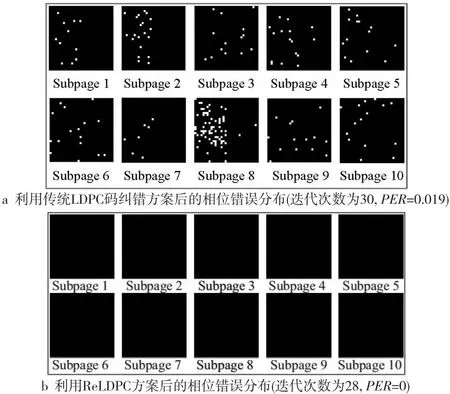

图4展示了利用传统LDPC码纠错方案与ReLDPC方案纠错后的相位错误分布[56]。如图4a所示,当传统LDPC码的译码迭代次数达到所设定的译码迭代次数最大值30时,PER为0.019;如图4b所示, 在译码迭代次数为28时,PER为0。与传统LDPC码纠错方案相比,ReLDPC方案显著降低了PER,减少了译码迭代次数,提高了相位型同轴全息存储系统的可靠性。

Figure 4 Phase error distribution of reconstructed phase pages

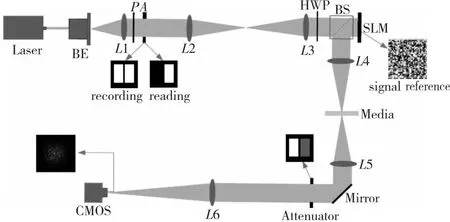

接着,通过实验进一步验证ReLDPC方案的有效性。图5所示,展示了真实的全息存储光路[56]。从激光器发出的光经过激光扩束器BE(Beam Expander)进行扩束。P是产生线偏振光的线性偏振器。使用2个相同矩形窗口形状的方形孔径A,左边和右边的窗口分别表示信息光和参考光。采用半波片HWP(Half-Wave Plate)调节光的偏振状态以满足SLM的要求。分束器BS(Beam Splitter)将一个波束分成2个或多个波束。相位数据页被上载到SLM以产生调制光束。参考光和信息光相互干扰,形成记录在介质上的干涉条纹。在记录过程中,2个矩形窗口打开。读取数据时,遮挡信号部分的窗口仅使得参考光通过。由于重建后的信息光是一束强度较低的衍射光,因此使用衰减器来平衡读取过程中信息光与参考光部分之间的强度差。重建光的傅里叶强度由CMOS探测器在傅里叶透镜L6的后焦平面上捕获。相关光学器件的参数如表1所示。

Table 1 Parameters of optical devices

Figure 5 Schematic diagram of holographic storage experiment system

统计了1 000个数据帧的译码迭代次数和BER[56],分别如图6所示。数据帧定义为一个码字中的信息比特序列。如图6a所示,使用传统的LDPC码纠错方案后,有935个数据帧达到了最大译码迭代次数30。然而,ReLDPC方案仅有259个数据帧达到最大迭代次数。相比传统的LDPC码纠错方案,ReLDPC方案能够将译码迭代次数平均降低31.6%。

Figure 6 Number of decoding iterations and BER of 1 000 data frames

另外,统计了1 000个数据帧的BER变化情况。如图6b所示,在使用提出的ReLDPC方案后,有750个数据帧中的错误比特被完全纠正,而传统的LDPC码纠错方案只能将极少数的数据帧中的错误比特完全纠正。经计算,使用提出的ReLDPC方案和传统的LDPC纠错方案后,平均BER分别为0.002 2和0.009 7。相比传统的LDPC纠错方案,ReLDPC方案使BER平均降低77.3%。实验结果表明,所提出的ReLDPC方案能够显著减少LDPC码纠错方案的译码迭代次数,降低BER,进而提升纠错性能。

4 结束语

随着全球数据量爆发式增长,全息数据存储具有高密度、大容量、长寿命和高数据转换速率的优势,有望成为现有冷数据存储的最佳方案。本文首先介绍了全息数据存储系统,并分析了当前纠错码用于全息存储的研究现状。为了提高相位型同轴全息存储数据可靠性,提出了一种参考光辅助的LDPC码优化方案,利用已知的参考光信息优化初始LLR信息,显著降低了BER,减少了译码迭代次数。