一款基于GaAs 工艺的改进型Wilkinson功率分配器芯片

2024-03-01汪柏康张沁枫孙文俊秦战明权帅超

张 斌,汪柏康,张沁枫,孙文俊,秦战明,权帅超

(中国电子科技集团第五十八研究所,江苏 无锡 214035)

0 引言

在射频/微波系统中,功率分配器(简称功分器)是最常见的无源器件[1]。功分器是一种将信号功率按照工程实际需求来分配的器件,在分支端口相位幅度一致的情况下,也可用于功率合成器,实现多路信号的功率合成。在多通道大规模射频收发集成电路系统中,功分器是信号的“中转站”,为系统实现信号的分配与合成。随着微波毫米波电路小型化、高集成度、超宽带的发展,研发一款高性能的功分器至关重要。

功分器的实现方式有很多种,如SIW 功分器[2]、波导功分器[3]、微带功分器[4]等。SIW 功分器和波导功分器一般多用于大功率收发系统模块间的功率合成或分配,这类功分器体积大、频带窄,只适用于特定电路系统。而微带功分器又可分为Wilkinson 功分器、电阻性功分器和T 型结功分器,其中Wilkinson 功分器由于结构简单、易于集成、隔离度高等优点被广泛应用[5]。

近年来随着半导体技术的飞速发展,以化合物半导体(GaAs、GaN、InP 等)为衬底的单片微波集成电路(MMIC)成为当今小型化、超宽带、高集成度、低成本和多功能设计的主要研究方向[6]。本文以实际项目需求为背景,借助于是德科技公司(KEYSIGHT)的ADS(Advanced Design System)软件[7],以及与之适用的国内某GaAs IPD 工艺代工厂提供的PDK(Process Design Kit)工艺设计包,设计一款性能良好的4~20 GHz 小型化、改进型一分二Wilkinson 功分器芯片。

1 电路设计

1.1 Wilkinson 功分器理论分析

功分器的技术指标包含工作带宽、分配损耗(固有损耗)、插入损耗、输出端口的隔离度以及端口回波损耗等,这些性能的优劣决定了功分器的优劣[8]。

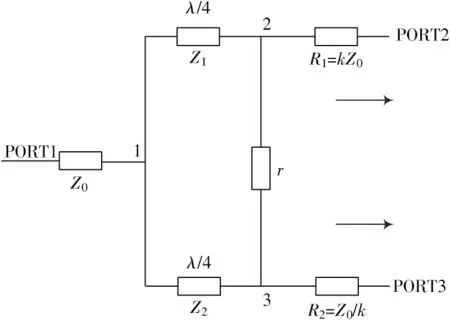

图1 所示为单节传统一分二Wilkinson 功分器电路原理图,输入端口为特性阻抗Z0=50 Ω 的传输线,输出端口为特性阻抗R1、R2(单位为Ω)的传输线,中间的分支结构由两根电长度均为λ/4 的特性阻抗Z1和Z2的传输线以及隔离电阻r组成。当信号由端口1 输入时,经过分支网络分为两路信号,由端口2、端口3 输出。

图1 一分二Wilkinson 功分器电路原理图

根据功分器端口匹配的三个条件[9],可以得到图1中Wilkinson 功分器的各项参数,公式为:

式中k2为两个输出端口的功率比。对于二等分功分器来说,即k2=1,输出端口特性阻抗R1、R2等于输入端口的特性阻抗Z0,功分网络两条支路特性阻抗Z1=Z2=Z0,隔离电阻r=2Z0。此时两路信号幅度相同、相位相等,由于端口2 与端口3 之间被隔离电阻r直接连通,使得从端口2 经由功分结到达端口3 的信号相比直接从端口2 经隔离电阻r到达端口3 的信号多走了两个λ/4 波长的距离,两股信号在端口3 处形成180°的相位差进而相互抵消掉,同样从端口3 进入的信号到达端口2 时亦会相互抵消,所以功分器两输出端口之间具有非常良好的隔离性[10]。

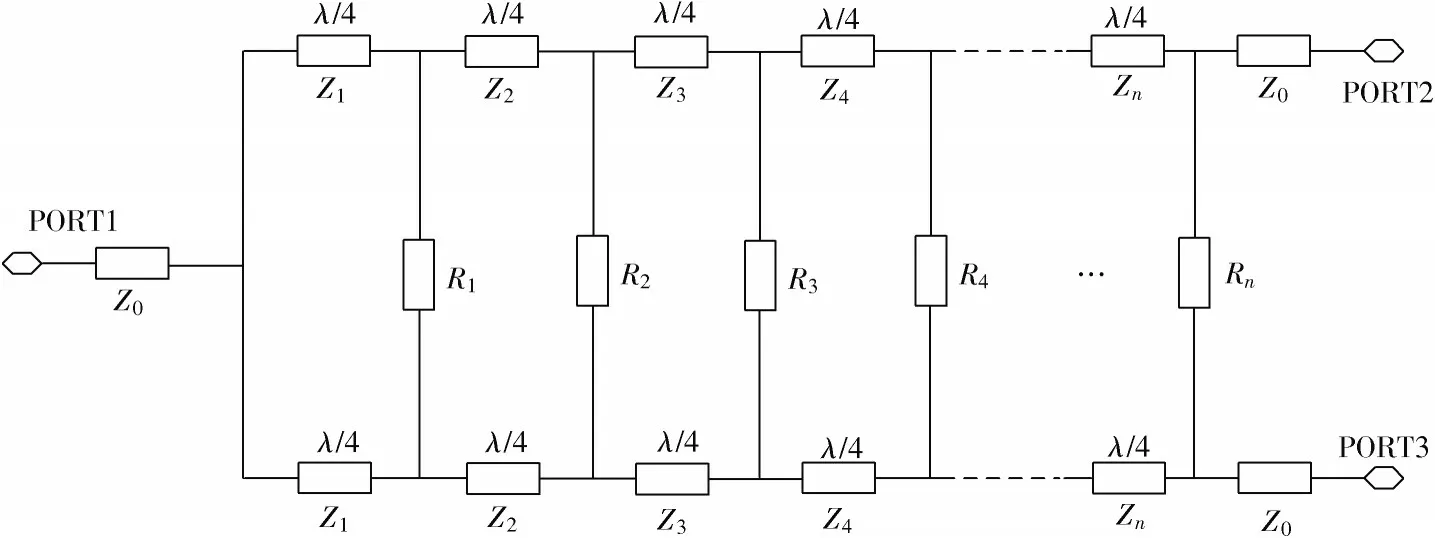

以上分析针对于单节一分二功分器。单节功分器设计简单,具有插损小的优点,但频带较窄、隔离度不高。当使用单节结构设计宽带功分器时,电路的参数指标会恶化,这时可以通过增加功分器节数来扩大带宽,提高隔离度。图2 所示为多节结构的二等分Wilkinson功分器电路。多节结构功分器传输线特性阻抗和隔离电阻分析方法与单节分析方法类似。图中,Z1,Z2,…,Zn分别为各节电长度为λ/4 传输线的特性阻抗,R1,R2,…,Rn分别为各节之间的隔离电阻[11]。在多节阻抗变换中,若各阶梯阻抗产生的反射波彼此抵消,便可以使匹配的频带变宽[12]。由此可知,选用Wilkinson 的节数越多,功分器的工作频带也就越宽。实际设计功分器时,应根据性能指标要求选择合适的节数。

图2 多节一分二功分器电路图

表1 为多节一分二功分器的设计参数,其中f2/f1为比例带宽,N为节数,ISO(min)为理想时最小隔离度。由表1可以得到各节的λ/4传输线特性阻抗和隔离电阻。

表1 多节一分二功分器参数

1.2 改进的Wilkinson 功分器设计

1.2.1 电路拓扑结构的改进

对于超宽带Wilkinson 功分器的设计,不能盲目增加节数。功分器的损耗会随着引入节数的增加而增加,同时电路面积也会变大。

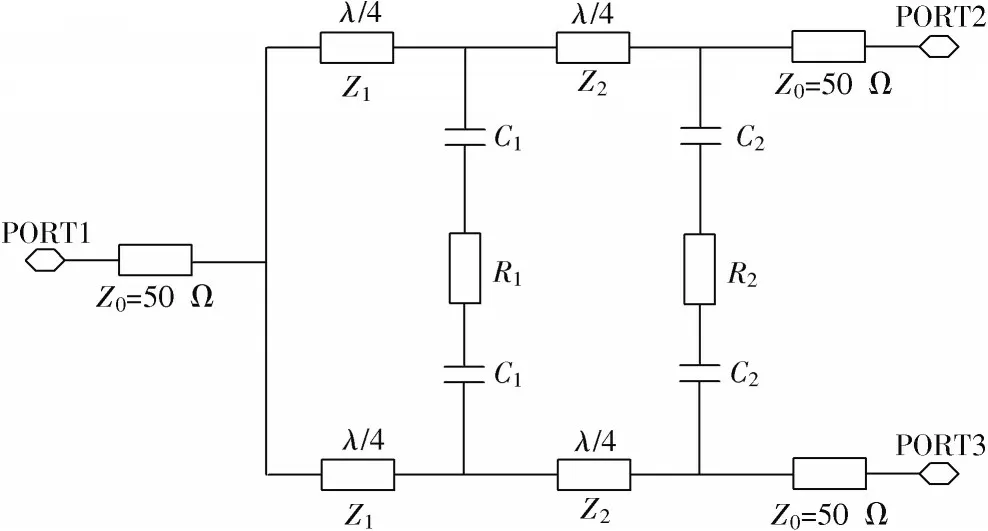

本文设计的功分器频率为4~20 GHz,比例带宽f2/f1=5,由表1 可知,传统设计至少需要4 节结构,电路面积会非常大。为了实现小型化、超宽带的要求,本文设计采用两节改进后的Wilkinson 功分器拓扑结构,如图3 所示。在传统一分二的Wilkinson 功分器隔离电阻的两端,分别引入大小相等的2 个串联频率补偿电容C1、C2。这种电容电阻串联网络有两方面作用:一方面可以实现低频段的耦合抑制功能,从而提升低频段端口之间的隔离度,扩展功分器带宽,在不增加尺寸的条件下将传统两节Wilkinson 功分器的比例带宽由2∶1 提升至5∶1;另一方面,加入的电容可以参与端口匹配,优化电路的端口回波损耗。这种新型结构功分器的各分支特性阻抗和隔离电阻依旧可以通过表1 查得,电容大小根据具体电路实际优化得到。

图3 改进后的Wilkinson 功分器电路图

由表1可知:当Z0=50 Ω 时,第1节阻抗Z1=81.99 Ω,第2 节阻抗Z2=60.985 Ω,隔离电阻R1=98 Ω,隔离电阻R2=241 Ω。在确定工艺,已知传输线中心频率、特性阻抗和电长度的情况下,可以根据ADS 中LineCalc 插件[13]算出传输线的宽度和长度,如图4所示。由此得到:第1节传输线宽度W1=14.5 μm,长度L1=2 320 μm;第2 节传输线宽度W2=41 μm,长度L2=2 243 μm。对于这个长度的传输线,采用传统的操场式布局走线,电路尺寸会非常大[14]。

图4 LineCalc 计算传输线

1.2.2 电路版图布局的改进

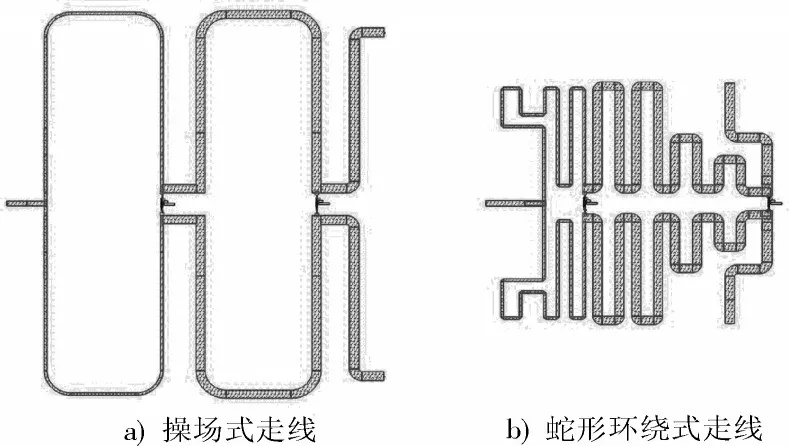

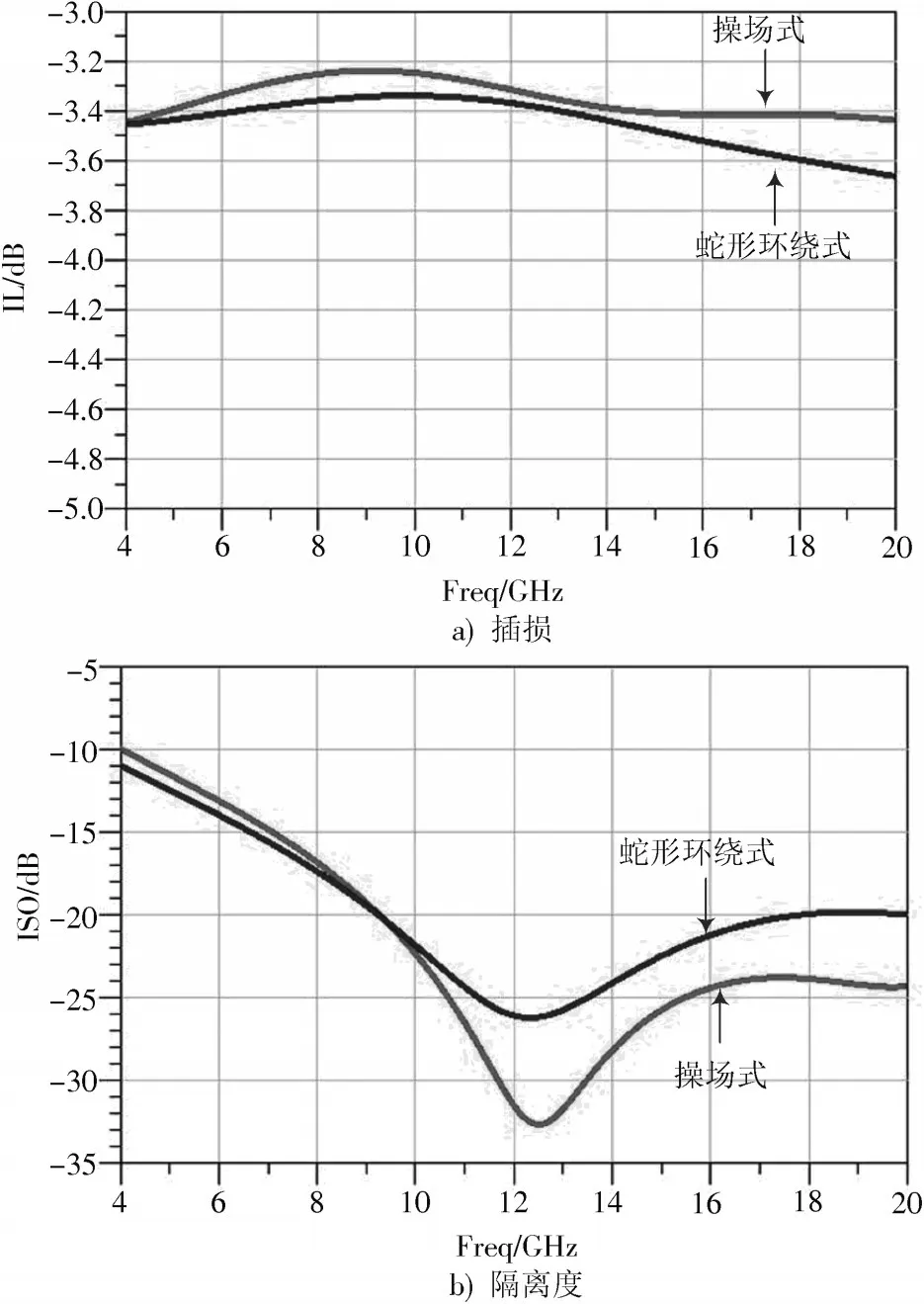

为了满足小型化的需求,对功分器的走线布局进行改进,将操场式走线改为蛇形环绕式走线,有效缩小了功分器的面积。图5 所示是同等电长度下操场式走线与蛇形环绕式走线的版图对比。两种结构电长度相等,隔离电阻相同,均未添加补偿电容,仿真对比如图6 所示。由图5、图6 可知,两种结构的电性能偏差在可调整范围内,但是采用蛇形环绕式走线的电路面积比操场式走线的电路面积减小近半。

图5 操场式和蛇形环绕式两种布局走线对比

图6 操场式和蛇形环绕式两种布局走线仿真对比

1.2.3 改进后的电路优化仿真

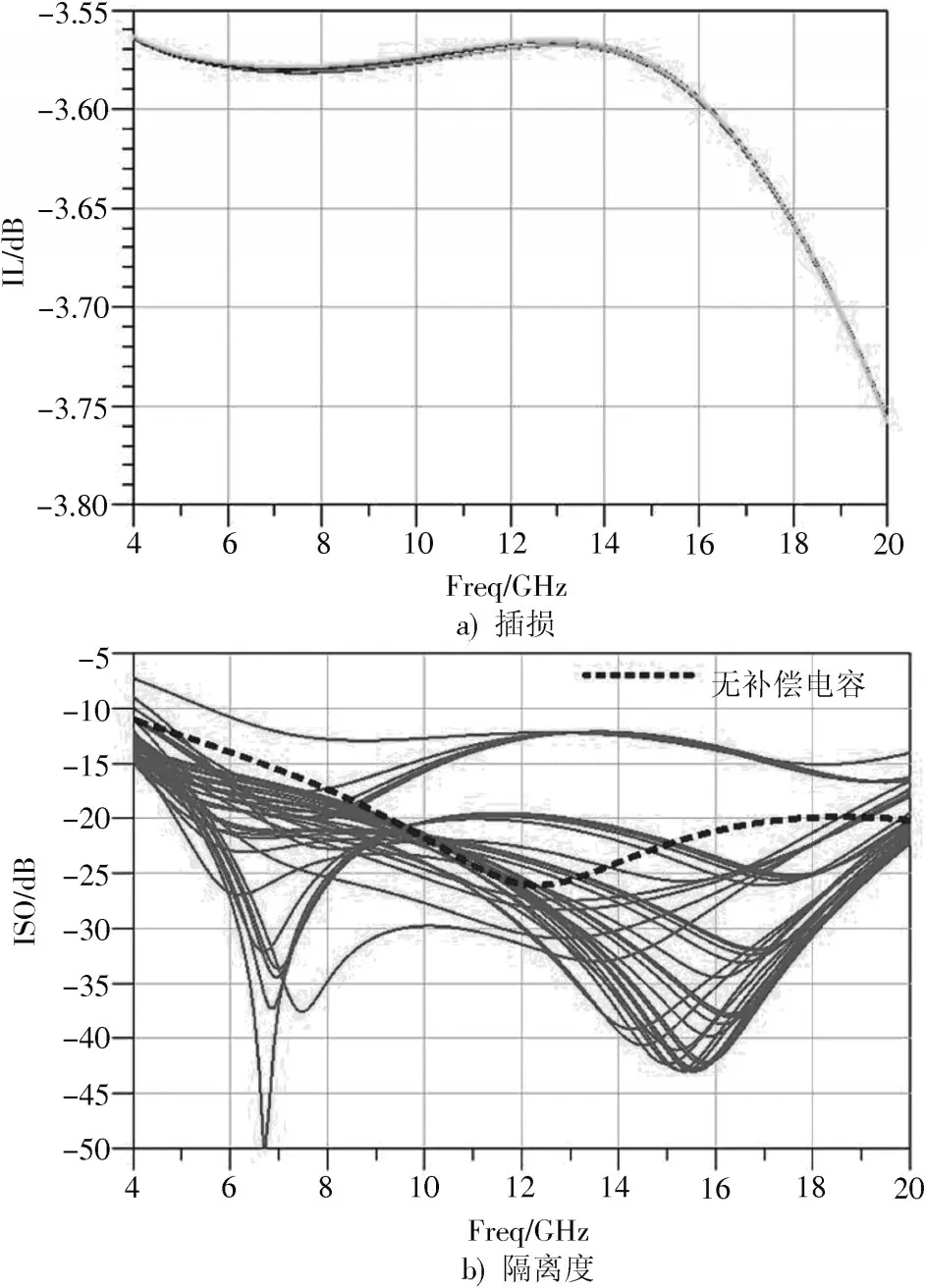

如图7 所示,在蛇形环绕式功分器的隔离电阻处加入补偿电容。在ADS 原理图中,扫描电容C1、C2,C1扫描范围为0.1~1 pF,C2扫描范围为0.1~1 pF,得到的S参数仿真结果如图8 所示。

图7 加入补偿电容后的蛇形环绕式功分器

图8 扫描补偿电容仿真结果

由图8 中可以看出,加入补偿电容对插损影响非常小,对隔离度的改善非常显著。最终迭代仿真,优化得到串联电容C1=0.6 pF,C2=0.55 pF。最终设计的电路版图如图9 所示,该电路momentum 电磁仿真结果如图10所示。

图10 功分器仿真结果

由图10 可以看出,在4~20 GHz 内,分配损耗为3 dB,插损典型值为0.65 dB,回波损耗典型值为20 dB,隔离度典型值达到25 dB,说明该功分器的性能达到了加工流片标准。

2 测试结果分析

芯片加工是基于国内GaAs IPD 工艺线完成的,该工艺线采用了外延和离子注入技术,表面采用了SiN 保护,使得芯片具有良好的接地和稳定性[15]。

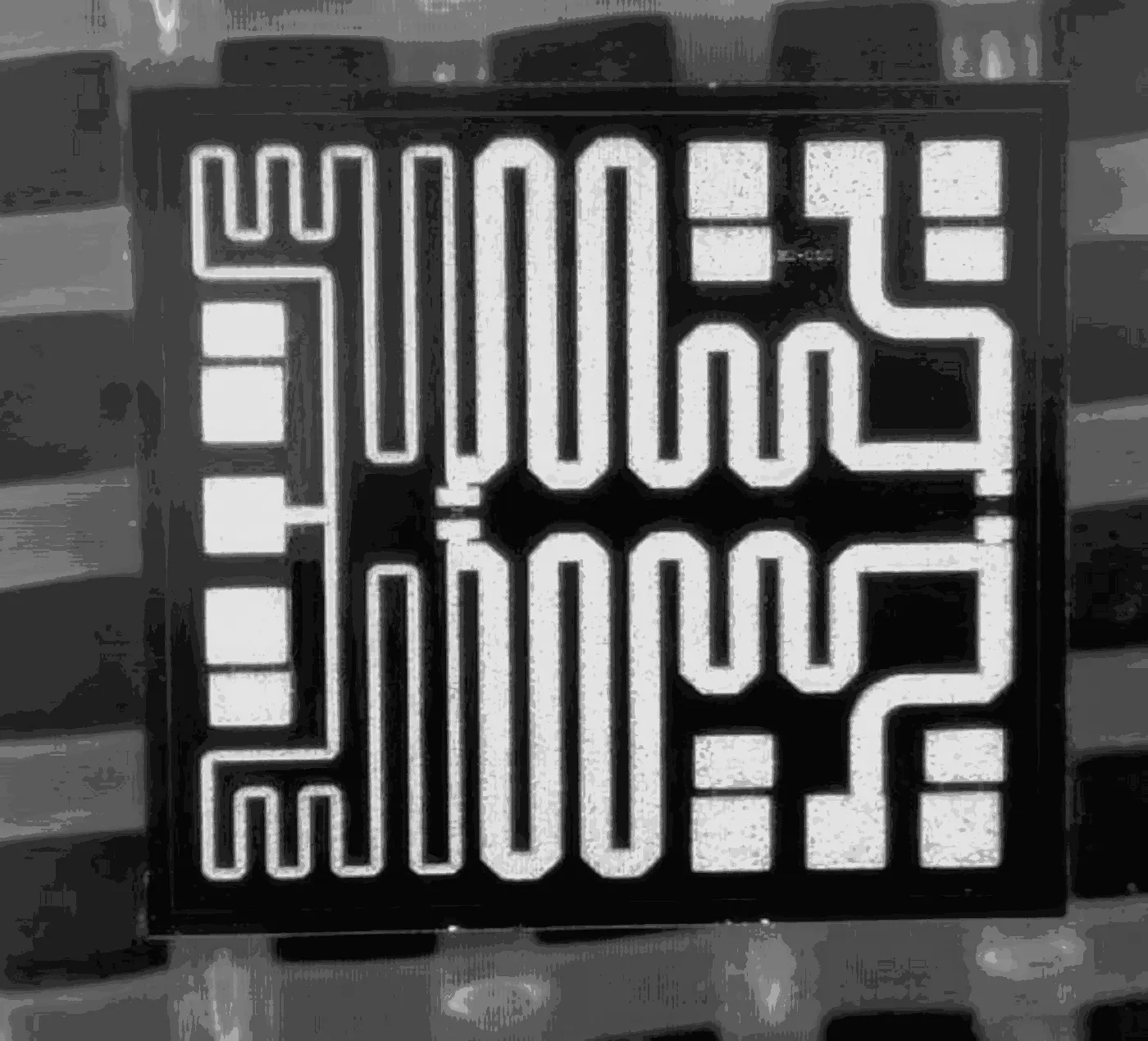

图11 所示为功分器芯片的实物图,整个芯片尺寸为1.0 mm×0.9 mm×0.1 mm,芯片内部主要包含有薄膜电阻、MIM 电容、微带线等元器件。

图11 功分器芯片实物图

微波测试系统由Cascade Microtech 探针台、PNA⁃XN5244A 矢量网络分析仪[16]组成。

芯片实物测试结果如图12 所示,可以看出实测结果与仿真结果相似,通带内插损典型值为0.65 dB,隔离度典型值达到25 dB,输入回波损耗≥14 dB,输出回波损耗≥15 dB。实测结果满足设计要求,芯片间测试一致性良好。

图12 芯片测试结果

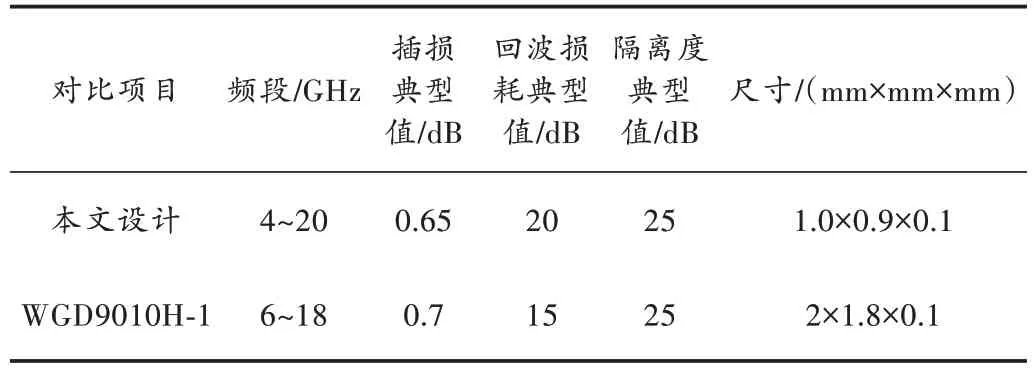

本文设计的功分器与国内产品手册中类似频段功率分配器的性能指标对比结果如表2 所示。

表2 指标对比

由表2 可以看出,本文设计的功率分配器性能优良,在带宽和尺寸上极具优势,尺寸仅为手册产品WGD9010H⁃1 的1/4。

3 结论

本文通过对功率分配器的理论分析,使用蛇形环绕式结构取代传统的微带线结构,并在功分器隔离电阻处引入了频率补偿电容,基于砷化镓(GaAs)工艺,借助ADS 软件成功设计了一款新型结构的一分二Wilkinson功分器。芯片实物测试结果表明,在通带4~20 GHz内,插入损耗典型值为0.65 dB,端口回波损耗典型值为20 dB,端口隔离度典型值达到25 dB,芯片尺寸仅为1.0 mm×0.9 mm×0.1 mm。

该芯片具有频带宽、插损小、尺寸小、隔离度高等优点,且基于GaAs 工艺,性能稳定,使用方法简单,可以应用于射频/微波电路系统中。后续会使用此新型Wilkinson 结构设计一分四、一分八等功分器,实现多分路功分器的高性能化和小型化。