一种基于C单元的三节点翻转自恢复锁存器*

2024-01-24孙皓洁马瑞君梁华国黄正峰

徐 辉,朱 烁,孙皓洁,马瑞君,梁华国,黄正峰

(1.安徽理工大学计算机科学与工程学院,安徽 淮南 232001; 2.合肥工业大学微电子学院,安徽 合肥 230009)

1 引言

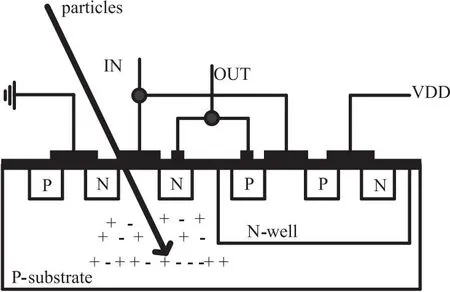

伴随着时代不断发展,工艺技术不断精进,在纳米级别的金属氧化物半导体集成电路中,晶体管的尺寸也同时在快速缩小。晶体管的缩小虽然带来了很多优势,例如低成本和低功耗,但是也会不可避免地带来一些问题,软错误便是其中之一。软错误通常是由空间中的带电粒子对电路的轰击造成的[1-3]。如图1所示,高能粒子冲击内存模块底层电路上的晶体管时,产生的电荷会通过漂移和扩散机制被附近的PN结吸附。当电荷量积聚到一定程度后,便会产生一个瞬态脉冲,导致电平值异常。异常的电平值传导到电路功能模块,此时会产生错误的逻辑值,这种情况被称为单粒子翻转SNU(Single-Node-Upset)[4-6]。因为集成电路本身的连接复杂,加之电荷共享,很多敏感节点逻辑值都会同时受到影响,从而产生多节点翻转MNU(Multiple-Node-Upset),比如三节点翻转TNU(Triple-Node-Upset)[7,8]。目前针对MNU的主流研究方向是针对TNU进行加固。据研究,节点翻转后,发生MNU的概率在40 nm技术中达到了35%以上,而TNU发生的概率占到了8%,且随着工艺技术的进步,TNU发生的概率逐步在上升。节点翻转会导致数据存储和执行错误,甚至系统崩溃,这都将会影响系统的正常工作[9,10]。因此,设计出低功耗、能容忍TNU且自恢复的锁存器具有实际意义。

Figure 1 Particles strike transistor图1 粒子轰击晶体管

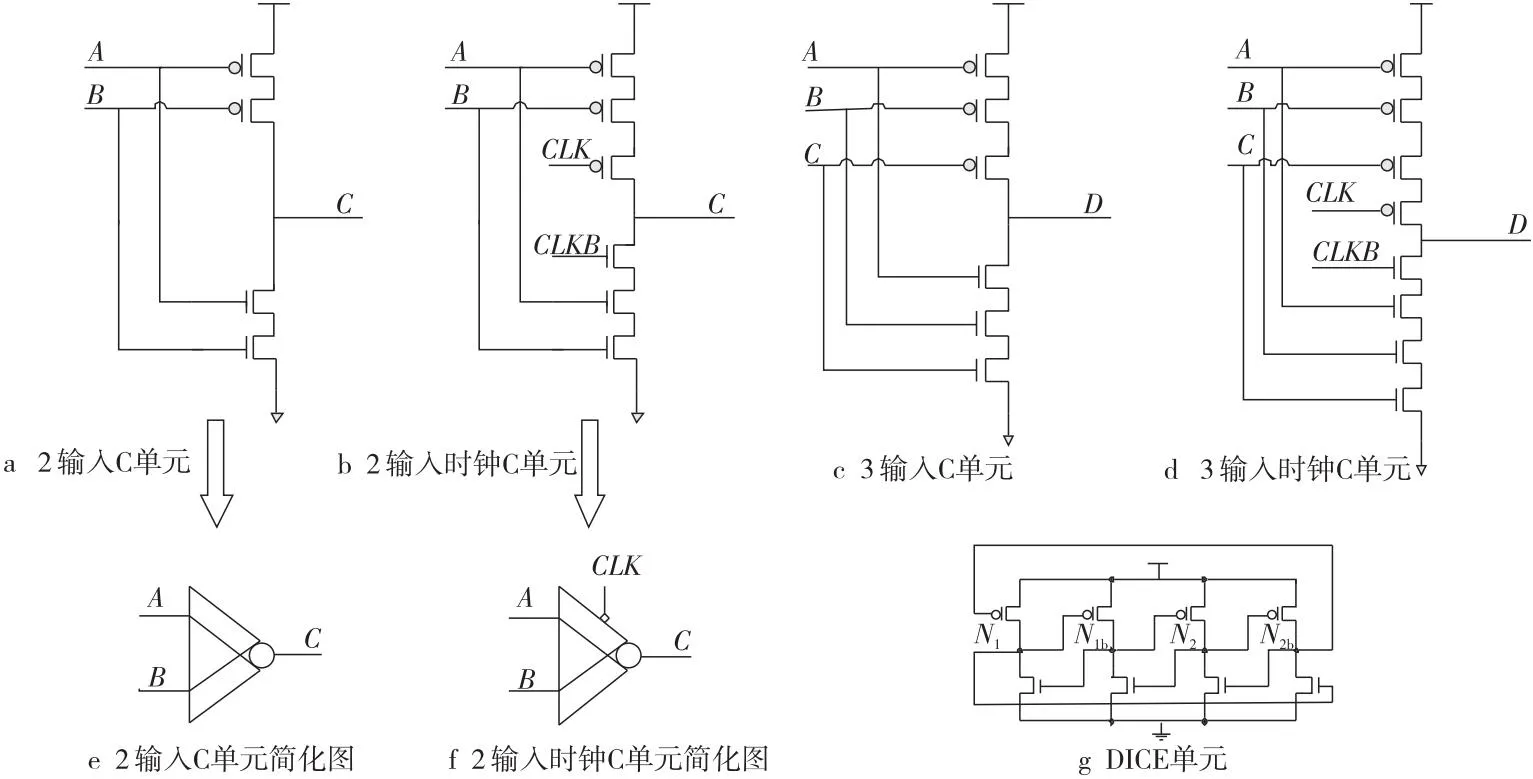

Figure 2 C-element and clock C-element of different inputs, and their symbols of C-element and clock C-element, and DICE element图2 不同单元输入的C单元和时钟单元及其单元简化图和DICE单元

为了解决TNU,涌现出了很多加固的方式,比如布局隔离、空间冗余技术和电路设计加固。其中,主要的解决方案仍然是电路设计加固。因此,本文提出一种基于C单元的三节点翻转自恢复锁存器MKEEP。通过仿真实验表明,相比于其他锁存器,本文所提的MKEEP锁存器不仅具有三节点翻转自恢复的能力,同时还有功耗小、延迟低的特点。

2 现有的结构和锁存器

在很多的锁存器加固设计中,由于C单元容忍单节点翻转的特性,它的应用无疑是很广泛的。图2a~图2d代表的是不同输入的C单元和时钟C单元。当C单元输入相同时,输出便是输入相反的逻辑值;如果输入不相同,此时便是C单元的高阻状态。同时,C单元与时钟相配合使用可以减少锁存器在透明时期的功耗。除了C单元之外,还有双互锁存储锁存器DICE(Dual-Interlocked storage CEll)。DICE锁存器可以实现单节点翻转自恢复的特性受到很多青睐。

随着对锁存器加固设计研究的深入,基于这些基础结构,很多容忍或者同时具备节点翻转自恢复能力的锁存器涌现了出来。

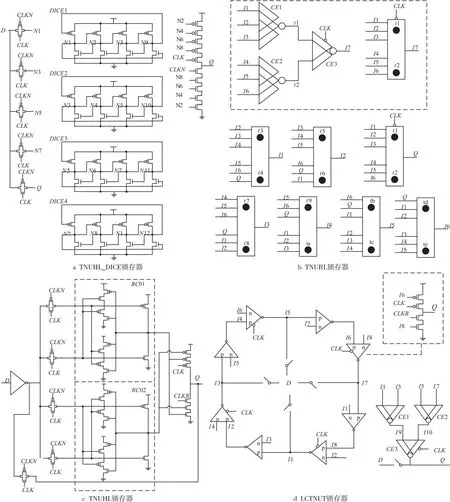

Figure 3 TNUHL-DICE, TNURL, TNUHL, and LCTNUT latches图3 TNUHL-DICE、 TNURL、TNUHL和LCTNUT锁存器

如图3a所示,TNUHL_DICE(TNU-Hardened Latch based on Dual-Interlocked storage CEll)锁存器利用了DICE单元的相互配合,具备了三节点翻转并自恢复的能力。如上文所述,DICE单元首先完全容忍单节点翻转,在DICE单元中4个存储节点中任何一个节点发生了翻转,都会被其他未受影响的节点恢复。TNUHL的锁存器设计使用了4个DICE单元相互配合弥补DICE单元的不足之处。在最坏的情况下,也就是2个锁存器都被翻转节点所影响的时候,利用剩下的2个DICE单元进行恢复;同时使用了时钟C单元的变形模式,增加了2个输入,当有3个节点发生翻转时,4输入的时钟C单元会将错误逻辑值拦截使之不会影响输出Q。但是,TNUHL锁存器的4个DICE单元没有配合时钟进行使用,所以功耗相对较高。

图3b中的TNURL(TNU self-Recover Latch)锁存器结构是由一种软错误拦截模块SIM(Soft-error-Interceptive Module)构成的。如图3b虚线圈起来的结构所示,其中SIM结构是由3输入的C单元和1个时钟C单元组成。锁存器面对的最大威胁就是高能粒子轰击在同一个SIM结构上,造成SIM结构中一个3输入的C单元输出发生翻转,但是错误逻辑值会被下一层的时钟C单元拦截,无法进一步扩大影响范围。在恢复阶段,通过未受影响的其他SIM结构中时钟C单元的输出将逻辑值恢复。

图3c中的TNUHL锁存器使用了一个非常对称而又巧妙的设计,这种设计就是图中圈注的恢复电路部分RC(Restore-Circuit),同时还使用2输入的时钟C单元进行错误逻辑值的拦截,以保证不输出错误的逻辑值。TNUHL锁存器的功耗延时都非常出色,但是这种锁存器设计的目的是容忍三节点翻转,却没有自恢复的能力。

图3d中LCTNUT(Low Cost and TNU completely Tolerant latch)锁存器左半部分的设计使用了反相器输入分离的结构,并构成一个循环的路径,同时使用2个C单元和1个时钟C单元搭建成拦截错误逻辑值的层次结构。相比于C单元的锁存器结构,LCTNUT锁存器使用了更少的晶体管,降低了整体的功耗开销;而且在结构上还配合了时钟,以便于在透明期减少功耗开销。但是,这种锁存器只能容忍三节点翻转,无法自恢复。

3 MKEEP锁存器

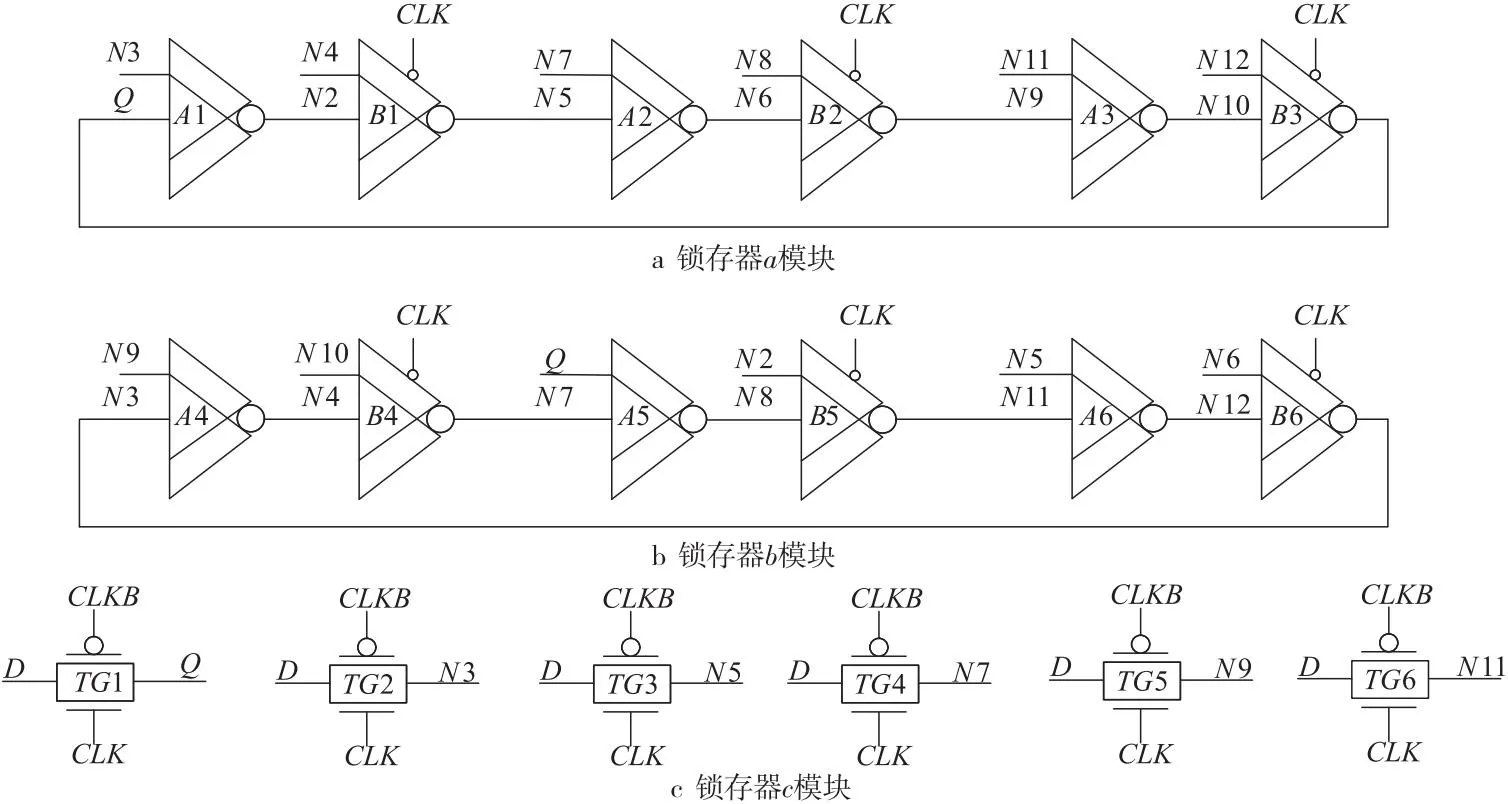

MKEEP锁存器结构如图4所示。图4中,D、Q分别为输入信号和输出信号,CLK、CLKB为时钟信号。结构组成包括7个传输门、6个C单元和6个时钟C单元。

Figure 4 MKEEP latch图4 MKEEP锁存器

3.1 工作原理

当CLK=1,CLKB=0时,锁存器处于透明期。通过传输门TG1至TG6,节点Q、N3、N5、N7、N9、N11得到由输入D传递的数据;然后,这6个节点分别通过a、b模块中的C单元A1~A6赋予其他节点逻辑值;而此时的所有时钟C单元处于关断状态,目的在于减少功耗,避开电流竞争。

当CLK=0,CLKB=1时,锁存器处于锁存期。此时传输门全部关断,时钟C单元全部导通,模块a、b内部节点之间便会产生反馈回路来保存数据。

下面将进行锁存器容错分析:

(1)单节点翻转:例如当输出Q受到了辐射粒子的轰击,此时,节点Q所在的C单元A1和A5都根据自身防止单节点翻转的特性将错误的逻辑值阻塞,使受到影响的节点无法对电路造成更大的影响。接下来,通过时钟C单元B3将Q点的逻辑值恢复。其他的单节点翻转亦是如此情况,MKEEP锁存器完全容忍单节点翻转并可以自恢复。

(2)双节点翻转:双节点翻转的情况分为2种。如果两个节点不是在同一个C单元上发生翻转,这种情形和单节点翻转的情况一致。双节点翻转的最糟糕情况就是同一个模块同一个C单元中2个节点的翻转,引起了第3个节点的翻转。例如,在a模块中,当Q节点翻转和N3节点翻转同时发生的时候,C单元A1输出的逻辑值翻转,如此下来节点N2就会受到影响。因此,N2所在的时钟C单元B1会处于高阻态。在b模块中,节点Q、N3和N2都是分别作用于C单元A5、A4和时钟C单元B5,错误的逻辑值都会被所在的C单元或者时钟C单元拦截住。锁存器的恢复就开始展开;首先节点Q的值将会通过时钟C单元B3恢复,节点N3的值将会通过节点N6和N12恢复;最后,节点N2通过C单元A1恢复。

(3)三节点翻转:三节点翻转分为4种情况。

第1种情况就是在2个模块中3个节点分散开来分别影响3个C单元,这种情况相当于3个单节点翻转情形的叠加,这里不再赘述。

第2种情况比起第1种情况更糟糕些;例如,当节点N3、Q和N7发生翻转的时候,此时在a模块中,C单元A1的输出N2彻底发生翻转,但是错误逻辑值被时钟C单元B1拦截住,而节点N7产生的错误逻辑值则被C单元A2拦截住。在b模块中,节点N3发生翻转,C单元A4拦截住了错误逻辑值。节点Q和N7发生翻转后,C单元A5就会发生错误输出,此时节点N8也会翻转,但是时钟C单元B5拦截住了错误的逻辑值。也就是这种情况影响了Q、N2、N3、N7、N8一共5个节点,但是错误的逻辑值都被锁存器拦截住了。至于恢复阶段,时钟C单元B3和B4的正常输出将恢复节点Q、N7的状态;时钟C单元B6的正常输出将更正节点N3的输出;在节点Q、N3的正常逻辑值恢复之后,同时C单元A1的输出将会恢复,节点N2则回归到正常逻辑值;节点Q、N7的正常逻辑值使C单元A5正常输出,恢复节点N8的状态。由此看来,锁存器完全可以应对三节点翻转的第2种情况。

第3种情况也是比较糟糕的一种情况。例如,当节点N3、Q和N4发生翻转的时候,对于a模块中的C单元A1,它的输出将会翻转,也就是造成节点N2的翻转;由于节点N4翻转,此时的时钟C单元B1的2个输入都发生翻转,所以B1的输出N5也会翻转;但是由于节点N7未发生翻转,所以C单元A2将错误的逻辑值拦截住。也就是说,此次3个翻转的节点造成了另外2个节点的翻转,一共5个节点发生了翻转。对于b模块,在上文中的工作原理中也说明了,这正是MKEEP锁存器的重点之处,将5个节点分别散落放在锁存器结构的不同C单元上,这样,对于b模块中的C单元就会将所有的错误逻辑值拦截住。接下来就是这种情况的恢复。首先a模块中时钟C单元B3持续输出的正确逻辑值将Q恢复;b模块中的时钟C单元B6将恢复节点N3的正确逻辑值;a模块中的C单元A1输出则因为2个输入的恢复而正常,那么N2的逻辑值将会被恢复;同理,b模块中的C单元A4则会将N4的正确逻辑值恢复过来;最后,在节点N2、N4正确恢复之后,节点N5的逻辑值也被正确恢复。锁存器所有的节点都被正确恢复,并继续正常工作。

第4种情况影响的节点数应该是最糟糕的一种情况。例如,节点N1、N3和N9发生翻转,那么此时影响节点的范围相对于第3种情况进一步地扩大。在a模块中,节点Q、N3的翻转使节点N2发生了翻转;b模块中节点N3、N9的翻转导致了节点N4的翻转;同时节点N4发生翻转反馈至a模块,N5因此发生翻转;但是节点N7没有发生翻转,所以传输的错误值被C单元A2拦截。同样,由于节点N9的翻转,a模块中的C单元A3处于高阻态,b模块中的时钟C单元和C单元B4、A5、B5、A6分别拦截住了节点N4、Q、N2、N5传递的错误逻辑值。由于错误的逻辑值没有继续往下传播,恢复的步骤就可以依据正确工作的逻辑值展开。节点N9的逻辑值,可以通过时钟C单元B2正确恢复;节点N3可以通过时钟C单元B6正确恢复;节点N3、N9的正确恢复就可以使C单元A4输出正确的逻辑值,因此节点N4正确恢复;节点Q可以通过时钟C单元B3正确恢复;由于节点N3、N1恢复至正确的逻辑值,所以节点N2可以通过C单元A1正确恢复;同理,节点N5也可以被正确恢复。所以,以上被影响的节点都被恢复。

综上所述,MKEEP锁存器完全可以实现三节点的容忍并自恢复。

3.2 故障注入实验

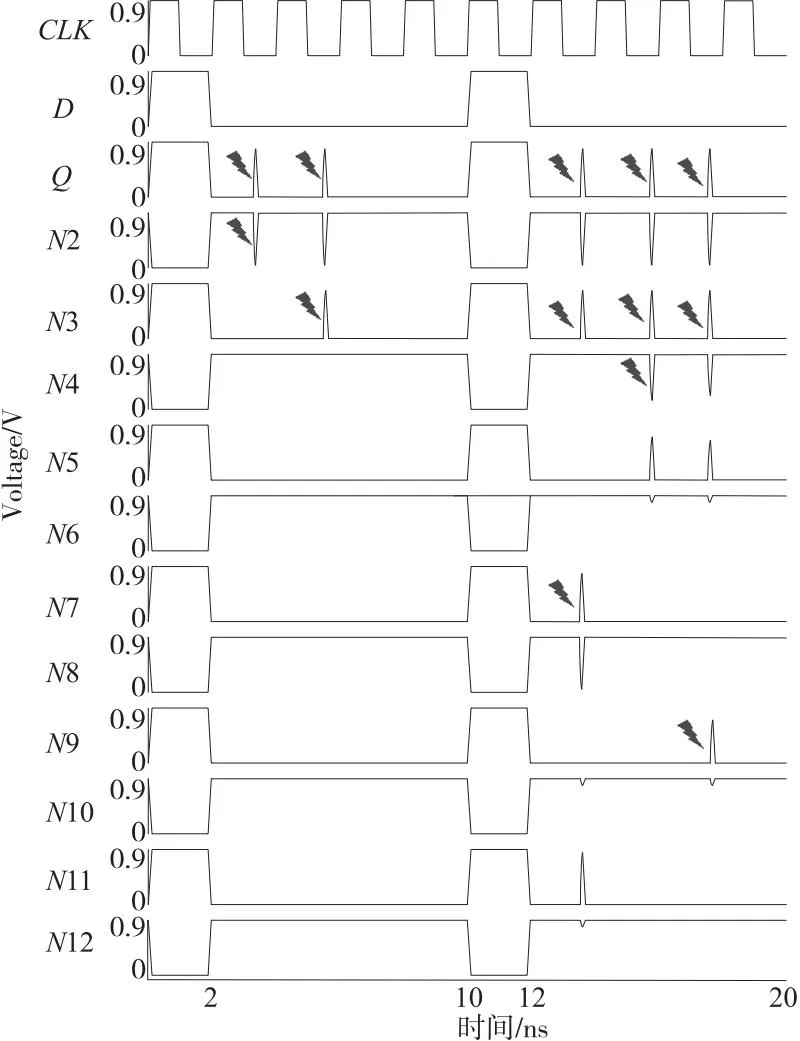

本节将会通过实验来验证MKEEP锁存器的鲁棒性和节点冗余自恢复能力。使用仿真软件HSPICE并基于32 nm的工艺模型,设定的电源电压为0.9 V,温度为27 ℃,时钟频率为500 MHz。NMOS管的长宽比是1∶1;PMOS管的长宽比是1∶2。图5和图6中是MKEEP锁存器的正常波形和在故障注入后的波形图。

Figure 5 Simulation results of MKEEP in the error-free case图5 MKEEP无故障注入下的仿真波形图

Figure 6 Simulation results of MKEEP in the error case图6 MKEEP故障注入下的仿真波形图

这里依据上面节点恢复的分析,对锁存器进行故障注入实验。根据上文中举例的情况进行波形仿真实验,闪电标志的地方代表上述情况中受到粒子辐射的节点。从图6可以看出,无论是双节点翻转还是三节点翻转,MKEEP锁存器都能很快地将错误的逻辑值恢复至原本的正常状态。

4 效能评估

为了进一步评估锁存器的效能,本文要进行可靠性、面积、延迟和功耗的测试和比较(延迟是指输入D到输出Q的传输延迟,功耗为平均功耗)。将MKEEP锁存器与LCHR(Low Cost and Highly Reliable radiation latch)[10]、DNCS(Double Node Charge Sharing SEU tolerant design)[11]、NTHLTCH(Non-Temporally Hardened LaTCH)[12]、Delta_DICE[13]、DONUT(DOuble Node Upset Tolerant latch)[14]、TNU_LATCH(Radiation hardened LATCH for TNU)[15]、LCTNURL[16]、TNUHL_DICE[17]、TNURL[18]、TNUHL[19]和LCTNUT[20]锁存器在相同的条件下进行仿真比较。仿真环境为:使用HSPICE仿真软件,32 nm工艺库,电压为0.9 V,温度为27 ℃,时钟信号为500 MHz。

表1列出了以上所说的各种锁存器对单节点和多节点翻转的容忍自恢复能力。其中达到三节点翻转容忍并自恢复的锁存器是LCTNURL、TNURL_DICE和TNURL。而LCTNUT和TNU_LATCH只拥有对三节点翻转容忍的能力。

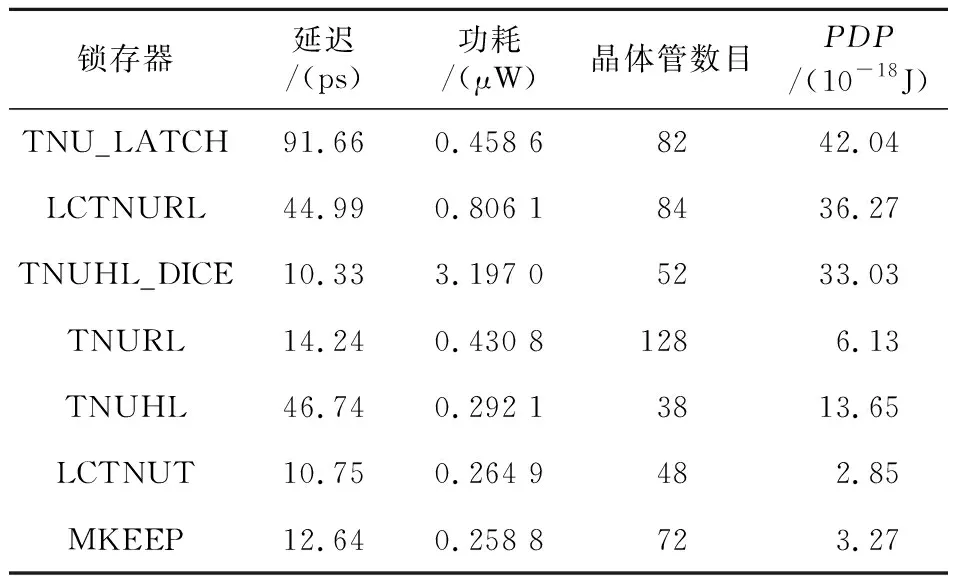

表2中给出了各锁存器的延迟功耗仿真结果。除了延时功耗外,还有一个重要因素就是平均延时和平均功耗的乘积值,一般称作PDP(Power- Delay-Product),最后一列就是锁存器对应的PDP值。PDP的计算公式如式(1)所示:

Table 2 Power consumption,delay and PDP of each latch表2 各锁存器的功耗、延迟和PDP

PDP=Power×Delay

(1)

其中,Power表示功耗,Delay表示延迟。

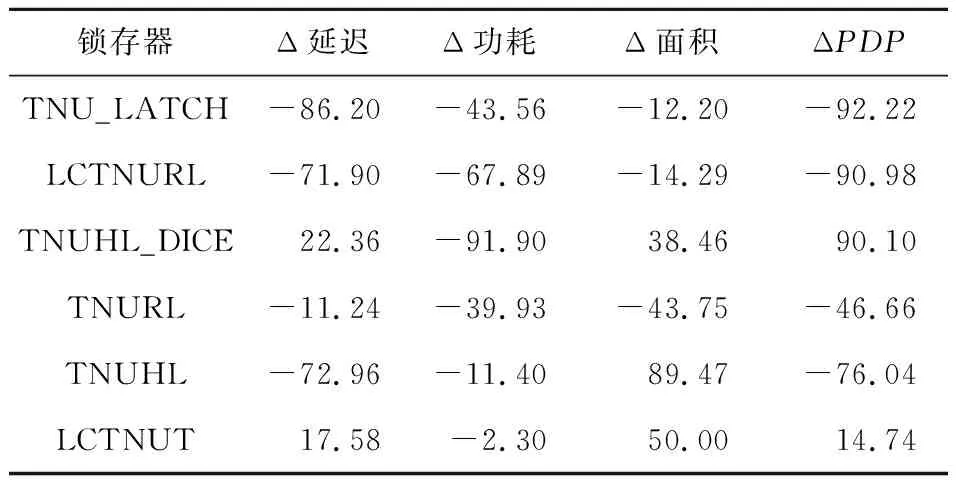

为了更详细地比较,需要进行锁存器之间的相对开销计算,如式(2)所示:

Δ=(ProposedLatch-

ComparedLatch)/ComparedLatch

(2)

其中,ProposedLatch表示本文结构在表3中对应的数值,ComparedLatch表示列举出的锁存器在表3中对应的数值。

从表3可以看出,MKEEP锁存器在功耗和延迟上相比其他锁存器具有优势。如果在表3中单独进行对比,功耗和延时比较占有优势的就是LCTNUT锁存器,但是此锁存器只能容忍三节点翻转,却无法自恢复。而本文提出的MKEEP锁存器却可以完全容忍三节点翻转并且自恢复。与其他三节点翻转自恢复的锁存器相比,MKEEP锁存器在晶体管的数量上减少了,这会降低面积开销。

Table 3 Cost comparison of MKEEP and other latches表3 与其他锁存器的成本比较 %

Figure 7 Results of each latch in PVT experiments图7 各锁存器在PVT实验下的结果

5 PVT波动实验分析

随着CMOS电路的相关工艺技术飞快发展,晶体管的特征尺寸不断地减小,这也成为了锁存器对PVT变化敏感的重要因素。为了进一步检验锁存器的稳定性,使用HSPICE仿真软件对MKEEP锁存器进行合理的PVT(Process- Voltage-Temperature)分析也很重要[21,22]。

PVT实验工艺分为5个类型:TT(典型NMOS、典型PMOS)、FF(快速NMOS、快速PMOS)、SS(慢速NMOS、慢速PMOS)、FNSP(快速NMOS、慢PMOS)和SNFP(慢NMOS、快PMOS)[23-25]。本文将电压设从0.75 V~1.25 V,间隔是0.05 V。温度变化则在-25 ℃~125 ℃。

经过PVT的仿真实验,最后得到了图7所示的折线图。图7a与图7b、图7c与图7d、图7e与图7f分别是在温度、电压和工艺的变化下,本文设计的锁存器与参考锁存器在实验中功耗和延迟的相关数据组成的折线图。从图7a和图7b中可以看到,随着温度的升高,锁存器延迟整体在升高,而功耗则是整体下降。MKEEP锁存器功耗保持稳定而且数值较小,延迟上升的幅度基本上没有变化。

图7c和图7d表示的是锁存器对电压变化的敏感度。依据电路中功耗和电压的定律公式,随着电压的升高,锁存器的功耗会升高;但是,随着电压升高,电阻相对不变,整个锁存器的电流就会增加,于是锁存器的延时便会降低。从折线图中可以看到,某些参考的锁存器在电压变化的情况下,功耗和延迟的变化都是非常明显的;而本文设计的MKEEP锁存器对电压变化的敏感度较低。

图7e和图7f表示工艺的变化对锁存器的影响。从图中可以看出,每种锁存器的功耗在工艺FF中达到最大,在工艺SS中则是最小。延迟则是与之相反。图中功耗和延迟越曲折,代表锁存器越容易受到工艺的影响。从实验的结果来看,MKEEP锁存器受到工艺变化的影响较小。

6 结束语

随着半导体集成电路技术的进步,高能粒子轰击锁存器造成的TNU变得更为严重。与此同时,大多数现有的锁存器对三节点翻转和自恢复的效果并不是很理想。为了解决这些问题,本文设计了一种高性能、低功耗的三节点翻转自恢复的锁存器MKEEP。通过HSPICE仿真实验表明,相比于其他三节点翻转容忍或者自恢复的锁存器,本文所提出的MKEEP在面积开销、功耗、延迟和PDP上具有明显的优势。从PVT测试实验结果也可以看到,MKEEP锁存器相比于其他的锁存器表现得更加稳定,受环境条件的影响较小。因此,MKEEP锁存器是一种非常具有竞争力的锁存器。