基于FPGA的8B/10B编解码IP核设计

2024-01-23周爽,周莉

周 爽,周 莉

(1.中国科学院国家空间科学中心,北京 100190;2.中国科学院大学计算机科学与技术学院,北京 101499)

0 引言

为了解决航天器内电缆布局困难、发射成本增加的问题,采用8B/10B编码技术将数据和时钟合并传输,有效减少点对点高速数据传输时的电缆数量,克服传输过程中产生的时钟与数据抖动问题,提高传输效率,并且利用8B/10B编码技术的检错功能,采用冗余的方式实现误码检测,提高系统抗辐射性能[1-2]。

目前针对LVDS的8B/10B编解码的实现主要是基于FPGA的8B/10B编解码IP核或外加串行/解串芯片、驱动芯片、均衡芯片。前者受到版权限制,具有不可移植、代码不透明、资源占用高等缺点,在航天任务工程应用时受到很多约束。后者需要增加多个芯片的硬件电路,增加了电路板面积和成本。因此研发基于FPGA的自主可控可移植的8B/10B编解码IP核是十分必要的。

本文面向航天器数据传输的8B/10B编解码应用需求,设计了一个基于FPGA的8B/10B编解码的IP核。模块化实现8B/10B编解码,并将查找表存储在Verilog源文件中,除时钟外都是逻辑设计,使系统移植性好、灵活性高;在接收端选取同频多相采样方法实现时钟与数据的恢复,提高传输速率,降低对FPGA工作频率的要求。

1 系统设计

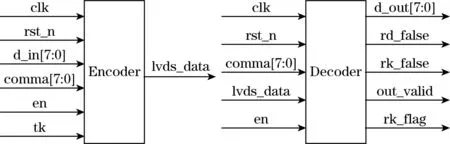

针对IP核设计的通用性、可配置、易操作、易移植、接口时序明确等需求,本文提出的8B/10B编解码IP核设计的接口信号如图1所示。

图1 编解码模块接口信号

IP核对数据字符和控制字符进行统一编码和解码,编码模块设置了指向数据字符或控制字符的标志(tk)、comma字符(comma),解码模块设置了使能位

(en)、数据字符译码错误(rd_false)、控制字符译码错误 (rk_false)等状态指示。

系统逻辑设计包括编码模块、解码模块、可靠性设计3个部分。

1.1 编码模块设计

编码模块设计如图2所示,输入数据经过一个9 bit位宽的FIFO,实现数据跨时钟域的传输,其中高8位是有效字符,最低位为标志位,用于匹配写入端和读出端的时钟;encoder模块编码采用分组查找表的方法,将有效字符分为数据字符和控制字符实现编码;再经deserdes模块将数据串行输出。

图2 编码模块设计框图

编码模块的实现需要满足编码规范,考虑编码技术对直流平衡及转换密度的要求。直流平衡要求编码后的数据呈中性,即“0”和“1”的数量相等。3 bit数据有8种取值情况,编码为4 bit时只有6种取值情况满足条件。同理,5 bit数据有32种取值情况,编码为6 bit时只有20种取值满足条件[5]。故引入RD(running disparity,极性偏差)表示这组数据的不平衡度,其中RD+表示“1”的数量比“0”的数量多2个,RD-表示“1”的数量比“0”的数量少2个[6-7]。转换密度则要求编码后的比特流不存在连续的5个及以上的“0”或“1”。

本系统中,数据字符编码时进一步将数据分为5 bit、3 bit,遵从极性平衡和编码后的数值(即6 bit、4 bit)交替2个要求实现编码,逻辑框图如图3所示。

据工信部安排,目前已有多家化肥生产企业参与产品追溯体系建设试点。2018年4月19日,全国化肥电子防伪追溯体系服务平台正式上线,已具备企业接入条件。试点的顺利推进及全行业的推广亟需《化肥追溯体系规范》标准作为准则和指导。

图3 数据字符编码逻辑框图

编码时3种极性状态分别为:“00”表示当前状态平衡,“01”表示当前状态为RD-,“11”表示当前状态为RD+。初始输入极性状态为RD-。编码时5B编码模块和3B编码模块实现极性交替和6 bit、4 bit数据的交替。控制字符无需划分5 bit、3 bit,但仍需遵从编码要求。

当极性状态更换规则与编码直流平衡要求相悖时,优先解决连续的5个及以上的“0”或“1”出现的问题,并在接下来的编码过程进行极性补偿。

编码单元接口时序图如图4所示,编码输出有3个时钟的延时,延时固定。

图4 编码模块接口时序图

1.2 解码模块设计

8B/10B解码模块通过时钟与数据恢复(clock and data recovery,CDR)技术从串行数据中正确提取时钟信息,再利用恢复的时钟正确采样接收数据,实现数据恢复。CDR的拓扑结构主要有3种方法:基于反馈相位跟踪的CDR、基于无反馈的过采样型CDR和基于突发模式的CDR[8-9]。过采样方法根据采样时钟的不同可以分为时域过采样和空间过采样2种方法。时域过采样法直接采用传输数据的n倍频率时钟对数据进行过采样,采用4~5倍过采样时FPGA的最高运行速率会限制8B/10B的通信速率,故本系统采用同频多相的空间过采样的方法实现时钟与数据恢复。

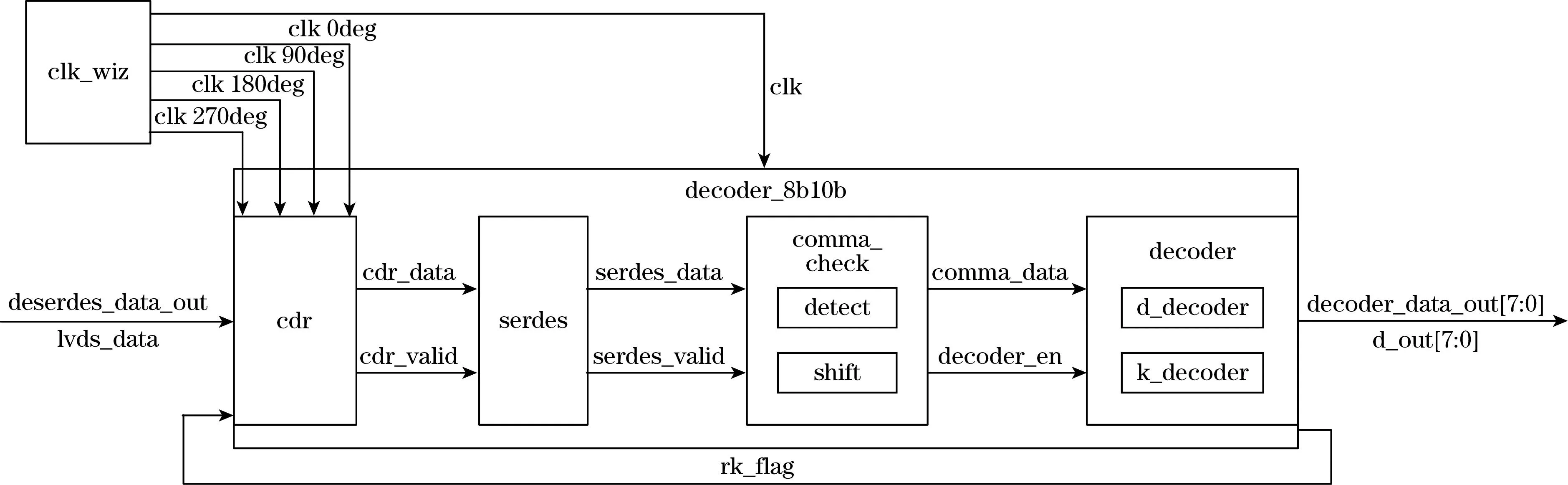

如图5所示,解码流程分为4个功能单元,分别为时钟与数据恢复单元cdr、串并转换单元serdes、comma码检测单元comma_check、译码单元decoder。接收端接收到的比特流首先进入cdr模块进行数据恢复,恢复后的数据进入serdes模块实现串并转换,之后进入comma_check模块,找到comma字符,即传输数据中的字符边界起始端,再将重排后的10 bit送入解码单元;最后经过decoder解码模块实现数据字符和控制字符的解码。

图5 解码模块设计框图

利用FPGA的时钟管理模块DCM产生4路与数据速率同频的时钟,相位分别为0°、90°、180°、270°。cdr模块在一个码元周期内利用这4路时钟对接收数据实现4次采样,采样示意图如图6所示。将采样结果记录在寄存器中,在下一个周期的0°相位的时钟上升沿到来时将本次4个采样结果记录在寄存器data_reg[3:0]中,通过对采样结果的处理判断最佳相位从而恢复数据。

图6 数据采样示意图

同频多相过采样法是异步传输,理论情况下恢复数据的最佳相位是不变的,但由于采样时钟的偏差和抖动,数据最佳采样相位发生变化,所以需要定时进行调整。本IP核采用的方法是在总线空闲或者数据包间发送comma码时重新检测数据最佳相位,以消除累积误差。数据包间发送comma码时,检测到第1个comma码时,进入检测最佳采样位置的状态机,根据采样值确定当前最佳采样位置,选择对应时钟的采样值进行串并转换。调整最佳采样位置需要2个字节的时间,数据包间发送的comma码需要大于2。

comma_check模块包括2部分功能单元:用于检测comma的detect单元;用于重新对齐数据的shift单元。comma_check模块的检测逻辑设计如图7所示,同步的comma码默认是K28.5,也可配置。

图7 comma_check模块功能结构设计图

对齐后的待解码10 bit数据根据标志位进入d_decoder或k_decoder单元,采用查找表的方法进行译码,每组字符都需按流程完成解码。解码单元接口时序图设计如图8所示,解码输出有1个时钟延时,延时固定。

图8 解码模块接口时序

1.3 可靠性设计

8B/10B编码技术具有强检错能力。8B/10B编码将268种有效的8 bit数据字符和控制字符转换为10 bit,共有1024种不同的取值,但有效码仅有536种,通过检测冗余,即接收到的字符是否有效来判断是否存在错误的传输。同时,传输数据中频繁的电平变化,也有利于降低误码率。还可以通过特殊字符的定义实现信息识别定位,快速找到误码位置。本系统在解码端产生rk_false、data_3b_false、data_5b_false等解码错误标志和字符有效标志,用于报告上位机,提高了数据传输的可靠性。

按数据包传输时,若采用50 ppm(1 ppm=10-6)的晶振,那么累积错位1 bit的长度为106/50=20 000 bit,根据8B/10B编码规则,最多保证传输2000字节。建议传输包长在1024字节以内,数据包之间传16个以上K码,便于解码端调整至最佳解码状态,并在总线空闲时发送K码。

2 试验验证

使用Modelsim仿真验证后,用2块FPGA作为硬件平台验证IP核,其中发送端FPGA型号为xc5vsx95t,接收端FPGA型号为xc4vsx55,二者通过LVDS电平进行数据传输,通信速率为80 Mbps。

通过添加ILA核实时显示测试结果。测试时,发送端发送FFFF个数据包,每个数据包中包含1024组顺序码数据,数据包间发送20组comma码,在接收端查看正确数据组数及各种标志位输出。如图9所示,其中cnt_state指示接收数据最佳相位点,data_out输出解码后的数据,data_right_cnt记录正确传输数据的数量。如图10所示,数据包已经全部完成传输,接收到的即为comma码,正确传输数量为3FFFC,等于FFFF×(1024)10,传输无错误,且其余标志位均显示无错误。此外,IP核还经过xc5vsx95t、K7325T的FPGA板的测试,传输也无错误。

图9 误码率测试结果示意图1

图10 误码率测试结果示意图2

3 结论

本文设计基于FPGA的8B/10B编解码的IP核,除解码四相位时钟的时钟模块外均为逻辑设计,采用分组查找法进行编解码,冗余和容错措施保障数据传输,接收端采用同频多相的过采样方法实现时钟与数据的恢复,具备移植性好、运行速率高、可靠性强的优点。IP核接口设计合理,可以根据用户应用需求进行配置,更改comma码、时钟配置等,适用性强。通过对IP核的仿真测试和误码率测试,验证了IP核设计的有效性和可靠性,满足航天设备数据传输的可靠性要求。