基于Innovus 的局部高密度布局规避方法

2024-01-17李应利王淑芬

李应利,王淑芬

(中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

0 引言

随着集成电路产业的快速发展,先进工艺节点不断变小,芯片集成度不断提高,芯片规模越来越大,这样的快速发展为数字集成电路后端设计提出了新的挑战。数字芯片设计过程中需要考虑的因素很多,其中,时序收敛是至关重要的。布局布线(PR)是数字集成电路后端设计中占比最大的工作,包括版图布图规划(FP)、标准单元布局、时钟树综合(CTS)、布线及时序优化等若干步骤[1]。标准单元布局是指通过电子设计自动化(EDA)工具,采用自动布局方法,根据逻辑相关性及时序要求,将标准单元放置在内核区域的过程。布局后若局部标准单元密度过高,会对后续布线和时序优化有很大的影响。当布线阶段存在大量拥挤问题时,需要返回到布局阶段重新调整布局,这个过程一般需要循环多次;在时序优化阶段,由于布局问题导致工具无法修复时序时,也需要重新调整布局。因此,在标准单元布局阶段就需要考虑到版图是否存在局部标准单元密度过高的问题。

Cadence 公司的Innovus 是PR 常用的工具,不仅可以实现布局和布线,还可以在不同阶段进行时序优化,但对于后续时序优化,会存在由于局部标准单元密度过高导致工具无法修复的情况。本文以UMC 28 nm 工艺模块级芯片为例,芯片规模为370 万门,时钟频率为780 MHz,使用Innovus 中标准单元布局阶段的两个设置命令,解决了局部标准单元密度过高的问题,并对比分析了两种方式对时序优化的影响。

1 局部高密度标准单元

标准单元布局是集成电路PR 中必不可少的步骤,大量标准单元的放置一般使用工具自动布局的方法,布局后可通过工具查看标准单元的分布情况。使用Innovus 测量得到的标准单元密度分布如图1 所示,以边长为10 个标准单元高度的正方形将芯片划分成无数个小方块,以不同颜色表示标准单元的密度分布;小方块内标准单元总面积占小方块面积的比例即是标准单元密度,此比例越大,表明标准单元密度越高。局部标准单元密度过高会导致PR 后续出现一系列问题,无法达到芯片时序和绕线等的要求。

图1 标准单元密度分布

局部高密度标准单元对时序、绕线和IR Drop 的影响如下。

1)时序检查是芯片设计中必不可少的部分,主要分为建立时间检查和保持时间检查。建立时间是指在触发器的时钟信号上升沿到达之前数据稳定不变的时间,若建立时间不够,数据将不能在这个时钟上升沿被稳定地打入触发器;保持时间是指在触发器的时钟信号上升沿到达之后数据稳定不变的时间,若保持时间不够,数据同样不能被稳定地打入触发器[2]。布局的后续流程是CTS,CTS 之后会对建立时间和保持时间进行优化。保持时间的优化方式通常是在数据路径上通过插入缓冲单元或反相器单元增加延迟[3],所以在优化保持时间违例时可能需要占用一定的芯片空间,而标准单元的密度过高会导致在优化保持时间违例时,工具无法插入缓冲单元或者反相器单元,导致一些保持时间违例无法被完全修复。

2)局部高密度标准单元区域通常会出现大量的绕线,工具在该区域进行绕线时,可能引起布线拥堵,甚至影响布线效率[4]。同时,由于实际布线与预计绕线路径有差异,会使绕线距离更长,增加连线负载和连线延迟,导致时序变动甚至无法收敛。局部高密度标准单元还可能在绕线时存在局部较严重的拥塞,导致绕线无法正常绕通,而出现短路问题[5]。

3)动态IR Drop 是电路开关切换时电流波动引起的电源电压压降[6]。标准单元布局一般是将有逻辑关系的单元靠近放置,单元密集的地方逻辑门单元较多,如果连接到金属连线上的逻辑门单元同时翻转,将会导致IR Drop 较大,所以标准单元密度过高会导致该区域的IR Drop 相对较大。

局部高密度标准单元不仅对绕线、IR Drop 和时序有影响,还会影响后续时钟转换时间和串扰的修复。因此,在标准单元布局阶段,应避免局部高密度标准单元的存在。

2 PR 自动化流程

在数字集成电路PR 流程中,布局设计将影响到芯片的面积、速度、信号完整性和设计周期,一个好的布局将大大减少后续布线以及时序收敛所耗费的时间和精力[7]。Innovus 是Cadence 公司的一体化PR 工具,它可以实现从FP、布局、CTS 到绕线的整个流程,完成从输入网表到输出GDS 的全部功能,且在不同阶段可进行时序考虑和优化[8]。本文通过脚本语言将Innovus 整个后端流程串起来,实现全自动化运行。PR自动化流程如图2 所示,将FP 结果输入后,整个流程依次为PreCTS、CCOPT、PostCTS、PostCHD、PostR 和PostRHD,最后输出数据,其中PostRHD 可迭代多次修复保持时间。

图2 PR 自动化流程

本文基于UMC 28 nm 工艺设计的高速数字模块芯片仅作为层次化芯片的一部分。该模块芯片初始读入数据有94 万标准单元,时钟频率为780 MHz。在最初版中,将优化好的FP 数据输入PR 自动化流程,其中PostRHD 步骤迭代两次。整个流程结束后,最终时序报告结果表明保持时间违例没有被完全修复。虽然PostCHD 和PostRHD 阶段对保持时间进行了多次优化,但依然存在没有完全优化的情况,PostCHD 和PostRHD 的log 表明,以上情况主要是由于没有足够的空间用于修复保持时间违例造成的。PostCHD 的log 部分信息如图3 所示。打开Innovus 查看PostCTS版图,存在局部高密度标准单元拥堵问题,经分析是由于PreCTS 后局部单元密度偏高,且经过时序优化和CCOPT 后单元数量增大,局部单元密度更大,导致后续无法通过插入缓冲单元进行修复。

图3 PostCHD 的log 部分信息

2.1 局部高密度布局问题解决方案

为了解决PreCTS 阶段局部标准单元密度高或者布线拥堵的问题,通常需借助partial placement blockage[9]。Partial placement blockage 是在预计标准单元密度高的某一区域设定标准单元的利用率,需要在摆放标准单元之前在标准单元密集的区域加上partial placement blockage,该方法存在以下缺点:需根据不同版本改变partial placement blockage 所加的区域;会导致partial placement blockage 周边区域单元密度偏大。

本文在PreCTS 阶段使用setPlaceMode 设置的setPlaceMode-place_global_uniform_density true 和setPlaceMode-place_global_max_density value 两种命令避免了单元密度过高的情况,全局使用这两种命令可避免使用partial placement blockage 带来的问题。

单元均匀分布法:在后端自动化流程PreCTS 阶段的脚本中加上setPlaceMode-place_global_uniform_density true 命令,其他设置保持一致。该命令默认为false,本文将其设置为true,可使利用率低于70%的设计实现均匀的单元分布。

控制最大密度法:在后端自动化流程PreCTS 阶段的脚本中加上setPlaceMode-place_global_max_density value 命令,其他设置保持一致。该命令是控制全局单元摆放过程中的最大密度,value 的使用值范围为0~1,可根据需求自由调配,本文使用的值是0.55,表示标准单元布局阶段单元摆放的最大密度为55%。

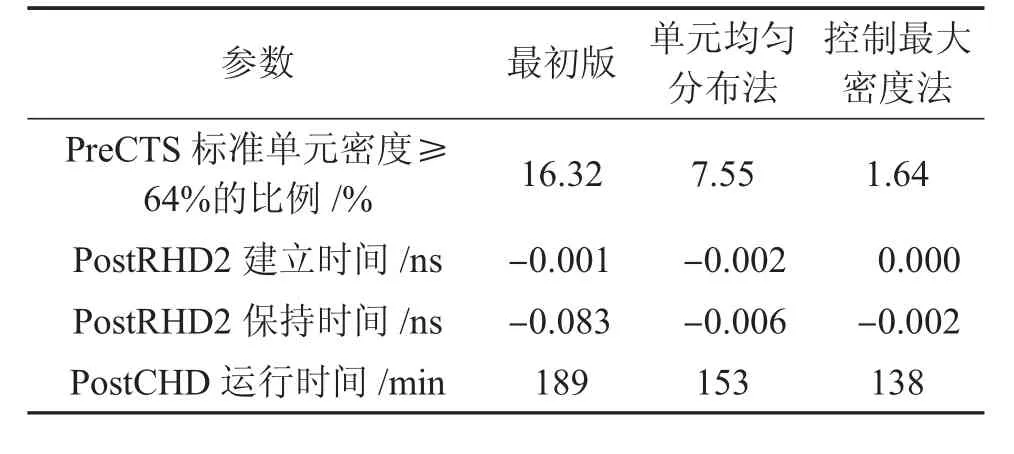

2.2 结果对比分析

控制芯片面积不变,对通过后端自动化流程完成的三种结果进行对比分析。最初版PreCTS 密度分布如图4(a)所示,可以看出最初的版图中虽然左上方有空余的空间,但版图中依然会存在密度过大的区域,说明扩大面积并不是解决局部标准单元密度高的关键。最初版PostCTS 单元密度分布如图4(b)所示,整体密度分布和PreCTS 结果基本保持一致,但高密度区域在此阶段会扩大,所以在PreCTS 阶段分布好标准单元的密度是必要的。

图4 不同方法单元密度分布

单元均匀分布法和控制最大密度法的PreCTS 单元密度分布如图4(c)(d)所示,从图中可以明显看出,加setPlaceMode 命令的两种PreCTS 的版图中单元分布相对均匀,且红色区域很少,即很少存在局部标准单元密度很高的情况,尤其是在控制最大密度法的版图中单元分布更加均匀,密度主要在50%和60%之间,更有利于完成后续的自动化流程。两种方法的结果对比如表1 所示,可见控制最大密度法的PreCTS标准单元密度≥64%的比例由最初版的16.32%降至1.64%,低密度有利于后续流程中的时序优化,而且从表中可以看出,两种方法比最初版的时序有明显的改善,PostCHD 和PostRHD 中也不存在最初版中没有空间余量的问题。控制最大密度法在保持建立时间没有变差的情况下,保持时间违例基本可以修复完全,且PostCHD 的运行时间最短,比最初版的时间缩短26.98%。由表1 可知,控制最大密度法效果更佳,所以对该方法进行动态IR Drop 检查,得出其最终的动态IR Drop 比最初版下降了8.85%。综上所述,控制最大密度法的整体效果最好,无论是从标准单元的密度分布,还是对保持时间违例的修复和动态IRDrop 都更优。

表1 两种方法的结果对比

3 结论

本文采用UMC 28 nm 工艺,基于Innovus 后端自动化设计流程,实现了从FP 输入到GDS 数据输出的PR 过 程 , 在 PreCTS 阶 段 分 别 使 用setPlaceMode-place_global_uniform_density true 和setPlaceMode-place_global_max_density value 两种命令设置,减少局部高密度标准单元的存在,避免在自动化流程中影响保持时间违例的修复。结果表明,setPlaceMode-place_global_max_density value 设置由于可以控制最大密度的比例,可以有更好的调控性,不仅可以解决由于局部标准单元密度过高导致保持时间违例无法正常修复的问题,实现保持时间违例优化,而且PostCHD 的运行时间缩短了26.98%,动态IR Drop 降低了8.85%。