端口双向耐高压电路的ESD 防护设计技术

2024-01-17邹文英李晓蓉杨沛周昕杰高国平

邹文英,李晓蓉,杨沛,周昕杰,高国平

(中科芯集成电路有限公司,江苏 无锡 214072)

0 引言

静电放电(ESD)是影响集成电路可靠性的主要因素之一,集成电路设计者需要高度关注的一个焦点问题就是ESD 防护设计[1]。随着CMOS 工艺特征尺寸的不断减小,工艺、器件、电路以及系统等各个层面的因素都会对ESD 防护设计产生巨大影响[1],ESD 防护设计与电路的相关性越来越强,电路设计者也面临更大的挑战,需要从全芯片的角度来优化ESD 防护设计,才能保证电路的可靠性[2-4]。

本文提出的全定制32 路总线接口电路采用0.35 μm CMOS 工艺,衬底材料采用P 型硅,外延层厚度为7 μm。本文重点阐述了芯片中双向耐高压输入引脚的ESD 防护设计技术,并介绍了全芯片ESD 防护的设计技术。双向耐高压输入引脚采用创新性的双向耐高压二极管的器件结构,此结构既能使端口电压在-10~10 V 变化时电路正常工作,又能快速泄放ESD电流。相较于其他的双向耐高压结构,此结构抗闩锁能力强,和工艺的匹配度高,设计和制造都容易实现。该电路通过了4.0 kV 人体模型(HBM)ESD 测试,具有较好的ESD 防护性能。

1 双向耐高压输入管脚的ESD 防护设计

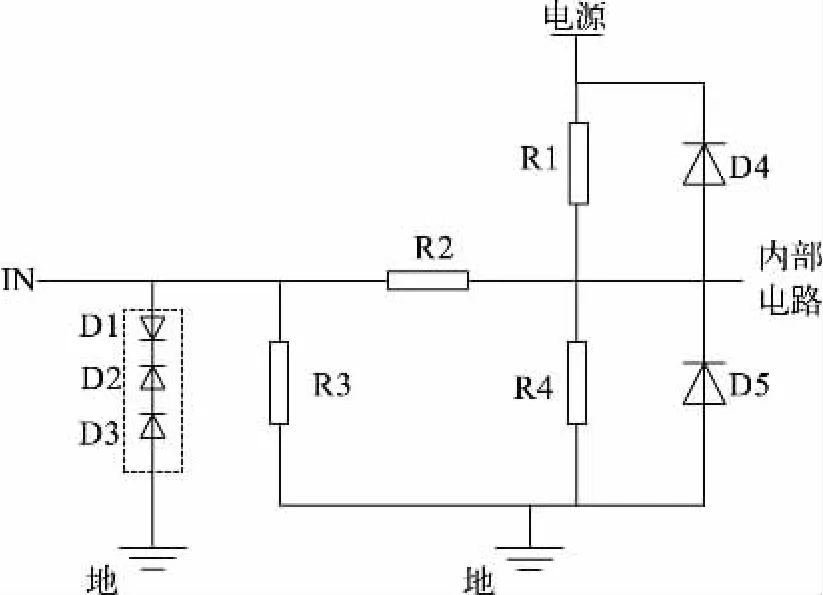

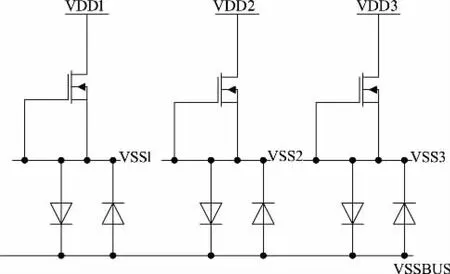

32 路总线接口电路中包含16 路接收电路,接收电路的差分输入管脚端口电压在-10~10 V 变化,图1为双向耐高压输入管脚的电路图,设计中采用电阻分压网络,使端口可以接受负压,并扩大输入范围,这样输入端口电压在-10~10 V 变化时,经过电阻网络R1、R2、R3 和R4 后的电压始终在0.59~2.69 V 内变化。图1 中D1、D2 和D3 为双向耐高压二极管,其中D1 的击穿电压约为17 V,D2 和D3 的击穿电压为8.2 V,形成一级ESD 防护;R2 为10 kΩ 的多晶限流电阻,保护内部电路不受损伤;D4 和D5 是普通器件结构的二极管,泄放流过限流电阻的ESD 电流,构成二级ESD 防护。当给端口施加正向脉冲时,D1 导通,D2 和D3 反向击穿,通过D1、D2 和D3 泄放ESD 电流,其中D2和D3 的累加击穿电压为16.4 V;当给端口施加负向脉冲时,D2 和D3 导通,D1 反向击穿,ESD 电流通过D3、D2 和D1 进行泄放。这样既能保证端口电压在-10~10 V 变化时电路正常工作,又实现了ESD 防护功能。

图1 双向耐高压输入管脚的电路图

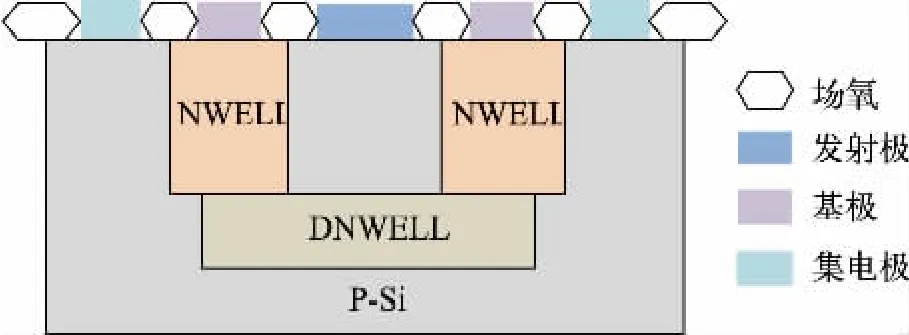

在外界静电到来时,ESD 防护器件需要迅速响应,及时泄放ESD 电流,同时不能影响芯片正常工作。然而,很多接口电路需要同时在正向高压和负向高压下工作。若端口工作电压远低于施加在ESD 防护器件上的电压,并且施加电压方向为正负双向时,ESD 防护器件必然会在其中一个电压方向上出现漏电。针对上述问题,结合CMOS 制造工艺,设计了一种特殊的ESD 保护器件结构,能够耐双向高压,图2 为双向耐高压的ESD 防护器件结构剖面图[5]。

图2 双向耐高压的ESD 防护器件结构剖面图

图2 中,把NWELL 和DNWELL 连接成封闭的环形区域,能够成功地将原本是一个整体的P 型衬底分割成两个相互独立的低浓度区域,达到耐双向高压的目的。然后在中间的独立区域中进行第一高浓度注入,把第一高浓度注入区域作为三极管PNP 的发射极。同时,在NWELL 区域进行第二高浓度注入,与发射极形成PN 结,NWELL 和DNWELL 封闭环形区域一起作为三极管PNP 的基极。当电压触发ESD 器件时,基极电流使三极管PNP 导通,达到静电泄放的目的。在P 型衬底上进行第三高浓度注入,把第三高浓度注入区域作为PNP 三极管的集电极。使用场氧将上述三个高浓度P 型注入区分别隔开[5]。

在进行ESD 防护器件版图设计时,将器件设计成多指状结构,均匀对称放置,保证释放电流的均匀性,图3 为多指状防护器件版图[6-7],图中绿色区域为DNWELL,紫色区域为NWELL,其他区域为P-Si。

图3 多指状防护器件版图

2 全芯片ESD 防护技术

2.1 ESD 防护器件设计

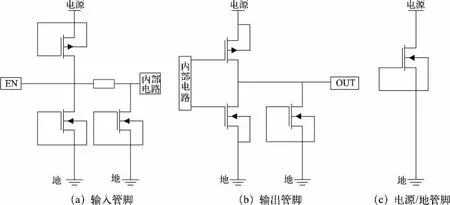

根据目标工艺,为本文的全定制32 路总线接口电路设计有效的ESD 防护器件,构建ESD 电流泄放通路。电路管脚分为双向耐高压输入管脚、输入管脚、输出管脚、电源管脚以及地管脚5 种类型,图4 为各类管脚器件结构图。

图4 各类管脚器件结构图

输入管脚采用GDPMOS(Gate-to-Drain PMOS)和GGNMOS(Gate-Grounded NMOS)实现两级保护[8]。靠近输入管脚的位置采用GDPMOS 作为ESD 一级防护,并且在输入信号路径上添加约200 Ω 限流电阻,阻止ESD 电流流入内部电路。在内部电路附近采用GGNMOS 进行ESD 二级防护,以泄放流过限流电阻的ESD 电流,降低到达内部晶体管栅极的ESD 电压。

一般对于输出引脚的电压钳位要求相对来说不会很严格,主要是因为输出引脚直接与输出缓冲晶体管的漏极相连,而且输出阻抗不能太高,以免对电路的输出特性造成影响。输出缓冲晶体管由于电流驱动能力较强,且器件尺寸较大,可达到自保护的效果,但在版图布局时依然需要遵守设计规则中对于ESD 防护的设计要求[8]。

电源和地管脚一般采用静态电源钳位电路来实现电源总线到地总线的ESD 电流备用通路。静态钳位电路依靠电压触发,当电压达到开启电压时,钳位电路导通,泄放ESD 电流。本电路采用GGNMOS 结构,使用的元器件少,版图面积也较小,且能很好地完成ESD 防护功能。

2.2 电源地线ESD 网络设计

32 路总线接口电路包含16 位驱动器和16 位接收器。电源电压为3.3 V,为了隔离噪声,16 位接收器共电源地,每8 位驱动器共电源地,因此电源分组为VDD1/VDD2/VDD3 三个不同的电源域,地分组为VSS1/VSS2/VSS3 三个不同的域。根据HBM ESD 测试方法,该电路将面临7 种ESD 测试组合(①All-to-VDD1;②All-to-VDD2;③All-to-VDD3;④All-to-VSS1; ⑤All-to-VSS2; ⑥All-to-VSS3;⑦I/O-to-I/O),每种测试组合发生时,都需要合理的ESD防护结构以供ESD 电流泄放。

功能端口管脚都有有效的IOP(I/O Protection)防护器件[9]进行ESD 电流泄放,实现可靠的ESD 防护。同组的电源总线和地总线之间也有合适的电源钳位电路来构建电源到地的ESD 放电通路。但是,不同的电源域在片内是物理隔断的,VSS1/VSS2/VSS3 之间片内也没有金属线短接,仅通过衬底连接。实验证明,加强电源地线ESD 网络设计对于全芯片ESD 防护能力的提升有帮助,因此,在不同的电源域之间需要放置PPP(Power-to-Power Protection)结构[9],不同的地域之间需要放置合理的ESD 结构,以提高整个芯片的ESD 防护水平。

该电路的驱动器和接收器的路数较多,从隔离噪声的角度考虑,不同电源域之间没有设计ESD 防护器件。为了增强全芯片的ESD 防护能力,设计了宽度为60 μm 的VSSBUS,VSS1/VSS2/VSS3 与VSSBUS 之间分别放置头尾相连的二极管串对,将分离的地线连接起来,间接实现不同电源域之间的ESD 防护,电源总线和地总线间的ESD 器件结构如图5 所示。

图5 电源总线和地总线间的ESD 器件结构

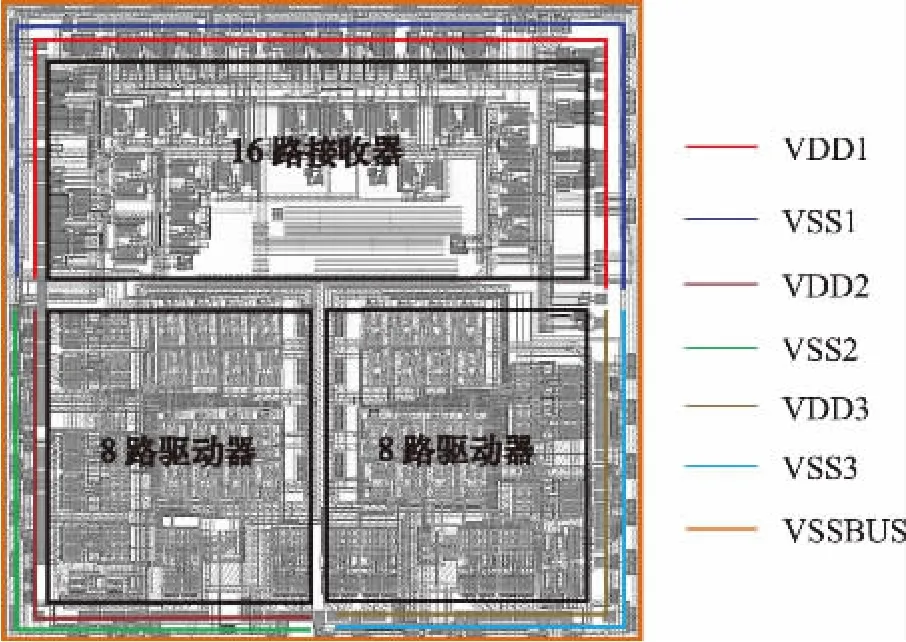

在进行电路版图设计时,16 路接收器放置在芯片的上方,由VDD1 总线和VSS1 总线供电;由于驱动器的工作电流很大,为了降低噪声,8 路驱动器放置在芯片的左下方,由VDD2 和VSS2 供电;另外8 路驱动器放置在芯片的右下方,由VDD3 和VSS3 供电。而VSSBUS 总线分布于整个芯片, 方便放置VSS1/VSS2/VSS3 总线和VSSBUS 总线之间的二极管串对,提高全芯片的ESD 性能。电源地线之间的布线网络如图6 所示。

图6 电源地线之间的布线网络

2.3 全芯片ESD 防护设计

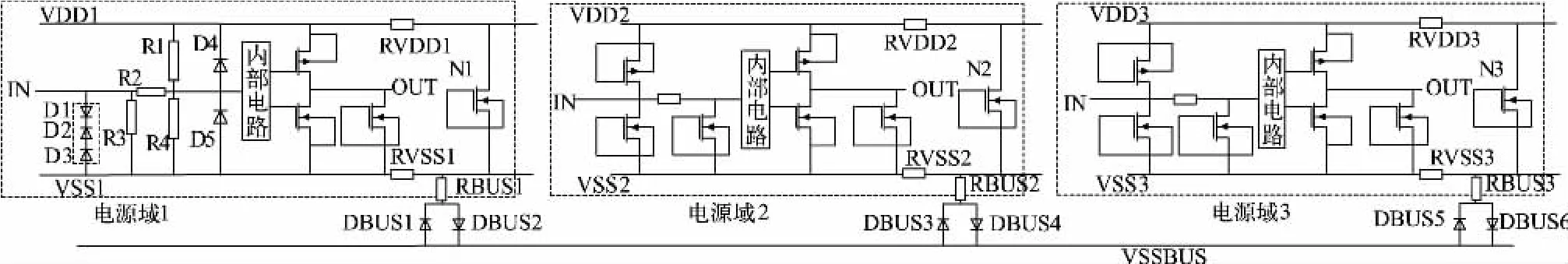

该款全定制32 路总线接口电路的全芯片ESD 防护网络如图7 所示,输入或输出管脚到电源总线上的集总寄生电阻分别用RVDD1、RVDD2、RVDD3 表示;输入或输出管脚到地总线上的集总寄生电阻分别用RVSS1、RVSS2、RVSS3 表示;VSSBUS 总线到地总线上的集总寄生电阻分别用RBUS1、RBUS2、RBUS3 表示。当在VDD1 和VDD2 之间施加正向脉冲时,ESD电流的泄放路径为VDD1→N1→RBUS1→DBUS2→DBUS3→RBUS2→N2→VDD2;当在VDD1 和VDD2之间施加负向脉冲时,ESD 电流的泄放路径为VDD2→N2→RBUS2→DBUS4→DBUS1→RBUS1→N1→VDD1。以此类推,通过电源总线、地总线和VSSBUS 总线以及I/O 管脚等部分的ESD 防护电路,再加上电源钳位电路,能够达到为任意两管脚之间提供ESD 电流泄放通路的目的[6-8]。

图7 全芯片ESD 防护网络

由图7 的分析可知,将ESD 电流泄放通路上的集总 寄 生 电 阻 RVDD1、RVSS1、RBUS1、RVDD2、RVSS2、RBUS2 等尽量减小,能够大幅提升全芯片ESD 防护能力。基于此原则,电路在管脚排列过程中,尽量设计多的电源和地管脚;电源总线和地总线的版图设计需要每隔约1 000 μm 放置电源钳位电路,在VSSBUS 总线上也每隔约500 μm 放置二极管串对[10];三组电源总线、地总线以及VSSBUS 总线采用较宽的金属线,通过上述版图设计方法既可以减小电源、地总线上的寄生电阻,也可以使电源、地总线承受较大的电流,防止电迁移。

3 测试结果与分析

全定制32 路总线接口电路采用0.35 μm CMOS工艺流片,设计要求电路的HBM ESD电压不小于2 000 V。

该电路流片后差分输入管脚功能正常,ESD 器件结构不影响内部电路的正常功能,电路功能和性能满足要求。对3 颗样品电路进行了HBM ESD 测试,测试结果如表1 所示。

表1 电路HBM ESD 测试结果

测试起始电压为2.0 kV,步进为0.5 kV,当ESD测试电压增加到4.5 kV 后,对ESD 试验后的3 颗样品电路进行功能和性能测试,其中2#样品部分管脚的输入高电平漏电流变大,由ESD 试验前的0.1 μA 变大到1 μA 以上,超出规范值1 μA,表明部分管脚对地漏电超标失效;当ESD 测试电压增加到5.0 kV 后,对ESD 试验后的1#和3#样品电路进行测试,电路静态电流由试验前的22 μA 变大到100 μA 以上,确定电源和地之间漏电超标。试验结果表明,电路通过了4.0 kV 的HBM ESD 测试,双向耐高压输入管脚和全芯片的ESD 防护技术有效可行。

4 结论

集成电路多种多样的应用环境给芯片的ESD 防护设计带来了更多的问题与挑战,需要根据不同的应用环境设计合适的ESD 器件结构。本文采用多电源域设计,从全芯片的角度系统地考虑ESD 防护架构,保证整体芯片的ESD 电流备用通路全覆盖,并构建全芯片ESD 防护网络,在保证不影响芯片正常功能和电路性能的前提下,提升整体芯片的ESD 防护能力。同时,对双向耐高压输入管脚进行ESD 防护电路的加固设计,提升了芯片的ESD 失效阈值,也为双向耐高压电路的ESD 设计提供了参考。