时钟缓冲器附加抖动分析

2024-01-17陈文涛邵海洲胡劲涵

陈文涛,邵海洲,胡劲涵

(中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

0 引言

在当今数据通信、雷达以及其他高速应用系统中,时钟抖动是决定整体系统性能的关键因素。抖动不仅会降低数据转换器的性能,而且还可能使高速数字系统产生误码[1-2]。要达到所需的系统抖动性能,一定要保持尽可能低的时钟抖动,并在整个分配网络上分配低抖动时钟源。

在系统中,一般会有多个器件需要参考时钟信号进行工作。这时,一个时钟源需要一个时钟分配网络来驱动多个器件,时钟缓冲器是这个分配网络的核心器件。时钟缓冲器用来复制时钟信号源,提供多路的匹配电平格式和更高的激励电平[3]。随着系统要求的不断提升,问题也随之而来,时钟分配网络里添加的时钟缓冲器会恶化时钟源的抖动。时钟缓冲器对时钟源抖动的恶化程度通常用附加抖动来衡量,附加抖动成为了时钟源驱动多个器件的一项关键指标[4]。

对于时钟缓冲器的附加抖动,目前业内无法通过测试直接得到,需要根据测试数据结合附加抖动公式计算才能得到,附加抖动计算公式的正确性至关重要。很多文献仅给出了附加抖动的计算公式,并没有针对公式进行推导和验证以证明其正确性。

本文从相位噪声的角度对附加抖动计算公式进行了推导证明,并通过对时钟缓冲器芯片附加抖动的实际测试,验证了附加抖动计算公式推导过程的正确性,同时帮助工程师更好地理解附加抖动的含义。结合附加抖动计算公式和实际测试,给出了时钟缓冲器附加抖动指标测试中的注意事项,以保证测试结果的准确性。

1 时钟缓冲器和附加抖动分析

1.1 时钟缓冲器

时钟发生器通常是基于锁相环(PLL)架构的时钟产生芯片[5-6],而时钟缓冲器通常是基于非PLL 的扇出型时钟芯片,是一种将一路时钟源信号通过频率复制生成多路时钟信号的器件,通常时钟缓冲器还兼具有时钟分配、格式转换和电平转换的功能。

对于需要多路时钟信号的电子系统来说,在时钟源输出端增加时钟缓冲器的方案可以有效降低系统成本,简化电路设计,为系统多个组件提供多路参考时钟。

1.2 附加抖动的定义

附加抖动就是位于时钟源(例如合成器或振荡器)与时钟接收器件之间的组件(如时钟缓冲器)所增加的噪声,即时钟线路上时钟缓冲器件本身为输入信号增加的抖动数量[2],该附加抖动可增大时钟的不确定性,导致抖动增加。

时钟源经过时钟缓冲器后,缓冲器本身的抖动会增加到时钟的内在抖动上,从而恶化整个系统时钟的抖动,这个参数定义为时钟缓冲器的附加抖动。所以,对于时钟缓冲器,附加抖动是一个关键指标,时钟缓冲器附加抖动叠加在输入信号抖动上的输出如图1 所示,时钟缓冲器输出信号的抖动是输入信号的抖动和缓冲器自身的附加抖动以某种方式的叠加。

图1 时钟缓冲器附加抖动叠加在输入信号抖动上的输出

1.3 附加抖动计算公式

时钟缓冲器本身不产生时钟信号,除非有输入信号,否则不能测量相位抖动。要显示真正的缓冲器附加抖动,在理想情况下应采用没有抖动的时钟源测量,不过,真正的时钟源总是有抖动的。

为了定性分析时钟缓冲器对于源时钟抖动的影响,首先需要测量时钟源的输入抖动和时钟缓冲器的输出抖动,然后根据时钟缓冲器的附加抖动计算式算出缓冲器的附加抖动。时钟缓冲器附加抖动JADDITIVE的计算式为

其中,JOUT为时钟缓冲器的输出抖动,JIN为时钟源的输入抖动。

假设噪声过程是随机的,而且输入噪声与输出噪声互相没有关联,附加抖动可帮助确定是否能够在时钟分配网络中添加时钟缓冲器。

1.4 附加抖动计算公式推导

随机相位抖动是在规定偏移频率范围内,积分相位噪声在时域的一种表现形式。在推导附加抖动计算公式前,需要先了解时钟信号抖动和相位噪声的关系[7]。

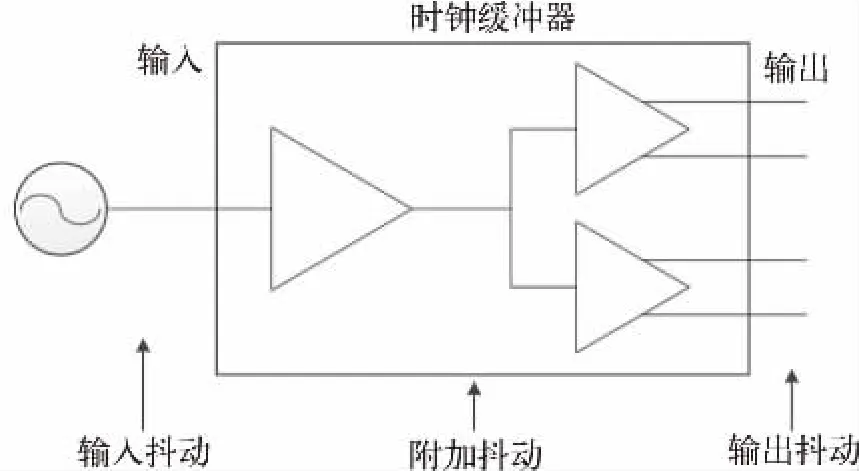

相位噪声是时钟信号噪声特性的频域表征方式,表征时钟信号频率的稳定度,是指偏离载波频率某一频率处1 Hz 带宽内噪声功率与载波信号总功率的比值,其频谱可以用L(f)来表示,单位为dBc/Hz。一个时钟信号的相位噪声频谱特性如图2 所示,从图中频谱来看,其边带会随着远离载波频率fC的位置逐渐降低,在偏离载波间隔为f-fC处时,相位噪声约等于载波频率fC处曲线的高度与频率f 处曲线的高度之差,即L(f-fC)的值。

图2 一个时钟信号的相位噪声频谱特性

与载波频率fC间隔f 处的相位噪声的频谱L(f-fC)为

其中,SC(f)为时钟信号的功率谱。

附带相位噪声的正弦时钟信号C(t)为

因为相位噪声远远小于π/2,式(3)可近似写成

其中ωC为fC的角频率。

C(t)的功率谱SC(f)为

结合L(f)的定义,得到均方根(RMS)相位抖动Jt-RMS和L(f)的关系为

附加抖动的计算公式可以从积分叠加相位噪声的角度来进行推导。式(6)是推导附加抖动计算公式的基础。

假设在偏移f"的频率范围内,LIN(f")表示时钟源的相位噪声频谱,对应的噪声功率为PIN(f")。L(f")表示时钟缓冲器引入的附加相位噪声频谱,对应的噪声功率为P(f")。LOUT(f")表示输出总的相位噪声频谱,对应的噪声功率为POUT(f")。相位噪声频谱的单位为dBc,噪声功率的单位为dBm。

为了简化后续推导,主信号归一化功率为0 dBm,根据相位噪声的定义可得,在数值上PIN(f")和LIN(f")相等、P(f")和L(f")相等、POUT(f")和LOUT(f")相等。从噪声叠加的角度,可得PIN(f")+P(f")=POUT(f"),P(f")可表示为

式(7)中的噪声功率单位为dBm,不能直接相加减计算,需先将单位dBm 转换为毫瓦(mW)进行计算。PmW(f")为对应单位为mW 的P(f"),可表示为

从而P(f")可表示为

从而得到时钟缓冲器的附加抖动相噪

将式(11)的等号左右两边分别带入式(6),可得

式(12)等号两边约去公因子,并做平方可得

根据积分线性公式,得到

式(14)等号左边为时钟缓冲器的附加抖动的平方,即

式(14)等号右边为输出总的抖动和时钟源输入抖动的平方差

上述式子从相位噪声的角度推导了时钟缓冲器附加抖动计算公式的正确性。该公式为时钟缓冲器附加抖动测试的理论基础。

2 测试验证

1.4 节从相位噪声叠加的角度证明了附加抖动计算公式的正确性。本节将通过对时钟缓冲器芯片的实际测试来验证附加抖动计算公式的推导过程。

被测时钟缓冲器是一款超高速扇出时钟缓冲器,最大工作频率为4.8 GHz,附加随机抖动典型值为27 fs@1 GHz。电路中集成两对可选差分输入端口,通过IN_SEL 引脚控制,输入端兼容直流耦合LVPECL、CML、3.3 V CMOS(单端)以及交流耦合1.8 V CMOS、LVDS 和LVPECL 输入电平。

图3 为时钟缓冲器测试环境框图。测试环境包含频谱仪、示波器、直流电源和时钟缓冲器。信号源作为时钟源给时钟缓冲器提供时钟输入信号,通过频谱仪测试信号源以及时钟缓冲器输出的相位噪声,并通过示波器测试信号源、时钟缓冲器输出的抖动[8-9]。

图3 时钟缓冲器测试环境框图

本文测试时钟缓冲器工作在1 GHz 频率下的附加抖动,根据时钟缓冲器附加相位噪声得到缓冲器的附加抖动Jt1。

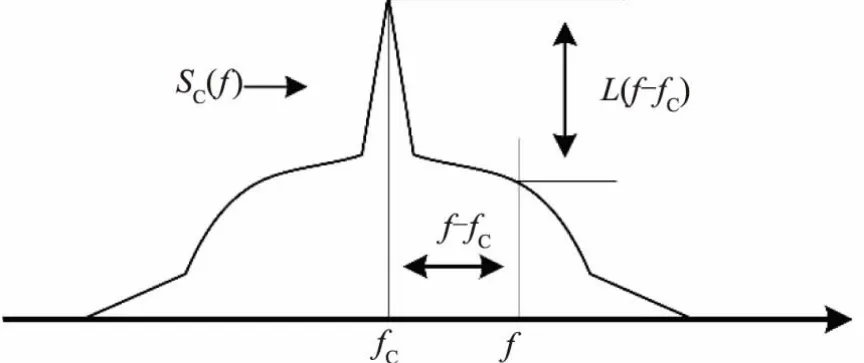

表1 为相位噪声的数据。其中第二例数值为时钟源信号在不同频率偏移处相位噪声的实测值,第三列数值为时钟缓冲器输出信号在不同频率偏移处相位噪声的实测值,第四列数值是根据式(9)计算得到的缓冲器在不同频率偏移处产生的附加相位噪声值。根据抖动和相位噪声的关系,由式(6)计算得到缓冲器的附加抖动Jt1=28.2 fs。

表1 相位噪声数据

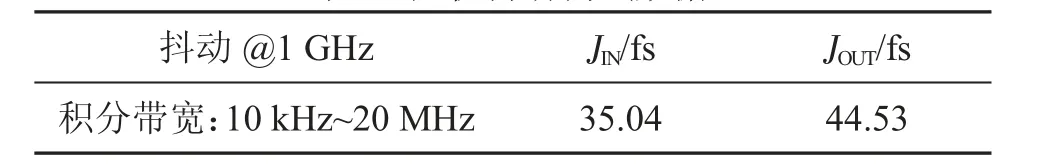

根据附加抖动计算公式得到缓冲器的附加抖动Jt2。表2 为随机抖动测试数据,其中第二列数值为时钟源信号抖动的实测值JIN,第三列数值为时钟缓冲器输出信号抖动的实测值JOUT。根据式(1)可计算得到时钟缓冲器的附加抖动Jt2=27.5 fs。

表2 随机抖动测试数据

从上面两种测试结果可以看出Jt1和Jt2相当,差异在1 fs 以内,通过实验测试验证了缓冲器附加抖动公式推导过程的正确性。

目前业内无法通过直接测试的方法来测试得到时钟缓冲器的附加抖动,只能使用间接测试的方法测试出JIN和JOUT,再通过附加抖动计算公式计算得到最终的附加抖动值,从而可以看出附加抖动计算公式正确与否在附加抖动测试中的重要性。本文通过理论推导和实际测试验证了附加抖动计算公式的正确性。

3 附加抖动测试时的注意事项

3.1 时钟源抖动的选取

从附加抖动计算公式可以看出,时钟源抖动JIN、缓冲器附加抖动JADDITIVE和缓冲器输出总的抖动JOUT之间的关系类似于直角三角形的勾股定理,三者关系见图4。在测试误差一定的情况下,需要考虑如何选取合适的时钟源来保证最终得到的附加抖动值更加准确。

图4 附加抖动图形

图4 中,a 为时钟缓冲器输出抖动的测试误差,J△为测试误差a 导致的附加抖动的计算误差。根据式(1)和勾股定理可以分别得到式(19)(20),

式(20)-式(19),经过变化得到式(21),即为J△和JIN的关系表达式,

在式(21)中,测试误差一定的情况下,即a 为常量,对于同一个时钟缓冲器,其附加抖动不会随着时钟源输入抖动的变化而变化,JADDITIVE也为常量,从而J△只与JIN相关,即在测试误差一定的情况下,时钟源输入抖动越大,附加抖动的计算结果误差越大。

通过实测验证了时钟源的抖动大小对缓冲器附加抖动计算结果的影响[10]。这里假设缓冲器输出抖动测试误差为5 fs。表3 给出了附加抖动根据实测结果的计算值,并在时钟缓冲器输出抖动测试误差一定(5 fs)的情况下,对比了时钟源抖动大小对附加抖动计算值的影响。其中,J△为根据输出抖动实测值加误差后计算的附加抖动值和根据输出抖动实测值计算的附加抖动值间的差值。对于低抖动的时钟源,5 fs 的测试误差导致附加抖动的计算误差为7.52 fs;而高抖动的时钟源,同样的测试误差导致附加抖动的计算误差为20.44 fs。

从测试结果可以看出,低抖动的时钟源对附加抖动的计算结果影响较小,验证了式(21)的理论推导。因此在测试时钟缓冲器的附加抖动时,应选用低抖动的时钟源,时钟源抖动应接近或者低于被测器件的附加抖动。

3.2 时钟源斜率的选取

时钟缓冲器时钟源输入信号的斜率会影响时钟缓冲器输出信号的抖动,即会影响缓冲器的附加抖动。因此在测试时钟缓冲器的附加抖动时,需要关注器件手册里对于时钟源信号斜率的要求。

图5 是某款时钟缓冲器的附加抖动和输入时钟信号斜率的实测关系曲线图,从图中可以看出,输入信号斜率越小,随机抖动越大,当输入信号斜率小于5 V/ns时,时钟缓冲器的附加抖动会急速恶化。在测试时需要选用满足时钟缓冲器输入信号斜率要求的时钟源。同时在为时钟源选择时钟缓冲器时,也需要关注时钟源信号的斜率和缓冲器输入的要求是否匹配。

4 结论

本文对时钟缓冲器附加抖动计算公式进行了分析,并对附加抖动测试做了研究,从相位噪声的角度推导了附加抖动计算公式,通过实验测试验证了公式推导的正确性。本文可以帮助工程师更好地理解时钟缓冲器附加抖动的含义以及在时钟系统应用中的作用。结合附加抖动计算公式分析和实际测试,给出了时钟缓冲器附加抖动测试中的注意事项,协助工程师更准确地完成时钟缓冲器附加抖动的测试。