GaAs PHEMT的I-V特性退化机理综述

2024-01-12何述万梁晓新周智勇阎跃鹏王魁松

何述万,董 濛,周 虎,梁晓新,周智勇,阎跃鹏,王魁松

(1.中国科学院微电子研究所,北京 100029;2.新一代通信射频芯片技术北京市重点实验室,北京 100029;3.国家发展和改革委员会创新驱动发展中心(数字经济研究发展中心),北京 100045)

0 引言

新一代信息技术主导了新一轮科技革命和产业革新,摩尔定律仍然为社会的高度互联化发展、经济的数字集约化转变提供了重要支撑。

射频通信是信息交互传递的关键,由于对电路性能的苛刻,往往需要采用化合物半导体来制作晶体管。砷化镓(gallium arsenide,GaAs)器件的高载流子迁移率和低噪声等特性使其在射频通信中承担着放大、混频和控制等作用,在化合物半导体中,其技术成熟、应用广泛、发展迅速[1]。

砷化镓场效应管经历了从同质结的金属—半导体场效应管到异质结的高电子迁移率晶体管(high electron mobility transistor,HEMT)、赝调制高电子迁移率晶体管(pseudomorphic high electron mobility transistor,PHEMT)的发展过程。异质结中施主与沟道被分隔开来,在极化效应下沟道中产生高浓度的电子集合,即二维电子气(two-dimensional electron gas,2DEG),极大避免了同质结中显著的库仑散射作用,提高了电子迁移率。而PHEMT在HEMT的基础上,用InGaAs取代GaAs作沟道层,使2DEG受双边势阱限制,提高了载流子的输运特性,削弱了短沟道效应,使得器件性能更优异且更稳定[2]。

GaAs PHEMT在实际应用中可在单片上同时集成增强型/耗尽型场效应管,其可靠性是单片微波集成电路性能提升的关键[3-4]。摩尔定律下器件尺寸的微缩,使得工艺和电路参数对GaAs PHEMT的影响加剧,诸如阈值电压VTH、漏源电流IDS、跨导gm等关键电流-电压特性的退化甚至失效也愈加明显[1]。性能参数的退化过程值得从内部机理上进行分析研究,生产工艺和电路设计的改进对于加强器件及电路的整体可靠性有着重要意义。

文章第1节通过GaAs PHEMT的经典层结构介绍晶体管的功能实现原理;第2节结合模型结构推导PHEMT的I-V特性及其主要的影响参量;第3、4、5节分别从结构缺陷、电热应力和环境因素的角度分析PHEMT的主要退化机理,并针对这些退化给出了改进优化的方向和措施;最后,第6节对本文内容进行了回顾总结。

1 GaAs PHEMT层结构

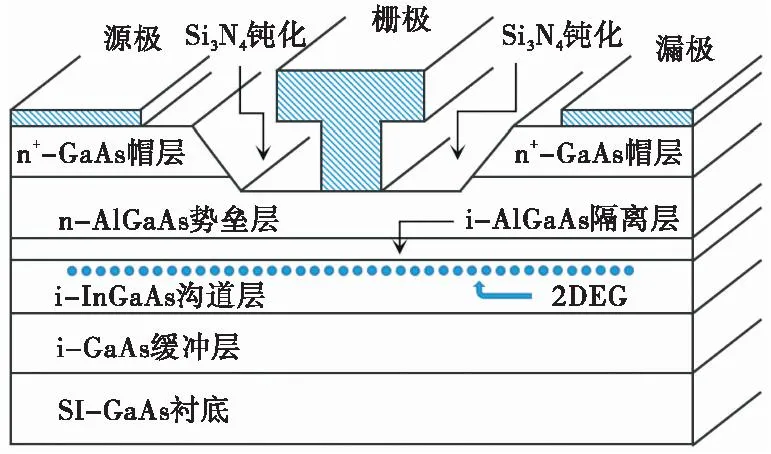

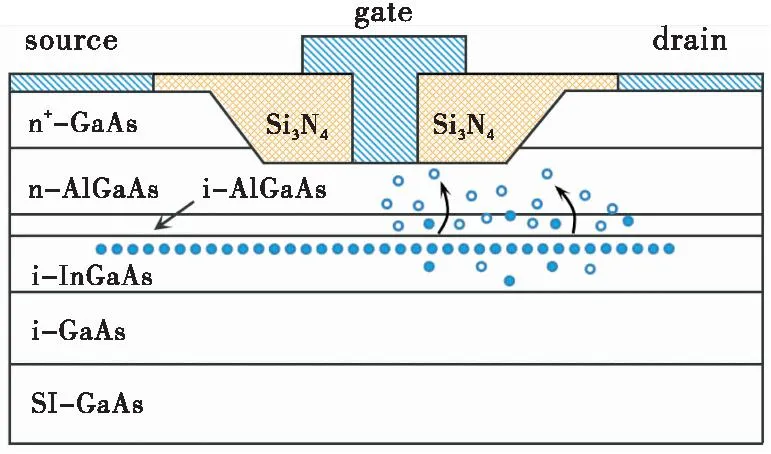

纵向层结构是决定器件性能的主要因素之一,增强型PHEMT的典型层结构如图1所示[5-6]。

图1 增强型PHEMT器件典型层结构Fig.1 Typical layer structure of E-Mode PHEMTs

在半绝缘GaAs衬底上,利用分子束外延(molecular beam epitaxy,MBE)及金属有机物化学气相沉积(metal-organic chemical vapor deposition,MOCVD)工艺,自下而上生长出具备不同功能的外延层[7]:

(1)缓冲层使用非掺杂GaAs制作,既能减弱衬底表面带来的生长缺陷以利于外延生长,又能吸收源于生长腔的杂质及衬底扩散的杂质,此外,GaAs与InGaAs的禁带宽度差构建了势垒以阻止2DEG进入缓冲层。

GaAs/AlGaAs超晶格缓冲层也是很好的选择,GaAs和AlGaAs的多次交替生长使衬底缺陷垂直延伸直至终止,缺陷掩埋效果更好,得到的外延界面更完好,且能大幅降低缓冲层的厚度。

(2)沟道层选用非掺杂InGaAs材料提供高的电子迁移率和饱和漂移速度,其禁带宽度相比AlGaAs、GaAs更窄,这种层间导带的不连续性使沟道层中形成强约束力的三角势阱,电子被封闭在AlGaAs/InGaAs异质结界面的狭窄势阱中,形成2DEG。为了克服InGaAs/GaAs异质结界面因晶格失配而产生的应力,一般把InGaAs层生长得很薄,让其中晶格存在畸变,晶格畸变的薄膜吸收失配产生的应力的过程就是赝调制[8]。

(3)隔离层使用非掺杂AlGaAs材料增大势垒层离化施主电荷与沟道层2DEG的距离,以减弱库仑散射作用,降低器件噪声,使得载流子输运特性得以改善的同时不明显影响2DEG的浓度。

(4)势垒层常用宽禁带的掺杂AlGaAs材料为势能更低的沟道层提供电子,电子穿过隔离层在沟道层势阱中聚集形成2DEG。为减小由施主离子和缺陷构成的复合体(即DX中心)形成的深能级电子陷阱,势垒层中Al的组分受到约束。

肖特基势垒从表面耗尽AlGaAs层,异质结从异质结界面耗尽AlGaAs层。理想情况下,AlGaAs的掺杂浓度和厚度应使两个耗尽区刚好重叠,以防止电子通过AlGaAs层传导,出现漏电通道。对于耗尽型器件,肖特基栅极的耗尽层应仅延伸到异质结耗尽层,而对于增强型器件,掺杂AlGaAs层的厚度较小,肖特基栅内置势垒将完全耗尽AlGaAs和2DEG沟道[9]。

(5)帽层采用高掺杂的GaAs材料同金属形成欧姆接触以制作源、漏极,栅极因需要肖特基接触以获得优良的调控效果,故不制作在帽层上。GaAs的禁带宽度比AlGaAs更低,有助于高的量子隧穿率的实现。量子隧穿同样发生在隔离层,使源、漏两端与2DEG形成接触。

2 PHEMT器件I-V特性分析

I-V特性分析是沟通器件物理与电路的桥梁,模型为这个转化过程提供过渡。基于紧凑物理模型,GaAs PHEMT通过载流子的输运特性(即本征模型),结合载流子运动过程中的实际器件物理效应和经验函数来构建方程,以此表征器件输入输出间的映射关系。

2.1 阈值电压VTH

GaAs PHEMT器件能带结构如图2所示。

图2 PHEMT器件能带结构示意图Fig.2 Schematic diagram of band structure of PHEMT devoce

栅金属与掺杂AlGaAs势垒层形成肖特基接触,内建电势qΦB使栅耗尽区出现,在能带上表现为导带底近栅金属端的向上翘曲[8]。

若忽略影响载流子输运特性的异质结界面态,则PHEMT器件的阈值电压VTH可表示为:

(1)

式(1)中,ФB为肖特基势垒高度,ΔEC为异质结导带不连续性,势垒层耗尽电压VP可由泊松方程求解:

(2)

式(2)中,Nd为势垒层施主浓度,dd为势垒层厚度,而ε是势垒层介电常数。

因为ФB和ΔEC均由栅极材料所决定,则阈值电压漂移ΔVTH可表示为:

(3)

异质结界面态表现为随着栅压变化的电容效应,电子填充情况的变化改变了阈值电压:

(4)

式(4)中Qint是单位面积的界面电荷,其与界面态密度的关系可表示为:

Qint=qNint,0(1-βVG)

(5)

式(5)中Nint,0是固定界面态密度,β是与界面态的俘获截面及密度有关的系数。

将VP及Qint的表达式代入式(4)可得:

(6)

则有阈值电压漂移量ΔVTH可表示为:

(7)

若外加栅压VG相同,式(7)可写为:

(8)

相对于Nint,0的变化而言,β的变化通常较小,若忽略其影响,则式(8)可简化为:

(9)

由式(9)不难发现,阈值电压VTH的漂移量主要受施主浓度Nd和固定界面态密度Nint,0的变化影响,负号表明影响趋势是相反的[10-11]。

2.2 漏源电流IDS

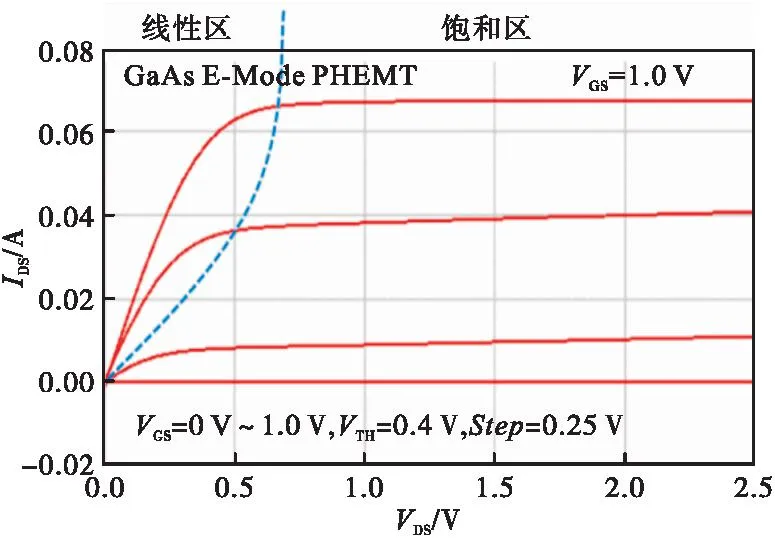

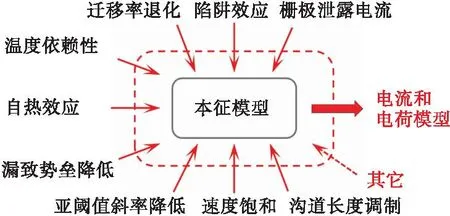

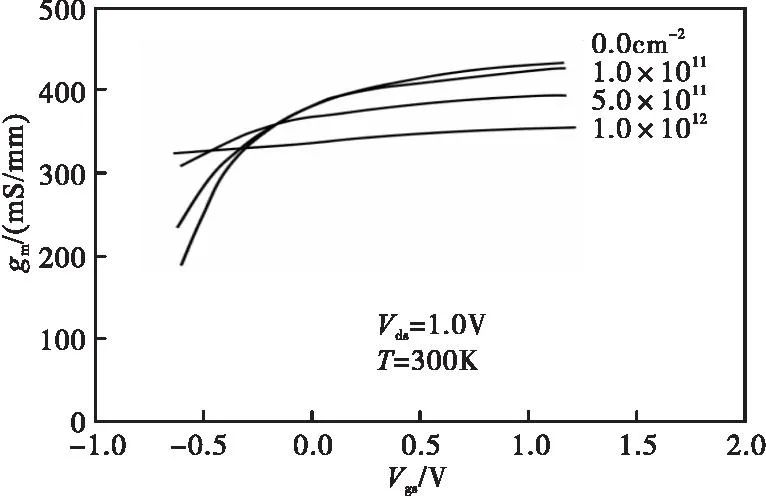

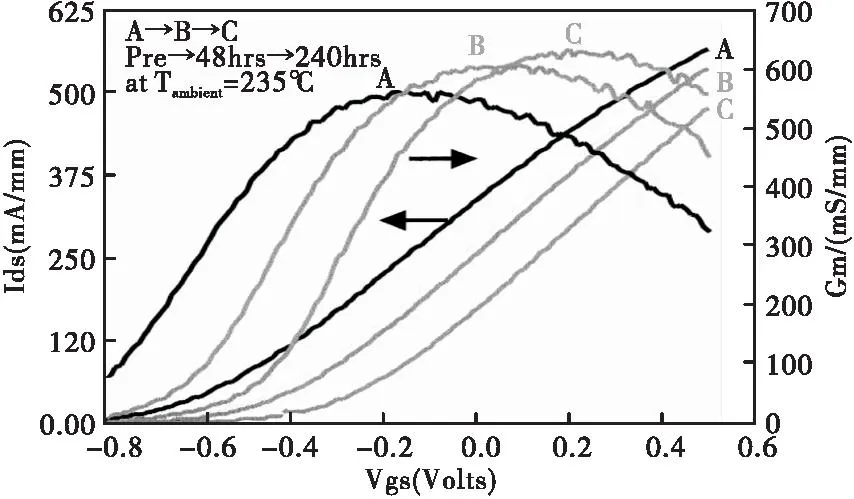

GaAs PHEMT是压控型器件,其I-V特性曲线如图3所示。当VGS>VTH时,电子进入沟道层形成2DEG,并与源漏区互连,在漏源间施加外电场VDS,即可使电子从源端运动到漏端,从而形成漏源电流IDS。若VDS 图3 GaAs PHEMT器件的I-V特性曲线Fig.3 I-V characteristic curve of GaAs PHEMTs PHEMT的I-V特性可以使用电荷控制模型和渐变通道近似得到。沟道载流子浓度ns可表示为: (10) 式(10)中,Δd为2DEG有效中心的修正因子,V(x)是由漏源电压引起的沿沟道的电势。则漏源电流IDS为: IDS=qnsv(E)W (11) 式(11)中,W为沟道宽度,v(E)为沟道中载流子漂移速度,主要与沟道电子迁移率μ及漏源电场有关。 (12) 式中ES为载流子漂移速度饱和时的沟道电场。 假设载流子迁移率μ为常数,此时在VDS为低值的线性区有: (13) 若增大VDS使PHEMT工作进入饱和区,有: (14) 式(14)中,V0=ESL,L是沟道长度[9,11]。 实际载流子迁移率μ受到沟道中陷阱影响,根据马西森定则(Matthiessen),这种影响可表示为: (15) 式(15)中μ0是包含其它散射机理的迁移率,α是陷阱电荷散射系数,NT为沟道是中陷阱总数。 式(15)微分可得载流子迁移率变化量Δμ: Δμ=-μ2αΔNT (16) 式(16)中ΔNT为沟道中陷阱总数变化量。 PHEMT在线性区的漏源电流偏移量ΔIDS为: (17) 饱和区的漏源电流偏移量ΔIDS,sat与此类似。 所以有 (18) 式(18)表明,漏源电流IDS的变化与沟道中陷阱总数NT的变化趋势相反,而且漏源电流IDS的退化与载流子迁移率μ的退化具有一致性[10]。 压控型器件的小信号增益特性由跨导所决定。跨导gm反映了器件电压转换电流的能力,其定义为源漏电压VDS为常数时,源漏电流IDS对栅源电压VGS的变化率: (19) 则器件在非饱和区的跨导gm为: (20) 可以得到在非饱和区跨导变化量Δgm: (21) 在饱和区的跨导变化量Δgm为: (22) 结合式(16)可得 (23) 式(23)表明,跨导gm的变化与沟道中陷阱总数的变化趋势相反,而且跨导gm的退化与载流子迁移率μ的退化具有一致性,这与漏源电流IDS的退化特性相同[10]。 PHEMT器件输入输出间的映射关系是各种外部或寄生效应在本征模型上叠加修正后的效果,如图4所示的非理想器件物理效应模型很好地反映了这一点。由此衍生出的晶体管的小信号模型及大信号模型,将器件物理层面的参量与电路层级的参数联系起来[12-16]。 图4 非理想器件物理效应模型Fig.4 Physical effect model of nonideal devices 各种外部或寄生效应是造成GaAs PHEMT的I-V特性退化的根源,考虑其中主要的退化机理,根据引发性能退化的原因可将退化类型区分为结构缺陷、电热应力及环境因素三个方面[17-18]。 本文涉及的退化失效机理在表1中列出: 表1 本文涉及的退化失效机理Tab.1 Degradation failure mechanism involved in this paper 因为PHEMT器件各层之间的掺杂浓度不同,所以杂质离子会自发扩散,扩散对各结构层功能实现的弱化效果是导致器件性能退化的重要原因。 从器件结构的角度出发,PHEMT的缺陷主要来源于:栅周的表面态、外延层间的界面态和晶体内体陷阱[19]。栅周表面态通常被Si3N4材料钝化填充,也可视为界面态。图5给出了PHEMT器件的界面态与体陷阱示意图。 图5 PHEMT器件的界面态与体陷阱Fig.5 Interface defects and bulk traps in PHEMTs 3.1.1 离子扩散 PHEMT器件使用非掺杂AlGaAs层隔离施主离子和2DEG,由此获得了更纯净的沟道和更低的噪声水平。但施主离子及杂质离子仍会通过扩散作用进入肖特基接触和导点沟道中,造成器件的性能退化,这个过程即为离子扩散[5]。离子扩散是基于布朗运动从高浓度区域向低浓度区域进行的输运过程,是熵驱动的趋向热平衡态的弛豫过程。 离子扩散主要包括势垒层中的Al到栅凹槽区的横向扩散,以及势垒层中的Al和n+-AlGaAs层(δ掺杂)中的Si到沟道区的垂直扩散。横向扩散导致施主浓度Nd的降低,也使异质结导带的不连续遭到破坏,使得栅压VGS的调控作用减弱,阈值电压出现一定程度的负向漂移。垂直扩散导致了沟道层非纯净散射的增加,散射过程使载流子速度的大小和方向不断变化,降低了电子迁移率μ,从而降低了漏源电流IDS与跨导gm[20]。 3.1.2 界面态效应 GaAs属于闪锌矿晶体结构,不同的原子交替占据晶格点的位置,纯晶体内晶格呈严格的周期性排布,但界面处晶体的晶格不再完整,周期势场的中断在禁带中引入了陷阱能级。晶体表面因晶格失配形成悬挂键使电子被局限在表面附近的状态即为界面态。此外,界面粗糙度的不一致和半导体材料间热应力导致的失配也会产生界面态。 在异质结器件中,栅周的界面态效应存在于栅源、栅漏之间的钝化层界面处,它能俘获一定数量的电子,形成电荷的积累,使漏/栅区的有效电场的降低,导致耗尽区宽度的增加。为保持器件的电中性,在AlGaAs下界面处会产生正的诱导电荷,中和部分2DEG使其浓度降低,最终导致漏源电流IDS减小[2]。 外延层界面态通常是以局域态的形式出现在界面两侧,这是由于AlGaAs/InGaAs/GaAs禁带宽度的不同,在其界面处形成了很强的极化电荷。极化过程主要考虑受主陷阱,该陷阱平时为电中性,有电子填充时显负电性,界面态通过陷获和隧穿过程,造成额外的电离杂质散射。由于在InGaAs层上生长AlGaAs势垒层时破坏了界面的平移对称性,所以异质结AlGaAs/InGaAs的界面态对导带不连续的破坏更明显,对沟道载流子输运影响更大,在退化过程中起主导作用[10]。 张兴宏等在文献[21]中的研究表明,器件性能显著变化的界面态密度分界值为1.0×1011cm-2。小于该值时界面态对GaAs PHEMT器件直流性能的影响不明显,器件的跨导随栅压有较大的变化,低栅压下跨导与电子迁移率成正比。大于该值时界面态对器件的I-V特性有较大的影响:随着界面态密度的增加,在源漏间电场的作用下界面态上的电子发生电离并参与沟道导电,漏源电流IDS增大;随着界面态密度的增加,减弱了栅极的调制效应,致使器件阈值电压VTH负向漂移,也使器件在低栅压下跨导增加,在高栅压下跨导减小。图6显示了不同界面态密度对跨导的影响[21]。 图6 不同界面态密度时跨导随栅压的变化[21]Fig.6 The variation of transconductance with gate voltage at different interface state densities[21] 3.1.3 体陷阱 体陷阱与界面陷阱本质相同,只是陷阱电荷在器件中不同位置的具体表现,有别于不能进行电量交换的固定电荷,陷阱电荷具有充放电功能,也即能俘获/释放电子。在界面陷阱中考虑的是陷阱面密度,而体陷阱考虑的是陷阱浓度。 体陷阱主要由晶体杂质、晶格失配、射线辐射等原因形成,在势垒层和缓冲层中均存在。势垒层和缓冲层中的陷阱主要通过俘获热电子,使沟道层中2DEG的浓度降低,从而使漏源电流IDS与跨导gm退化。体陷阱的俘获能力与浓度相关,随着陷阱被占据完全,俘获逐渐达到饱和,漏源电流IDS和跨导gm将重新稳定。在整个过程中,电流和跨导呈现崩塌的效果。因为缓冲层的厚度比势垒层大,相同浓度下缓冲层体陷阱更容易俘获热电子,对电流崩塌效应的影响也更显著[22]。 3.2.1 材料结构及工艺 PHEMT器件自1985年的问世以来,其性能提升主要归功于材料结构的改进,包括缓变调制AlGaAs层、平面调制AlGaAs层(δ掺杂)、超晶格缓冲层、超晶格施主层和多重沟道及量子阱等方面的不断变化。这些改进很大程度上减少了器件的缺陷和陷阱,提高了器件的性能和可靠性。在高性能电路中使用双栅极器件而不是两个级联器件,能最大限度地减少寄生效应、提高性能并节省芯片面积。这些方向也仍将是之后材料结构改进的重点,需要更多的理论研究和实践探索[23-25]。 当然,材料结构的改进需要先进工艺作为支撑。从器件纵向结构来说,材料的结构为多层厚薄,因而对工艺要求更加精密;从器件横向加工来看,切割(腐蚀)剖面深度要精确到几十埃的量级,往往还要分成多个层次,从而对腐蚀提出了更高的要求[25]。 3.2.2 生长介质膜 生长介质膜是制备晶体管管芯保护层的工艺,是栅极的钝化保护,常采用Si3N4作为栅极的生长介质膜材料。生长介质膜在隔离栅极和源极、栅极和漏极的同时,通过对势垒层表面的填充降低了器件表面态密度,进而抑制了器件工作时的电流崩塌效应。虽然对生长介质膜材料热处理可进一步减弱器件的表面态密度,但这通常以击穿电压的下降为代价。 生长介质膜也能避免器件遭受恶劣环境及杂质离子的侵害,对包括氢的外部杂质离子扩散过程有抑制作用,还能保持器件在电热应力下的性能稳定。杂质离子穿透介质膜的平均时间与介质膜厚度呈指数关系,往往通过直接加厚和多层加厚的方法能提高器件的扩散遮蔽能力。但因为Si3N4的介电常数较大,其厚度增加也带来了栅电容的增加,导致器件截止频率fT的下降,所以需要精确控制介质膜的生长[26-27]。 4.1.1 热电子效应 PHEMT器件在过驱动状态下可获得最大增益,而沟道中2DEG在强横向电应力下加速获得足够的动能成为热电子。热电子效应发生在饱和区,此时载流子漂移速度饱和,当漏端施加更大电压时,热电子获得更多动能,热电子效应也更显著。这个过程取决于漏栅电压Vdg,而非漏源电压Vds。需要说明,载流子饱和漂移速度vsat是一个平均量,与电场无关。 因为动能足够高,这些热电子会在沟道中碰撞电离,由此产生的电子空穴对在电场中被分离。电子在沟道中继续加速运动,而空穴由价带跃迁至导带进入势垒层及栅周。一部分空穴被栅极收集产生栅电流,而另一部分空穴被陷阱电子俘获,在栅下空穴积累形成一层内建的正电荷,降低了肖特基势垒的高度,使得阈值电压VTH负向漂移,从而使得PHEMT器件漏源电流IDS出现上升,而跨导gm只是沿栅源电压VGS负向平移[5,20]。 刘红侠等在文献[1]中指出,GaAs PHEMT器件阈值电压的退化可分为两部分,其中可恢复的漂移可由栅下势垒层中深能级DX中心的空穴积累所解释,而永久的漂移可由栅钝化层及肖特基接触界面的空穴陷落所解释[1]。 由于热电子获得的能量大部分在散射过程中被转移,而温度的升高会使电子承受更多的散射,所以热电子效应拥有弱的或负的温度依赖性。 图7为GaAs PHEMT热电子效应示意图。 图7 GaAs PHEMT器件热电子效应示意图Fig.7 Illstration of hot carrier effect in GaAs PHEMTs 4.1.2 电迁移 热电子在电场下获得的能量大部分被转移,其转移对象包括金属原子。金属原子在与电子进行动量交换后沿着金属条运动形成电迁移。电迁移与温度和电流密度有关,通常认为其阈值电流密度为2×105A/cm2[5,20]。 电迁移存在于源漏接触边缘和垂直方向,也存在于多层金属的互连线之中。电迁移既有横向的,也有纵向的,前者原子的迁移方向沿着电极方向,而后者的迁移方向垂直于电极方向。横向电迁移致使金属原子在晶格界面逐渐积累,栅末端和漏接触上原子积累产生指状金属,导致器件短路。纵向电迁移致使垂直于源漏方向上的材料空洞和积累,引起栅结构上外延小丘的形成,导致栅源或栅漏短路[28-29]。 虽然电迁移与离子扩散、栅金属下沉都表现为离子或原子的运动。但三者的诱发机理不同:离子扩散是布朗运动的结果,电迁徙是电应力作用的结果,而栅金属下沉是热应力作用的结果。 4.1.3 栅金属下沉 GaAs PHEMT的栅极通过金属—半导体形成的肖特基接触来控制沟道,肖特基接触是器件实现电性能参数的关键。PHEMT器件多采用Au/Pd/Ti或Au/Pt/Ti的金属结构制作栅极,顶层的厚Au用于低阻电传导,中层的Pd或Pt用于阻挡金属Au向下扩散,底层的薄Ti用以更好的粘接半导体材料,增强型的PHEMT器件为提高的肖特基势垒会在薄Ti下再做一层Pt。金属Pt的熔点高、原子质量大,其引入提高了栅极耐扩散、耐电迁移、耐高温的能力[30]。 正常工作温度下,栅金属扩散速度极慢,所以栅金属下沉往往是在高温工作状态下或在加速寿命试验中出现,是栅极金属遭受热应力后的扩散现象。实际上,阻挡层很好的阻挡了金属Au的向下扩散,所以在高温加速寿命试验中观察到的是金属Ti扩散进入AlGaAs势垒层,长期高温还会出现金属Pd或Pt扩散进入Ti薄层,甚至穿过Ti薄层进入AlGaAs势垒层的现象,Ti的扩散过程还引起了Ti-AlGaAs间化合物的形成。一般认为金属Ti的扩散是造成器件性能退化的主因。栅金属和半导体的相互扩散降低了势垒层施主浓度Nd,栅金属下沉减小了势垒层厚度dd,加剧了栅极调制效应,使阈值电压VTH正向漂移[31-35]。 栅金属下沉还会导致接触界面出现额外缺陷,伴随着热应力会在栅金属和衬底间形成细微的导电通道,局部热斑的形成弱化了器件的整流特性。 CHOU Y C等在文献[36]中给出了0.15μm GaAs PEHMT器件在235℃的高温寿命试验下漏源电流Ids和跨导Gm的退化情况,如图8所示。其中跨导Gm由A向C退化,随着栅源电压Vgs的正向偏移,跨导Gm的峰值小幅上升;漏源电流Ids由A向C退化,饱和漏源电流Idss出现降低[36]。 图8 GaAs PHEMT器件高温寿命试验退化情况[36]Fig.8 Degradation of GaAs PHEMTs during high temperature life testing[36] 4.2.1 抗热电子效应 热电子效应在高的漏栅电压Vdg下发生,电路设计上改进要从避免晶体管进入饱和区和减小沟道电压的方向考虑。 在深亚微米工艺中,降低供电电压是降低电场强度最有效的方法,当前部分GaAs PHEMT工艺库中提供了标压和低压两种规格的晶体管,用低压管替换标压管不会带来额外的面积消耗,为设计提供了极大方便。在复杂逻辑电路中,可以将二极管串联到晶体管的漏端,通过分压来减小沟道电压;也可以将一个常开晶体管插入到晶体管的输出漏端,通过常开晶体管吸收大比例的输出节点电压,以缓解其他晶体管的电应力。在开关电路中,较慢的转换速率会使晶体管的状态过渡过程更久,引起更多的退化;过高的负载电容会增加晶体管位于饱和区的时间,也会导致更多的退化[37]。 创建具有供体—受体掺杂的PHEMT(DA-PHEMT)的异质结构也有助于抗热电子效应,这种结构引入了额外的势垒以增强热电子在InGaAs量子阱中的局域化,这种变化不仅可以增加 2DEG 浓度和沟道电导率,还可以增加热电子的饱和漂移速度[38]。 4.2.2 推栅工艺 推栅工艺是对栅金属下沉现象的反向利用,主要用来解决器件阈值电压离散的问题。尤其是在增强型PHEMT中,因为栅金属需要更加靠近沟道,势垒层厚度dd的值更小,栅生长工艺波动所造成的阈值电压离散问题比耗尽型器件更为严重。增强型PHEMT中栅的最底层金属为Pt,利用Pt金属膜在退火工艺中向势垒层下沉的现象,以减小栅金属到沟道的距离的过程称之为“推栅”。 金属Pt的下沉深度主要受Pt金属膜的原始厚度影响,两者比值固定,所以想要下沉深度精准,就要制备足够均匀的Pt金属膜。章军云等在文献[35]中估算出Pt金属厚度每0.1nm的变化所引起的阈值电压偏移量约为13mV,如此尺度下的变化需要精确控制Pt金属膜的厚度[35]。 5.1.1 辐射效应 器件在航天领域的应用会面临多种类型的辐射,这些辐射对器件的作用效果可归结于电离效应和位移效应两种。PHEMT器件使用的材料具有宽禁带和非绝缘的特点,使其具备良好的抗电离效应特性,所以GaAs PHEMT主要的辐照损伤是高辐射剂量带来的位移损伤。 在辐射剂量较低时,材料中的缺陷在电离效应下俘获电子,使散射增加,迁移率的小幅退化造成漏源电流IDS的小幅退化;在辐射剂量增大后,异质结界面处的应力得到释放,使界面态密度降低,迁移率的小幅回升带来漏源电流IDS的小幅回升;当辐射剂量很大时,辐射粒子进入器件内部并与晶格发生弹性碰撞,致使原子偏离原有晶格位置,大量缺陷的产生导致沟道载流子密度骤降,继而引发I-V特性的大幅退化[39-40]。 图9为GaAs PHEMT器件辐照损伤过程[10]。 图9 GaAs PHEMT器件辐照损伤过程[10]Fig.9 Radiation damage process of GaAs PHEMTs[10] 5.1.2 氢效应 GaAs PHEMT器件的制作过程中,采用的封装外壳通常含氢并释放氢原子到腔体内,采用的离子注入技术也会将氢、氧注入GaAs中形成高阻层以实现电隔离。氢在器件内部引发的氢效应是离子扩散的结果[5]。 氢气分子在栅金属Pt的催化作用下转化为氢原子,氢原子会吸附在金属表面。首先,氢原子扩散进入到栅极下方的n+-AlGaAs(δ掺杂)层中,中和Si施主形成Si-H化合物,从而减小了有效载流子浓度,导致漏极电流IDS与跨导gm的下降,阈值电压VTH正向漂移。然后,氢原子与金属Ti作用生成的TiHX化合物会在栅极中产生压应力,这种应力通过压电效应在下面的半导体中引起极化体积电荷分布,电荷的积累改变了肖特基势垒的高度,导致内建电势发生变化,进而使阈值电压VTH负向漂移,漏极电流IDS小幅回升。随着TiHX化合物的饱和,肖特基势垒高度也基本稳定,晶体管的I-V特性也基本不变[27,41-43]。 图10为GaAs PHEMT器件氢效应示意图[43]。 图10 GaAs PHEMT器件氢效应示意图Fig.10 Illstration of hydrogen effect in GaAs PHEMTs 5.2.1 钝化保护 钝化保护是MMIC工艺流程中的最后工序。相较而言,生长介质膜因为空间的局限使其主要作用在于降低表面态密度,而钝化层承担了更多的减弱外界环境因素对器件影响的作用。钝化保护可以减弱器件俘获环境中电荷的能力,降低器件性能对时间、温度和电场的敏感性,也防止器件在划片、解离、装架等过程中管芯受到损伤。基于绝缘性能、介电强度、材料间反应、工艺兼容性等特性选择合适的钝化材料对器件很重要[26]。 5.2.2 封装处理 氢效应在非密封器件中不易发生,因为氢气会流动释放掉,而在一些特殊应用环境下(如航空航天),需要采用密封设计以避免水汽及大分子气体侵入器件。可以通过对封装材料的处理以避免密封器件中氢效应的发生:(1)采用吸氢材料。吸氢材料可通过物理吸附或化学反应的方法降低封装腔体内的氢气浓度,但吸氢效率低,也会引入新的问题。(2)控制材料漏率。器件密封针对的是水汽和大分子气体,可以控制材料的漏率在合适的值,既防止外部入侵,又保证内部小分子气体能释放出去。(3)高温烘烤管壳。在芯片封装前烘烤处理管壳能减少材料及镀层中残留的氢气,这也是目前广泛采取的手段。(4)偏置补偿。氢效应一般只导致器件特性的漂移,可采用自偏压补偿电路来抵消氢效应引起的工作点的漂移[43-45]。 在新一轮信息技术发展背景下,文章着眼于GaAs PHEMT器件的性能退化难题,根据外延层的结构系统介绍了PHEMT器件缓冲层、沟道层、隔离层、势垒层和帽层的材料结构及各自作用,然后结合器件物理进行晶体管电学参数上的推导,得出阈值电压VTH主要受施主浓度Nd和固定界面态密度Nint,0的影响,漏源电流IDS和跨导gm主要受沟道中陷阱总数NT和载流子迁移率μ的影响。由此,文章得以从包含离子扩散、界面态效应和体陷阱的结构缺陷,包含热电子效应、电迁移和栅金属下沉的电热应力,以及包含辐射效应和氢效应的环境因素这三个方面,分别分析各退化机理影响I-V的作用途径和过程。根据退化过程的梳理,文章统筹器件物理、工艺实践和电路设计方面的知识,给出了GaAs PHEMT的I-V特性退化的改进方法和措施,包括工艺环节上介质膜和钝化层的生长制备、金属栅极和封装的退火加热等的方法优化,包括材料结构上双栅结构和异质结构的设计创新,还包括电路设计上晶体管和电路结构的技巧运用等。 因为GaAs PHEMT器件退化失效机理需要在微观尺度下对器件各种效应的过程进行观察测量,导致目前相关的研究较为分散,对各种效应的解释仍有较大不足,模型的量化研究还比较浅薄。而根据退化机理所提出的性能改善措施需要结合工艺结构过程,所涉及知识较为庞杂,当前还比较缺少归纳性的陈述总结。随着化合物工艺的高速发展和广泛应用,器件可靠性作为单片微波集成电路性能提升的关键受到更多的重视,相关的探索和研究正在加快推进。

2.3 跨导gm

3 结构缺陷引起的退化及改进

3.1 结构缺陷引起的退化

3.2 结构缺陷退化改进

4 电热应力造成的退化及改进

4.1 电热应力造成的退化

4.2 电热应力退化改进

5 环境因素导致的退化及改进

5.1 环境因素导致的退化

5.2 环境因素退化改进

6 结论