软击穿对压控磁各向异性磁隧道结及其读电路性能影响

2024-01-08金冬月曹路明张万荣贾晓雪潘永安

金冬月, 曹路明, 王 佑, 张万荣, 贾晓雪, 潘永安, 邱 翱

(1.北京工业大学信息学部, 北京 100124; 2.北京航空航天大学合肥创新研究院, 合肥 230013)

磁随机存储器(magnetic random access memory, MRAM)不仅具有读写速度快、功耗低等特点,并且与互补金属氧化物半导体(complementary metal oxide semiconductor, CMOS)工艺相兼容,有望成为下一代主流非易失性存储器,在存算一体架构和云存储等领域具有良好的发展前景[1-2]。其中作为MRAM基本存储单元的磁隧道结(magnetic tunnel junction, MTJ),根据驱动方式主要分为自旋转移矩磁隧道结(spin transfer torque MTJ, STT-MTJ)、压控磁各向异性磁隧道结(voltage-controlled magnetic anisotropy MTJ, VCMA-MTJ)和自旋轨道矩磁隧道结(spin orbit torque MTJ, SOT-MTJ)等[3-5]。不同于STT-MTJ驱动电流较大、动态功耗较高,三端结构的SOT-MTJ不利于高密度集成,而VCMA-MTJ具有较高的电阻值和较低的写入功耗,现已受到了国内外学者的广泛关注[6-7]。近年来,有学者先后建立了VCMA-MTJ电学模型,并研究了脉冲电压和工艺偏差对VCMA-MTJ自由层磁化方向翻转及其写电路错误率的影响[8-10]。然而,随着VCMA-MTJ尺寸的不断缩小以及MRAM存储容量的不断增大,软击穿对VCMA-MTJ电阻Rt和隧穿磁阻比率M的影响将变得越来越大,甚至会导致VCMA-MTJ读电路读错误率的显著增大。

本文在充分研究软击穿形成机理基础上,修正了VCMA-MTJ电学模型,研究了软击穿对Rt、M等参数的影响,分析了软击穿时间Ts与氧化层厚度tox和脉冲电压Vb的关系。针对软击穿对MTJ不同状态影响程度的不同,本文设计了一种具有固定参考电阻的VCMA-MTJ读电路,并将上述电学模型应用到该读电路中,通过蒙特卡罗仿真研究软击穿对该读电路读错误率的影响。在此基础上,本文还设计了一种具有参考电阻调控单元的VCMA-MTJ读电路来进一步削弱软击穿对读电路性能的影响。

1 VCMA-MTJ软击穿机理

VCMA-MTJ结构如图1所示。其中,参考层和自由层主要为钴铁硼(CoFeB),氧化层主要为氧化镁(MgO)。参考层的磁化方向固定不变,而自由层的磁化方向会在外加脉冲电压Vb的作用下发生翻转。当自由层和参考层的磁化方向相同时称为平行(parallel, P)态,此时VCMA-MTJ呈低电阻特性,其电阻用RP表示;当自由层和参考层的磁化方向相反时称为反平行(anti-parallel, AP)态,此时VCMA-MTJ呈高电阻特性,其电阻用RAP表示。

图1 VCMA-MTJ软击穿机理分析示意

因为VCMA-MTJ中的氧化层厚度为nm量级,所以在VCMA-MTJ两端施加Vb会导致在氧化层中形成高达109V/m量级的强电场。由Degraeve等[11]提出的渗透模型理论可知,此时将会在氧化层内部产生缺陷,并且随着施加Vb的应力时间t的不断增加,缺陷数量n也会不断增多。具体地,n(t)[12]可表示为

(1)

式中:缺陷产生幂律指数αn=0.4;拟合因子Δγ=1.66×10-6;缺陷产生率β=2.1×10-25m-1;拟合因子αd=40;电子电荷量q=1.6×10-19C;缺陷直径a0=0.18 nm;VCMA-MTJ面积Am=1 962.5 nm2;tox为氧化层厚度。

R0为初始状态下VCMA-MTJ的电阻,与VCMA-MTJ的磁化状态mz密切相关。R0的公式[13]可以具体表示为

(2)

n(t)的不断增多,将会在VCMA-MTJ氧化层中形成有效导电路径,产生漏电流,进而发生软击穿。相应地,将发生软击穿时对应的缺陷数量称为临界缺陷数nc。nc的公式[14]可以具体表示为

(3)

此时,将发生软击穿时对应的时间称为软击穿时间Ts[15-16]。本文在考虑Vb和tox对Ts影响的情况下,将式(2)(3)代入式(1),整理得到

(4)

软击穿发生时产生的漏电流则被称为软击穿电流Is。该电流流经的由缺陷形成的导电路径则可等效为软击穿电阻Rs,并联接入原有VCMA-MTJ电阻R0的两端。随着t和n(t)的不断增加,导电路径将进一步展宽,Rs将会减小,Is将会增大。因此,软击穿的发生将会对VCMA-MTJ的Rt和M产生重要影响。下面结合图1进行具体分析。

1) 当t=0时,VCMA-MTJ处于初始状态,如图1(a)所示。此时,VCMA-MTJ氧化层中无缺陷,Rt(0)=R0,M(0)=M0。

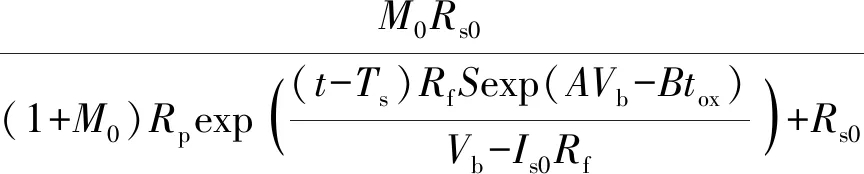

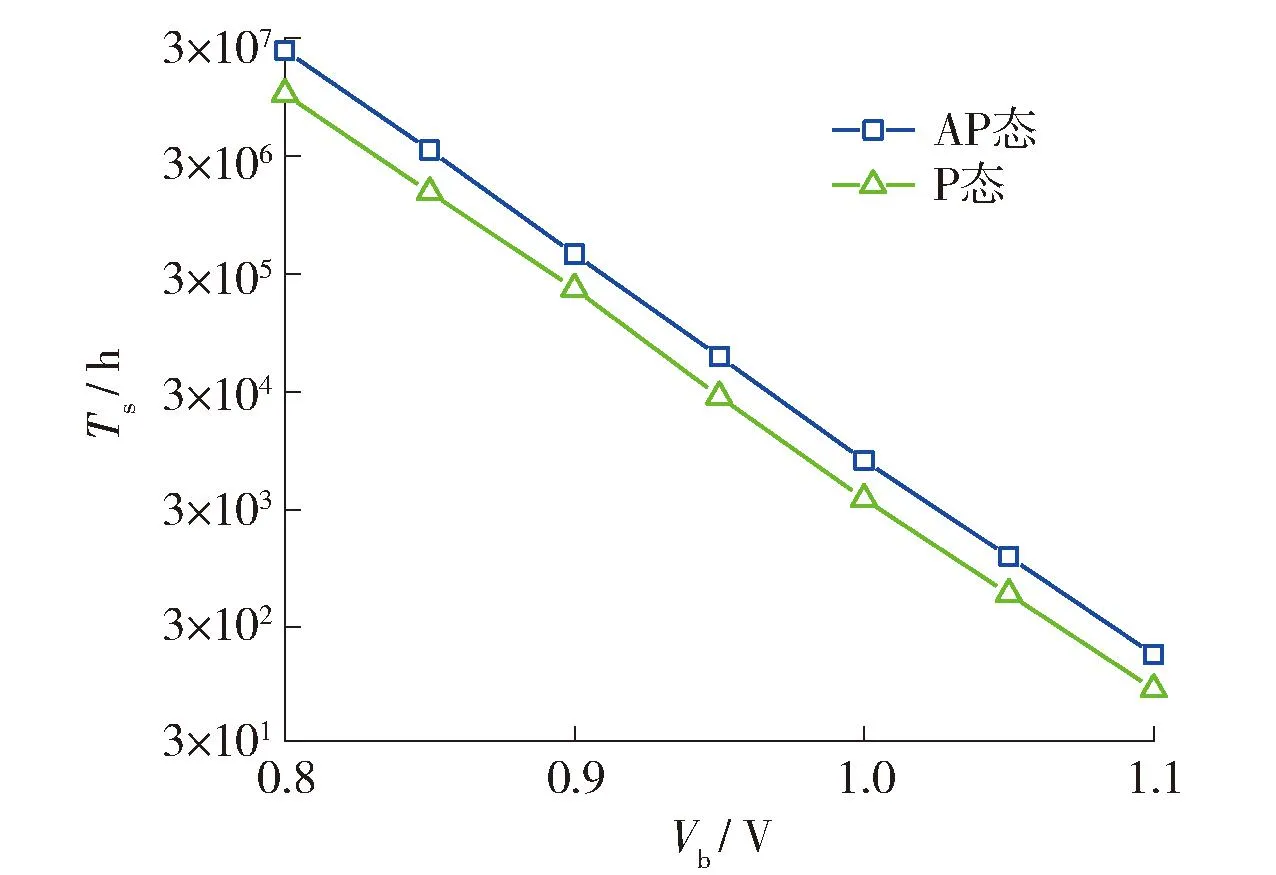

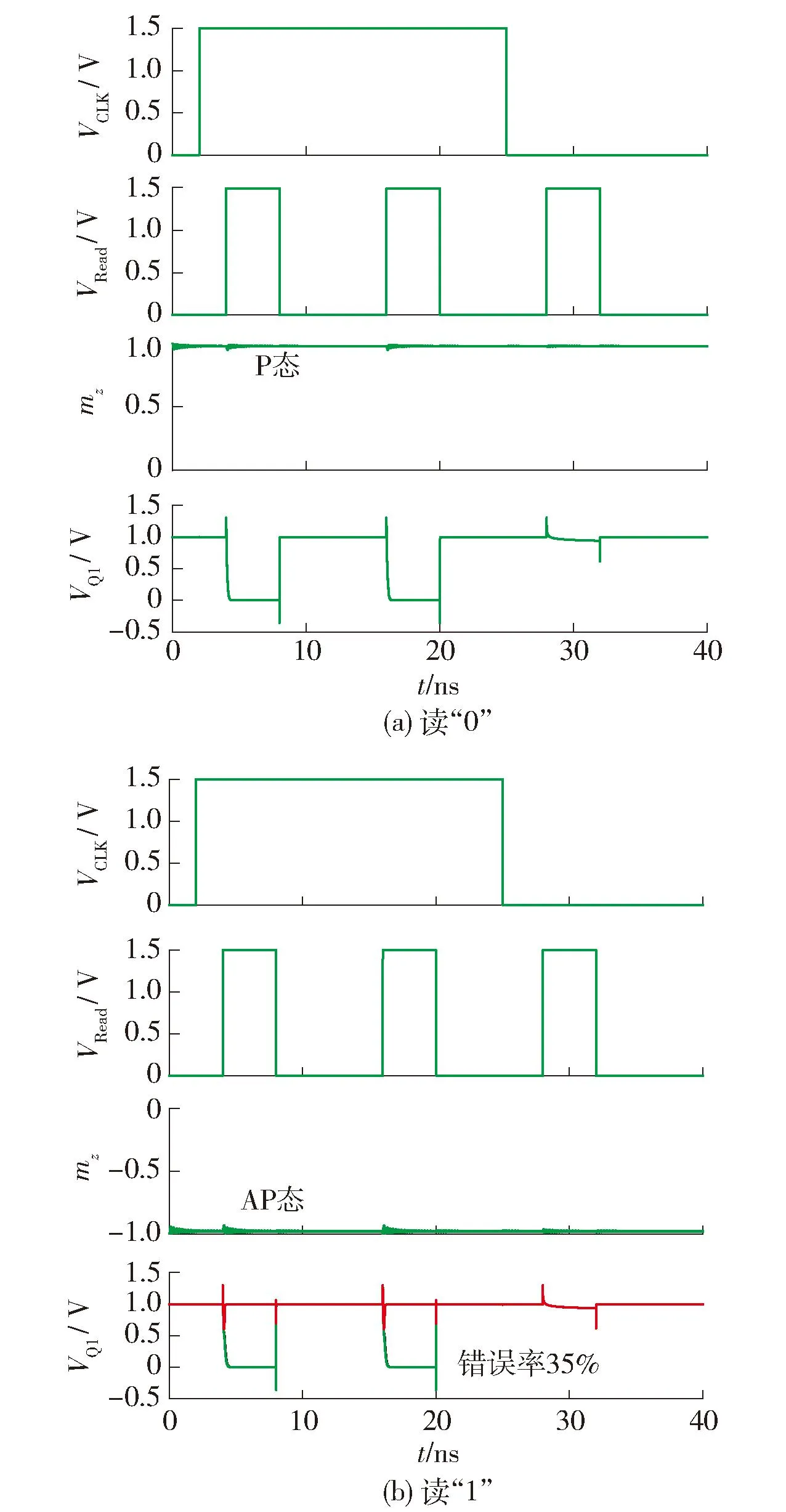

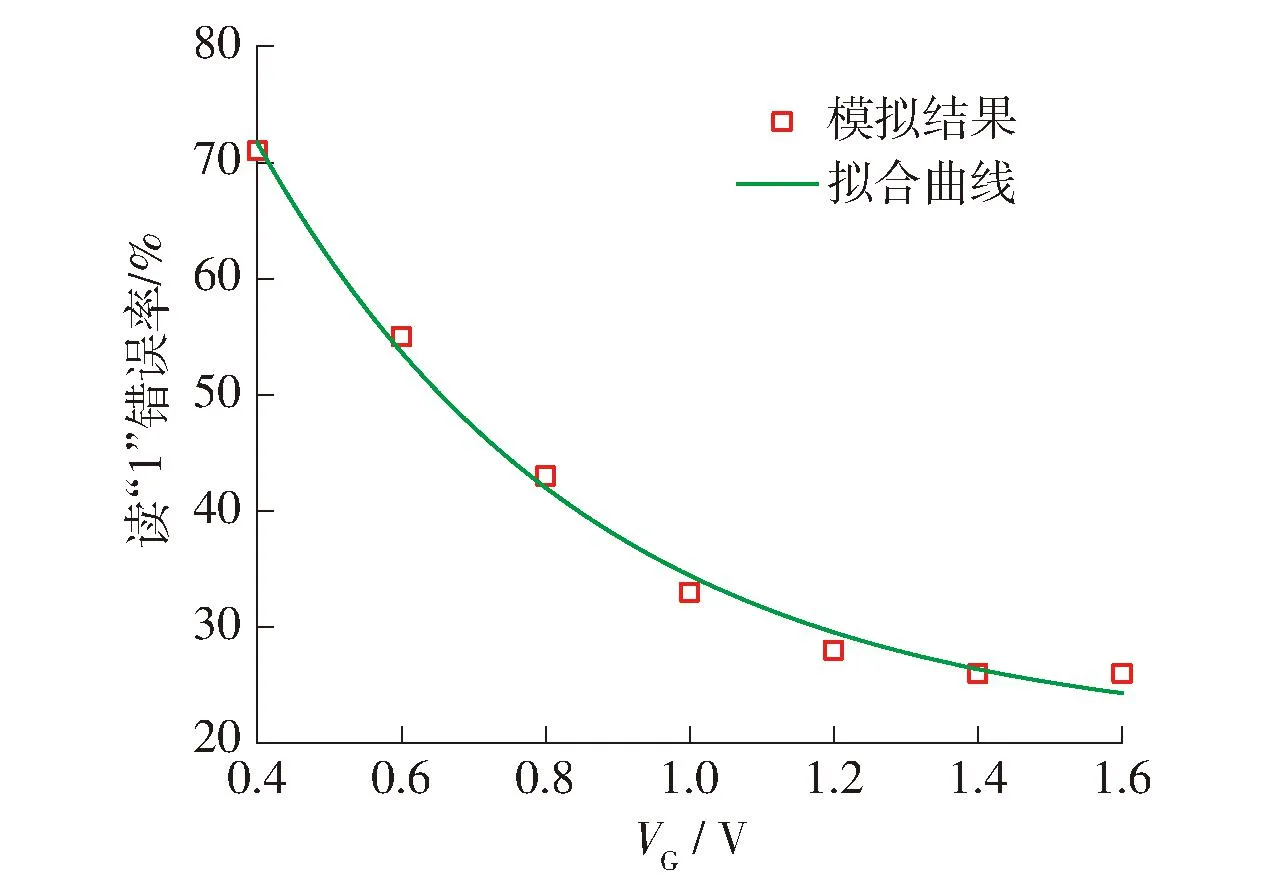

2) 当0 3) 当t=Ts时,n(t)=nc,缺陷的不断堆积将在氧化层中形成有效导电路径,发生软击穿,如图1(c)所示。此时的软击穿电流被称为临界软击穿电流Is0,公式[17]为 (5) 式中:拟合系数P=8.17×107(Ω·m2)-1;拟合因子η=3.9。此时的软击穿电阻被称为临界软击穿电阻Rs0,公式为 (6) 结合图1(c),可以得到发生软击穿时的VCMA-MTJ电阻Rt(Ts),表达式为 (7) 根据隧穿磁阻比率的定义,发生软击穿时的隧穿磁阻比率M(Ts)可表示为 (8) 4) 当t>Ts时,n(t)>nc,随着缺陷数量的不断增多,有效导电路径将逐渐展宽,如图1(d)所示。此时的Is(t)[18]可表示为 (9) 式中:常数S=1.25×10-5;拟合因子A=14.7;拟合因子B=1.2;失效电阻Rf=10 Ω。 相应地,Rs(t)可表示为 (10) 结合图1(d),本文分别给出发生软击穿后的电阻Rt(t)以及M(t)的表达式,即 (11) (12) 基于上述VCMA-MTJ软击穿机理的理论分析,本文进一步通过Verilog-A语言建立VCMA-MTJ电学模型,分别研究软击穿对VCMA-MTJ中Rt和M的影响,并分析比较Ts与tox和Vb的关系。 1) 软击穿对Rt和M的影响 本文研究了VCMA-MTJ分别在P态和AP态下Rt和M随t的变化曲线,如图2所示。其中,tox=1.4 nm,Vb=1.0 V。 可以看出,VCMA-MTJ处于P态时的软击穿时间Ts为3.39×103h,远短于VCMA-MTJ处于AP态时的软击穿时间6.67×103h,即VCMA-MTJ处于P态更容易发生软击穿。同时,VCMA-MTJ处于P态和AP态时的Rt和M均随t的增加而减小,其中,处于P态的VCMA-MTJ发生软击穿后M从初始值100%降低至50%需要120 h,而AP态的VCMA-MTJ则对应为130 h,因此,软击穿对P态影响更为严重。 图2 不同状态下Rt和M随t的变化 2) 软击穿时间Ts与tox和Vb的关系 由前面VCMA-MTJ软击穿机理分析可知,Ts主要取决于tox和Vb,因此,通过改变tox和Vb可以实现对Ts的调控。 图3给出了VCMA-MTJ在P态和AP态下Ts随tox和Vb的变化情况。可以看出,虽然Ts随tox的增大而增加,但增幅较小,而Ts却随Vb的增大而迅速减少。进一步地,图4给出了tox=1.4 nm时Ts随Vb的变化情况。由此可见,Vb对Ts的影响更为显著。因此,可以通过增大tox或适当降低Vb来推迟VCMA-MTJ软击穿的发生。 图3 不同状态下Ts随tox和Vb的变化 图4 tox=1.4 nm时Ts随Vb的变化 通过上述分析可知,软击穿对P态下的VCMA-MTJ影响更为严重,因此,本文设计了一款具有固定参考电阻的VCMA-MTJ读电路,通过设计VCMA-MTJ与固定参考电阻之间的电阻差异,利用电位放电速度的不同来实现“0”或“1”的输出,可有效避免读“0”错误率的产生。 在实际制备过程中,VCMA-MTJ的氧化层厚度会不可避免地存在几个原子层厚度范围内的微小偏差,通常认为VCMA-MTJ的氧化层厚度遵循高斯分布[19-20],即 (13) 式中:P为概率密度;σ为标准差;n为样本数量;tox,i为第i个VCMA-MTJ的氧化层厚度。 在此基础上,本文通过Verilog-A语言建立了VCMA-MTJ的蒙特卡罗模型,其中,n=100,σ=0.01tox。本文通过引入随机变量,使tox,i围绕tox呈高斯分布,进一步通过蒙特卡罗仿真研究软击穿对VCMA-MTJ读电路的影响。 具有固定参考电阻的VCMA-MTJ读电路结构如图5黑色实线部分所示,包含1个VCMA-MTJ存储单元(MTJ1)、1个参考电阻R0(R0=(RP+RAP)/2)、4个P沟道金属氧化物半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor,MOSFET)(P0~P3)和6个N沟道MOSFET(N0~N5)作为预充电灵敏放大器单元。图中:CLK为时钟信号;Read为读脉冲信号;驱动电压Vdd=1.0 V。在上述电路中,当MTJ1处于P态时表示其存储的数据为“0”,当MTJ1为AP态时表示其存储的数据为“1”。 图5 VCMA-MTJ读电路 当CLK为低电位时,N4、N5关断,读电路关闭。当CLK为高电位时,N4、N5导通,读电路开启。当Read为低电位时,P0、P3、N0、N1导通,P1、P2、N2、N3关断,此时电路进入预充电状态,Q0、Q1被Vdd上拉到高电位。若此时Read跳转为高电位,则P0、P3关断,N2、N3导通,电路进入读取状态。 当MTJ1处于AP态时,MTJ1存储的数据为“1”,Rt=RAP>R0,因此,N0—N2—MTJ1—N4路径中的电流I1小于N1—N3—R0—N5路径中的电流I0,进而Q1电位下降速度将慢于Q0电位。当Q0下降至低电位时,P1导通,N0关断,此时Q1被Vdd迅速上拉至高电位,实现了MTJ1存储的数据“1”的准确输出。 当MTJ1处于P态时,MTJ1存储的数据为“0”,Rt=RP 将本文的VCMA-MTJ电学模型应用在具有固定参考电阻的VCMA-MTJ读电路中,并进行蒙特卡罗仿真,初始时刻(t=0)读“0”和读“1”的仿真波形分别如图6(a)(b)所示。可以看出,当CLK的电压VCLK和Read的电压VRead同时为高电位时,该读电路可以通过Q1端的电压VQ1将MTJ1存储的数据准确地输出。 图6 具有固定参考电阻的VCMA-MTJ读电路在t=0时的蒙特卡罗仿真波形 图7给出了发生软击穿(t=6.67×103h)时该读电路的仿真波形。可以看出:当MTJ1处于P态,存储数据为“0”时,软击穿的出现不会对读“0” 操作产生影响;当MTJ1处于AP态,即存储数据为“1”时,软击穿的出现将会出现VQ1输出为“0”的情况,此时,读“1”错误率为35%。 图7 具有固定参考电阻的VCMA-MTJ读电路在t=6.67×103 h时的蒙特卡罗仿真波形 进一步地,图8给出了具有固定参考电阻的VCMA-MTJ读电路的读错误率随t的变化曲线。可以看出:读“1”错误率随t的增加而增大,这是由于在初始状态下,当MTJ1处于AP态时,Rt=RAP>R0,但发生软击穿后Rt不断减小,甚至小于R0,进而Q1电位下降速度不断加快,甚至快于Q0电位的下降速度,故读“1”错误率随t的增加而不断上升;读“0”错误率保持0不变,这是由于在初始状态下,当MTJ1处于P态时,Rt=RP 从上述分析可知,适当降低参考电阻调控单元的电阻将有利于降低读“1”错误率。为了保持读“0”正确率的同时降低读“1”错误率,本文进一步设计了一种具有参考电阻调控单元的VCMA-MTJ读电路,由R0和N6并联构成参考电阻调控单元,如图5红色虚线部分所示。当MTJ1发生软击穿后,通过增大压控端电压VG减小N6的电阻值,进而减小参考电阻调控单元的整体电阻值,将有利于降低VCMA-MTJ读电路的读“1”错误率。 图9给出了2种VCMA-MTJ读电路的读“1”错误率随t的变化曲线,其中tox=1.4 nm,VG=1.0 V。 结果表明,当t从6.67×103h增加为 6.78×103h时,具有固定参考电阻的VCMA-MTJ读电路的读“1”错误率将从35%迅速增大为70%,而对具有参考电阻调控单元的VCMA-MTJ读电路而言,其在t=6.78×103h时的读“1”错误率仅为32%。与具有固定参考电阻的VCMA-MTJ读电路相比,读“1”错误率改善达54%。因此,具有参考电阻调控单元的VCMA-MTJ读电路可有效降低读“1”错误率,可以在一定程度上削弱软击穿对VCMA-MTJ读电路的影响。 进一步地,图10给出了当t=6.78×103h时,具有参考电阻调控单元的VCMA-MTJ读电路的读“1”错误率随VG的变化,读“1”错误率E1=ξ·exp(-2.2VG)+20.5,拟合系数ξ=122 V-1。可以看出:当VG从0.4 V增大到1.2 V时,读“1”错误率呈显著下降趋势;当VG>1.2 V时,增大VG对读“1”错误率的改善幅度趋缓。通过非线性拟合可以看出,读“1”错误率与VG近似呈指数关系变化。 图10 具有参考电阻调控单元的VCMA-MTJ读电路读“1”错误率随VG的变化 综上所述,通过增大VCMA-MTJ的tox或采用本文设计的具有参考电阻调控单元的VCMA-MTJ读电路可有效降低VCMA-MTJ读电路的读错误率,从而提高VCMA-MTJ读电路的可靠性。 1) 本文基于渗透模型理论对VCMA-MTJ软击穿机理展开了深入分析,分别给出了Rt、M和Is随t的变化关系。 2) 基于上述分析,对VCMA-MTJ电学模型进行了修正,研究了软击穿对VCMA-MTJ器件性能的影响。研究表明,软击穿的出现导致Rt和M均随t的增加而降低。Ts随tox的增大而缓慢增加,随Vb的增大而迅速减少,因此,Vb是影响Ts的主要因素。此外,P态VCMA-MTJ发生软击穿的时间远短于AP态的软击穿时间且P态的M降低50%所需时间更少,因此,软击穿对P态的影响更为严重。 3) 进一步研究了软击穿对VCMA-MTJ读电路性能的影响。为了消除软击穿对P态VCMA-MTJ的影响,本文设计了一种具有固定参考电阻的VCMA-MTJ读电路。蒙特卡罗仿真结果表明,该读电路可以有效避免读“0”错误率的产生,但读“1”错误率仍会随t的增加而上升。为了进一步降低读“1”错误率,本文设计了一种具有参考电阻调控单元的VCMA-MTJ读电路。结果表明,该读电路不仅可以保持读“0”正确率,而且其在t=6.78×103h时读“1”错误率仅为32%,与具有固定参考电阻的VCMA-MTJ读电路相比,读“1”错误率的改善达54%,可以在一定程度上削弱软击穿对VCMA-MTJ读电路的影响。

2 软击穿对VCMA-MTJ性能的影响

3 软击穿对VCMA-MTJ读电路的影响

4 结论