积分映射法I/F转换电路的设计与实现

2023-12-12冯济琴邹劲松朱青松白仲熠

冯济琴, 邹劲松, 陈 程, 朱青松, 刘 杰, 白仲熠

(1.重庆理工大学 机械检测技术与装备教育部工程研究中心,重庆 400054;2.重庆工业职业技术学院, 重庆 401120;3.时栅传感及先进检测技术重庆市重点实验室, 重庆 400054)

0 引言

在捷联惯性导航系统(strapdown inertial navigation system,SINS)中,加速度计是重要的惯性元器件,其输出的模拟电流信号需要进行前端模数转换后再接入后端数字处理。常规的模数转换方式有A/D转换,V/F转换和I/F转换。A/D转换的本质为间断采样,会造成采样数据的丢失,实现高精度则依赖于A/D芯片的高位数,粗略估计需要24位AD芯片才能达到10-6g量级的转换精度[1]。V/F转换中,运算放大器的失调电压将限制电路线性度的提高,同时温度系数较大[2-3]。I/F转换基于电荷平衡的原理,对加速度计输出的电流做积分并通过模数逻辑处理通入恒定电流进行反向积分。I/F转换不受积分失调电压的影响,具有较高的转换精度,一般能达到10-5g量级,适用于中高精度惯性导航系统[4]。

传统的I/F转换电路包括积分、门限比较、逻辑控制、开关、恒流源等众多电路模块。其中,门限比较模块需要高性能双极性输入比较器,再适配特定阻值的高精密电阻才能实现对比较器电压阈值的设定[5]。电路模块众多和高性能元器件要求对I/F转换电路的转换速度、稳定性、成本提出了挑战[6]。因此,在保证I/F转换电路基本指标的前提下,设计一种简单稳定且不依赖于高性能元器件的I/F转换电路十分必要。

1 I/F转换电路原理

1.1 传统I/F转换电路原理

传统I/F转换原理如图1所示。实现方式:加速度计电流信号经电流积分器转换为电压模拟量,将该模拟量与已设定电压阈值的门限比较器进行比较,输出数字比较结果再进入数字控制电路进行数字逻辑运算。输出转换脉冲数量和数字逻辑控制信号,通过控制补偿电流的反向积分使整个模块在一个周期内达到电荷平衡,从而实现加速度模拟量到数字量的转换。

图1 传统I/F转换原理示意图

1.2 基于积分映射法I/F转换电路原理

基于积分映射法I/F转换电路的关键在于积分映射电路。该电路的功能是将第一级积分电压按照所设计的放大系数映射到控制芯片的TTL标准电压内。其中,放大系数通过推挽电路加适配负载来实现系数设定。积分映射电路的设计取决于控制芯片的选型、电路分辨率要求、电路整体功耗要求等。通过积分电压值的放大映射,在硬件层面上利用控制芯片IO脚电压识别特性,在逻辑上实现了控制芯片同时进行比较、逻辑控制两功能。

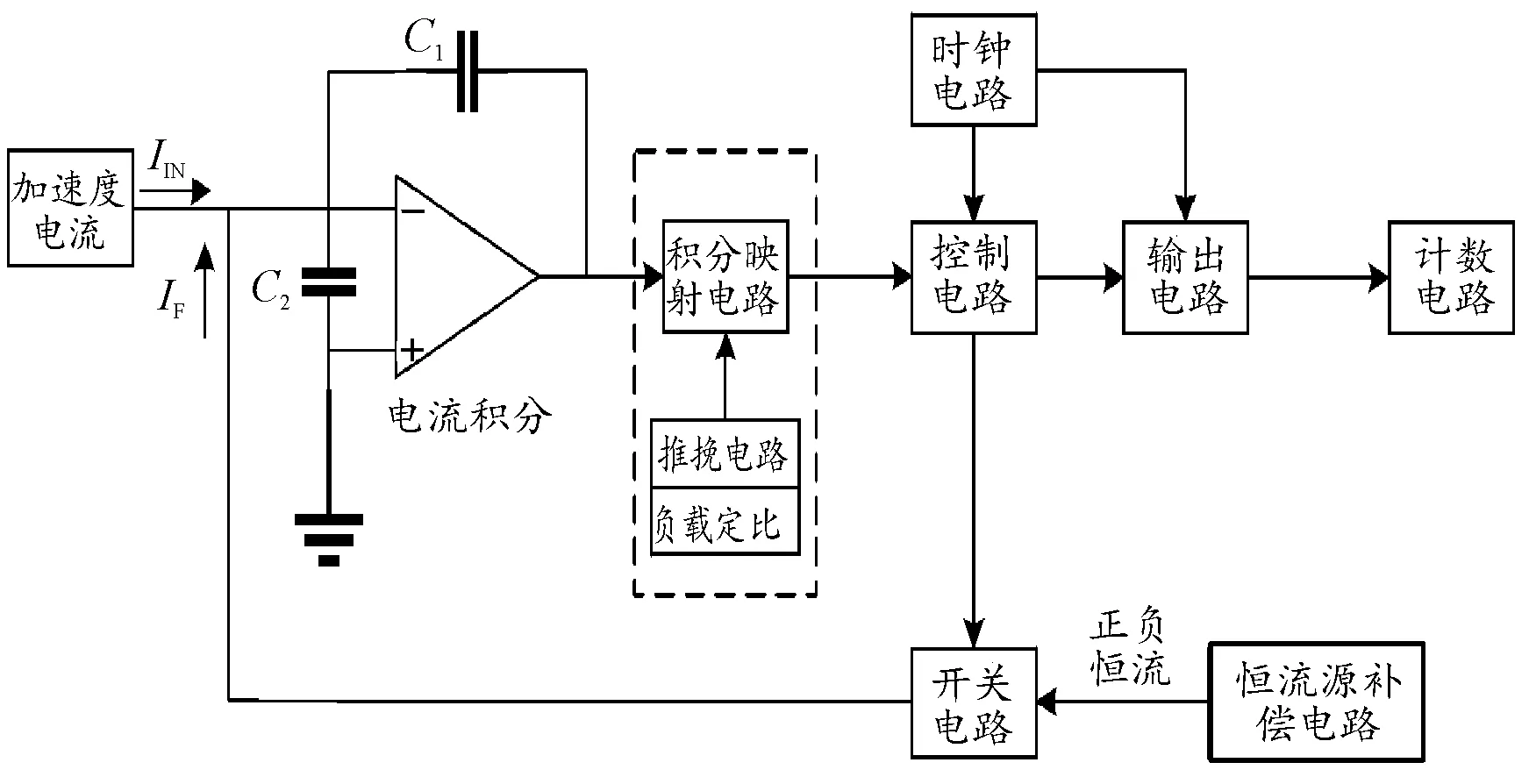

I/F转换电路基于电荷平衡原理[7-10]。基于积分映射法I/F转换电路原理如图2所示。

图2 积分映射I/F转换电路原理示意图

电流积分器对输入电流IIN与反馈平衡电流IF的差值在一定时间内通过积分电容C1进行积分取样,并将取样结果与设定的正(或负)门限电平进行同步比较。对于不平衡的比较结果,控制电路控制开关电路接通对应的正(或负)反馈恒流源,以形成若干个持续时间均为一个工作时钟周期T的反馈单位电荷对原取样结果进行再平衡。与此同时,控制电路输出相应数量且与输入电流极性对应的脉冲。对于平衡的比较结果,控制开关电路关断反馈恒流源和脉冲输出。上述过程在每个工作时钟周期T内同步进行1次,使电流积分器的输出电压保持在设定的正/负门限电平之内,即电路保持平衡。此时:

QIN=QF

(1)

在t时间内IIN累积的电荷量为

QIN=IIN×t

(2)

(3)

由式(3)可得输入电流IIN为

(4)

其中:F为单位时间内的输出脉冲数(pulse/s)。

由式(4)可知,只要保证恒流源I与工作时钟频率f为常值,在忽略各种误差的情况下,输入电流IIN就与单位时间内的输出脉冲数F成正比[11]。根据单位时间内的输出脉冲数,利用函数关系式(4)即可得出输入电流IIN的值。

2 电路模块及程序设计

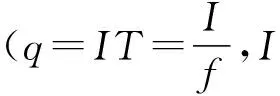

2.1 恒流源电路设计

由I/F转换电荷平衡原理可知,恒流源电路为反向积分提供电流基准,直接影响脉冲计数的精确性。设计高精度、高稳定性和高对称性的恒流源模块是保证I/F转换电路精度的根本保障。温度是影响恒流源模块稳定性的主要因素,当温度变化时会影响PN结的穿透电流,使得恒流源电流发生变化。在实际应用中,为了促进精度的提升,需要基于恒压器件进行恒流源模块的设计[12-13]。

基于恒压源(LM199AH)的压控来提升恒流源精度。 LM199AH采用次表面隐埋技术,稳定性高、噪音低、受温度影响小[14]。参数如下:电压值为6.8~7.1 V,温度系数为3×10-7~1×10-5,长期稳定性典型值是2×10-5/1 000 h。在恒流源模块电压端设计时,把采样电阻的供电电压与运算放大器的基准电压统一,防止产生信号流对地电压不足的问题。对于电路中运放的选择,用场效应管来替代传统的晶体管,使得放大倍数、驱动能力和基极电流得到有效提升。详细电路如图3所示(A1、A2标号相同处表示实际物理连接)。

图3 恒流源电路图

2.2 积分映射电路设计

积分映射电路的功能是将第一级积分后的模拟电压值经推挽电路通过适配不同电阻对,定比例放大到CPLD芯片引脚识别的TTL标准内,实现积分电压值的定比例转换。通过这种积分电压映射设计,TTL比较的数字结果直接进入CPLD进行数字逻辑解算,CPLD实现了比较、逻辑解算两大功能。相较于传统I/F转换电路需要专用比较器输出数字比较结果、再进入CPLD进行数字逻辑解算,本设计可节约一个环节的信号处理时间,降低一个环节带入的误差量,减少一个环节的电路元器件数量,提高电路可靠性,实现快速比较。本设计基于I/F转换电路分辨率要求、线性度要求,在CPLD芯片选型之后再选择不同阻值的电阻对来实现设计目标。

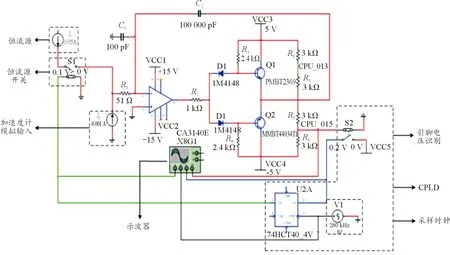

根据CPLD(EPM7064SLC44-10N)的TTL标准芯片手册可知:输入电压大于2 V识别为高电平,输入电压小于0.8 V识别为低电平。积分映射电路如图4所示。

图4 积分映射电路图

X1接加速度计信号输出端,U5_2接恒流源电路,cpu_013、cpu_015接CPLD芯片输入引脚。电路工作过程为:当没有加速度电流信号时,即X1输入为0 mA。经过运算放大器U1反向积分,U1的输出电压为0 V(U0)。推挽电路负载电阻值依次为R19=R20=R21=3 kΩ,R22=30 kΩ。因此,0输入时:

(5)

(6)

Ucpu _013=2.5 V,Ucpu_015=-0.455 V。

Ucpu_013=2.5 V,电压值大于1.7 V,根据CPLD的引脚TTL标准,cpu_013对应的CPLD输入端(标记为CPLD_13)被识别为高电平。同理,Ucpu_015=-0.455 V,电压值小于0.8 V,cpu_015对应的CPLD输入引脚端(标记为CPLD_15)被识别为低电平。

当X1端输入正电流信号时,经过运算放大器U1进行反向积分,输出为负电压,即U0<0 V。再由式(5)和式(6)计算得到cpu_013、cpu_015的电压值,根据CPLD的TTL标准就可以比较出对应的输入电平信号。输入正电流信号持续反向积分时,运算放大器U1输出端U0<0 V,且绝对电压值不断增加。由式(5)可知,cpu_013端电压值不断减小,直到Ucpu_013<1.7 V,CPLD_13引脚被识别为低电平,此时Ucpu_015<0.8 V,整个积分过程中CPLD_15引脚一直被识别为低电平。持续积分直到CPLD_13引脚处发生电平跳转,CPLD通过逻辑控制接通恒流源补偿电路,即U5_2输入负恒定电流。再通过反向积分,拉高Ucpu_013的电压值,使CPLD_13引脚回到初始高电平。当小电流输入时,恒流源补偿的频次低;大电流输入情况下,恒流源补偿频次高,通过对恒流源通断进行脉冲计数实现电流与频率的线性变换。

当X1端输入负电流信号、运算放大器U1反向积分后,输出为正电压。U0电压值不断增大,由式(6)可知cpu_015电压值不断增大,直到Ucpu_015>0.8 V,CPLD_15引脚被识别为高电平,此时Ucpu_013>1.7 V,CPLD_13引脚一直被识别为高电平。CPLD_15引脚处发生了电平跳转,通过逻辑控制U5_2输入正电流进行补偿。拉低Ucpu_015的电压值,使CPLD_15回到初始电平状态,频率计数方式同上。

2.3 CPLD程序设计

CPLD程序设计包括用Verilog HDL语言描述FPGA逻辑过程,再经过Modlesim时序仿真,考虑布局布线延时后是否能实现逻辑功能。

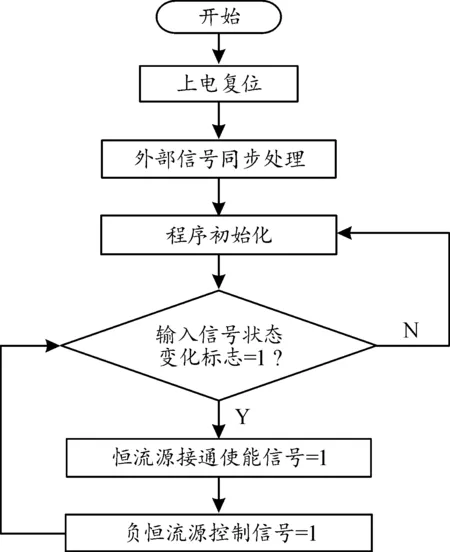

CPLD对六路加速度信号进行数字逻辑并行处理,每路信号实现如图5所示。CPLD芯片系统断电后程序不丢失,上电复位后,首先进行外部信号同步处理,避免后续逻辑判断过程中产生亚稳态,然后进行初始化程序[15]。

图5 加速度计信号处理流程

3 功能仿真与实验验证

3.1 功能仿真

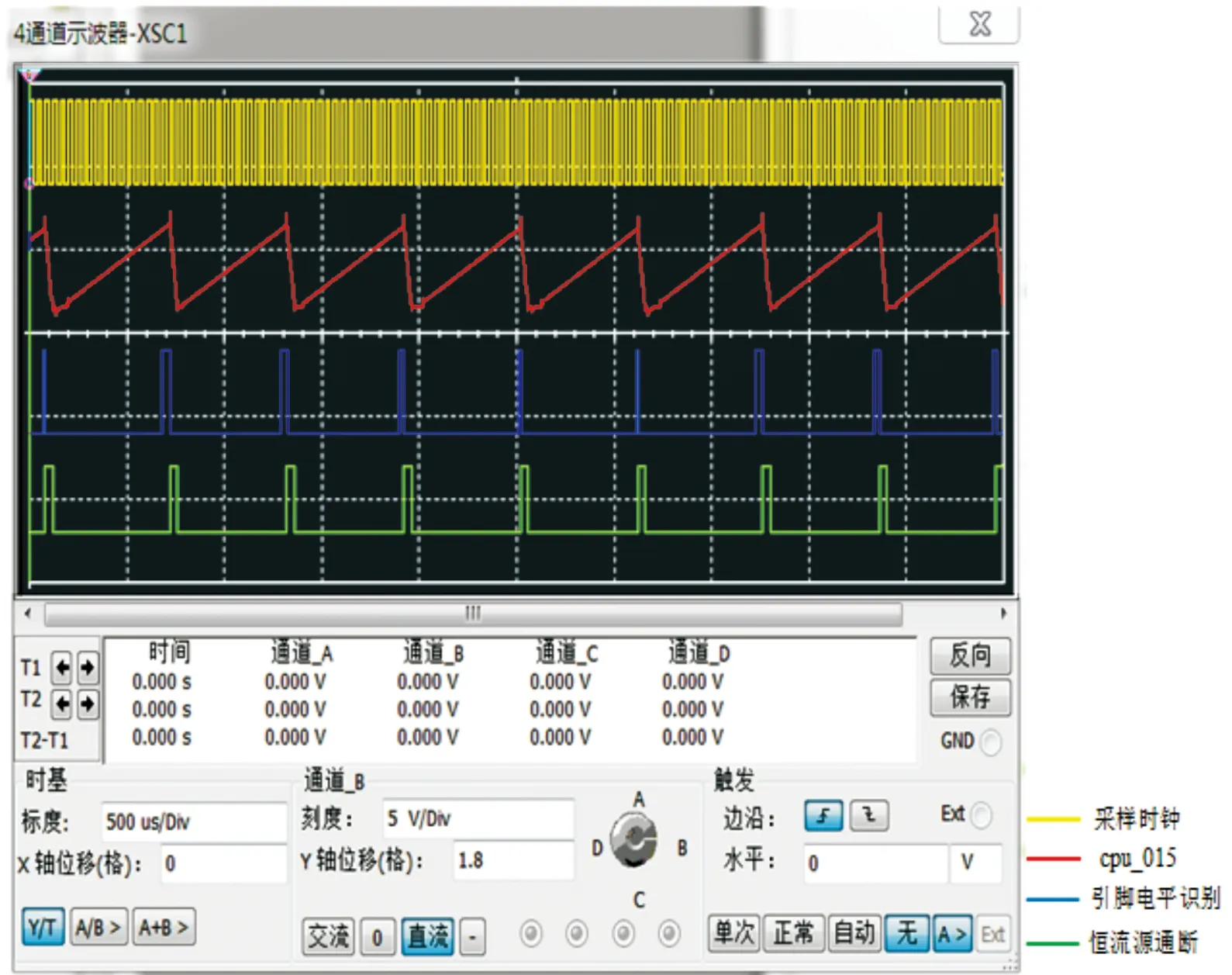

用Multisim搭建积分映射电路功能仿真模型,如图6所示,仿真模拟-1 mA的加速度计模拟信号输入,实际工作过程中该电流信号是连续不断变化的。对积分定映射电路中的元器件进行模型化处理:用DC-Current直流电源模拟恒流源;积分电路的运算放大器选取5端运放器件CA3140E;压控开关S2模拟CPLD芯片管脚电压识别过程,即引脚电压超过该压控开关触发电压时,开关状态跳转,接通或关断恒流源电路;D触发器74HC740模拟CPLD芯片数字信号逻辑解算;电压源Clock Voltage Source用来模拟CPLD不同的采样频率。最后用示波器XSC1抓取cpu_015的电压与压控开关S2的通断状态。仿真结果如图7所示。

图6 积分映射电路仿真模型

图7 XSC1示波器界面

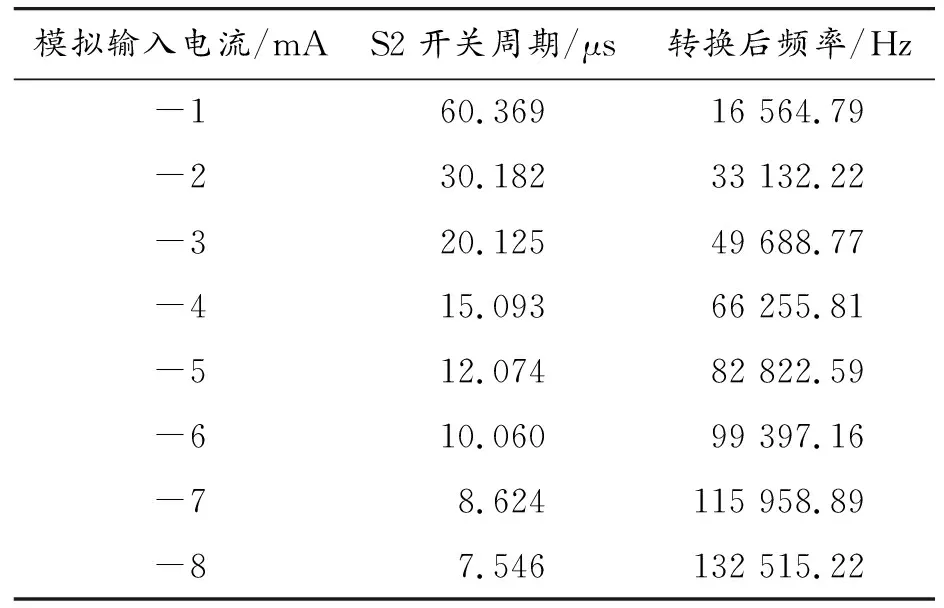

从图7可得,当cpu_015电压积分到压控开关S2的触发电压时,压控开关接通,通入对应的恒流源进行补偿,下拉电压值。1个时钟周期后,开关断开,继续进行原积分过程。由仿真波形可知,恒定电流输入时,I/F转换电路的工作过程与预期相符。进一步仿真输入不同电流信号时的电路工作情况,同时记录压控开关S2接通的周期,得到表1。

表1 不同模拟输入的仿真结果

由表1可以看出,模拟输入的电流越大,压控开关开通的频率越快。输入电流和转换后频率为正比关系,通过计数器检测压控开关的通断频率,即可求出输入电流信号的值。

3.2 实验验证

3.2.1实验系统

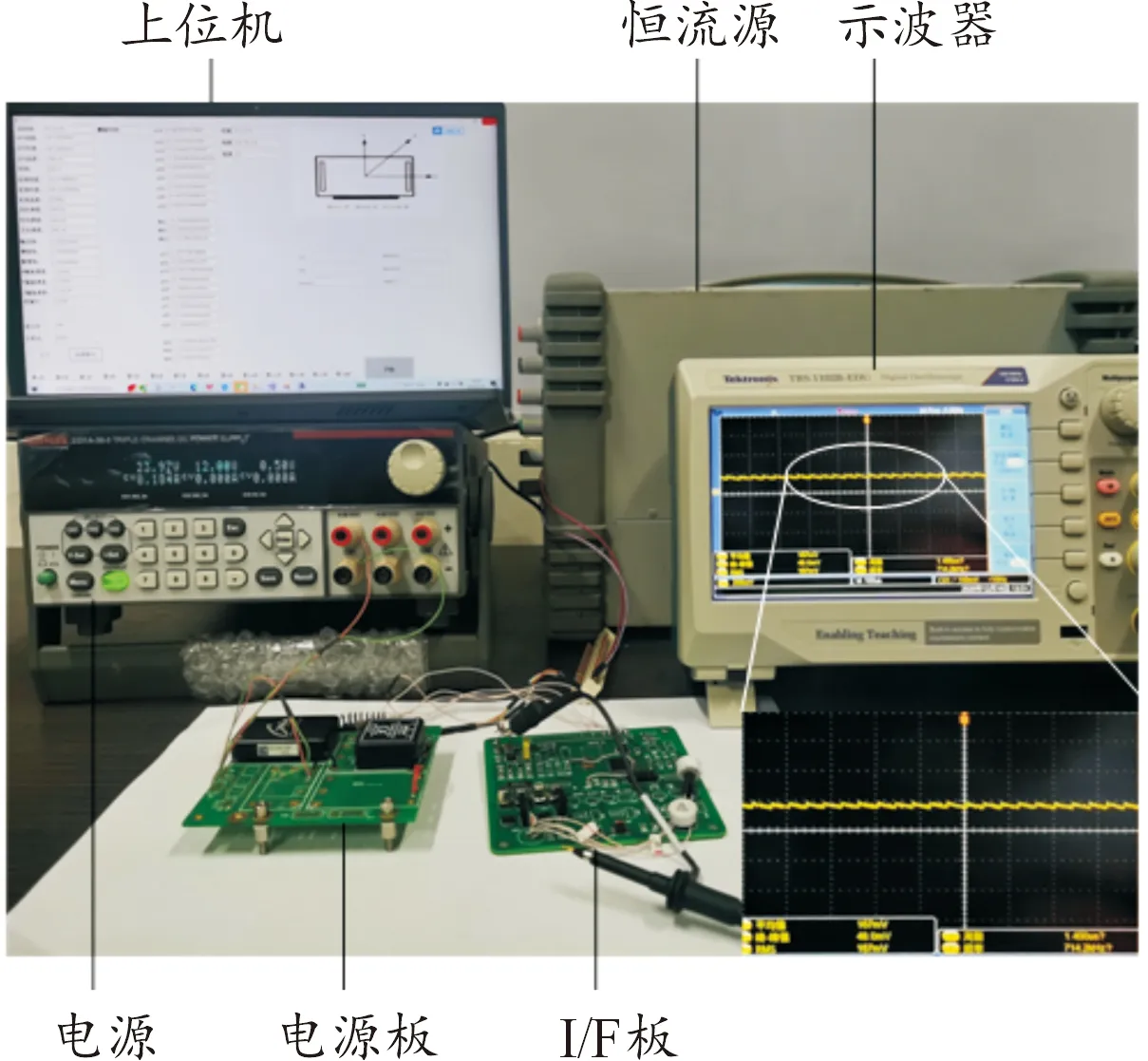

实验系统如图8所示,超稳定高精度恒流源提供测试电流模拟加速度计任意电流输入,用自制高精度、低噪声的I/F电源板给I/F转换电路供电,用示波器抓取电路信号进行功能检测,最后通过上位机软件保存分析数据[16]。实验系统实物见图8。

图8 实验系统实物

3.2.2零位和零位稳定性测试

将I/F转换电路置于恒温25 ℃条件下,对电路的零位、刻度因数和线性度等参数进行测试。启动电路30 min后对电路进行测试,令输入电流为IIN=0 mA (输入接地),每隔ΔT=20 s记录计数器的脉冲数,持续1 h,共记录n=180个零位数据Ni,三通道零位数据如图9所示。

图9 三通道零位数据曲线

(7)

(8)

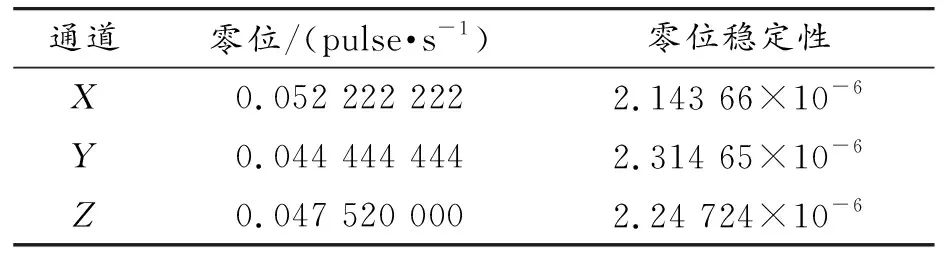

由式(7)和式(8)的计算结果,得到三路I/F电路零位和零位稳定性如表2所示。

表2 三路I/F电路零位和零位稳定性

从表2可知,设计的I/F转换电路3个通道的零位均值优于0.04 pulse/s,零位稳定性优于2.143 66×10-6。

3.2.3刻度因数和线性度测试

启动电路30 min后,打开高精度电流源给X、Y、Z三个通道输入不同大小的电流量,采样时间ΔT=1 s,记录恒流源开关通断的脉冲次数,得到输入电流与脉冲关系如图10所示。输入负电流信号时,将脉冲数记为负。

图10 输入电流与脉冲关系曲线

(9)

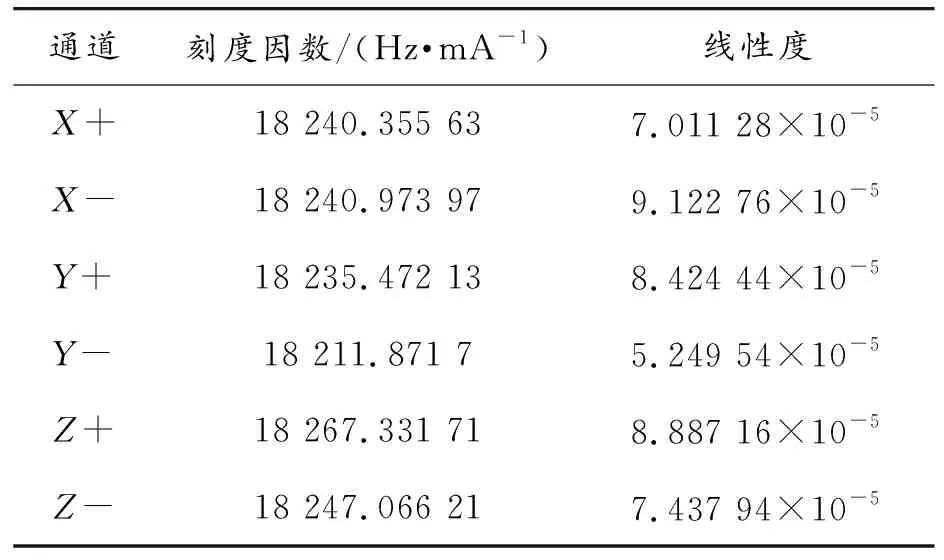

由式(9)计算得到设计的I/F电路的刻度因数和线性度结果如表3所示。

表3 本方案I/F电路的刻度因数和线性度

由表3可以得出所设计的I/F转换电路的刻度因数为18 250 Hz/mA,线性度小于10个ppm。

4 结论

所设的I/F转换电路计电路零位稳定性优于2.143 66×10-6,线性度小于10个ppm,实现了I/F 转换电路的高线性度和高零位稳定性,可应用于中高精度捷联惯导系统加速度计信号处理。所提出的积分映射方法在特定积分信号处理领域具有应用价值。