深亚微米SOI 工艺高压ESD 器件防护设计*

2023-10-25朱琪黄登华陈彦杰刘芸含常红

朱琪,黄登华,陈彦杰,刘芸含,常红

(中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

1 引言

高压(HV)集成电路在新能源汽车电子、工业控制、开关电源、电源管理产品以及电机驱动等领域发挥了关键作用。静电放电(ESD)已成为评估产品性能的一项重要的可靠性指标,ESD 脉冲对芯片放电会产生瞬间大电流和瞬间高电压,如果无法及时泄放,大电流会使内部器件PN 结热损毁,金属熔断;高电压会使绝缘层击穿漏电,最后导致内部的器件及整个电路永久性损伤,还会影响到关键器件的性能和电路的功能。绝缘体上硅(SOI)与体硅技术相比具有寄生效应相对较小、功耗低、耐高温、无闩锁等一系列优势,所以在集成电路设计中会被优先考虑[1]。SOI CMOS 工艺在工艺制程中采用全介质隔离技术,绝缘层使器件在工作时产生的热量无法及时、均匀散出,限制了ESD 器件的防护能力。文献[1]的研究结果表明,深亚微米工艺条件下,体硅工艺的ESD 防护能力比SOI 工艺器件的ESD 防护能力高一倍,ESD 器件防护能力弱已极大地限制了SOI 工艺在一些领域发挥优势,也成为了一个亟待突破的技术瓶颈。

本文介绍了一款采用深亚微米SOI 工艺驱动MOSFET 的控制器芯片,研究、分析了SOI 工艺高压ESD 器件的特性和工作性能,对端口电压进行了ESD防护器件的选择,通过“设计-测试-改进-试验”的方法,找到了适合端口的保护结构。

2 深亚微米SOI 工艺高压器件特性分析

SOI 工艺是一种全介质隔离技术,工艺器件与衬底之间被一道绝缘埋氧层隔离,同时隔离填塞的氧化物是热绝缘体,当某个功能模块中的器件工作时,绝缘埋氧层能阻隔器件有源区产生的热量,导致热量无法及时散发,最终顶层硅膜温度逐渐升高,这就是SOI工艺器件的自加热效应[2]。自加热效应对ESD 防护器件的可靠性设计影响很大,热量不能及时散出还会产生其他破坏,如导致金属温度逐渐升高、金属熔断和热击穿现象。

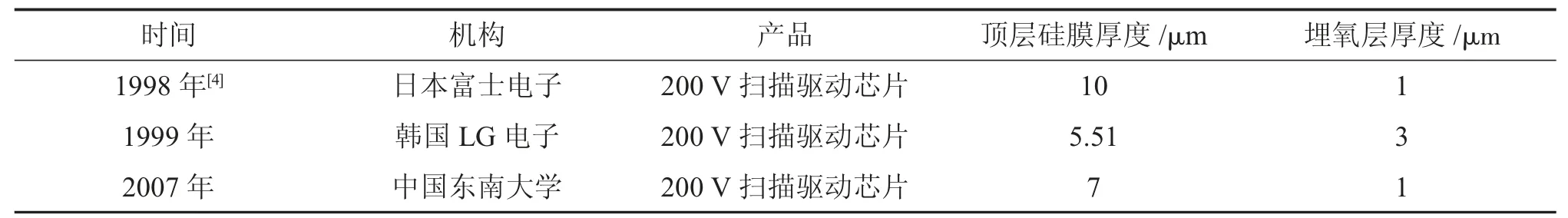

根据SOI 的硅膜厚度将器件分为厚膜器件和薄膜器件。对于厚膜SOI 器件,当最大耗尽宽度大于SOI硅膜厚度的2 倍时,称之为部分耗尽器件;对于薄膜SOI 器件,当最大耗尽宽度小于SOI 硅膜厚度时,称之为全耗尽器件[3]。SOI 工艺的厚膜器件比薄膜器件具有更大的电流密度,可以相应提高电路工作时的带负载能力及优势。部分采用SOI 工艺的高压驱动芯片的硅膜厚度对比如表1 所示,SOI 厚膜工艺已发展成高压芯片的首选工艺。

表1 部分采用SOI 工艺的高压驱动芯片的硅膜厚度对比

埋氧层与衬底隔离,氧化物又是热绝缘体,设计时需考虑自加热效应带来的不良影响,因此本文采用顶层硅厚度为3.5 μm、埋氧层厚度为1 μm 的薄埋氧层SOI 材料。

3 高压ESD 防护器件的特点

高压静电的防护原理与低压静电的防护原理是一样的,都是利用低阻抗的泄放通路将静电放电时产生的瞬间大电流及时泄放,同时静电放电的电流或电压自然地降低至击穿点以下。

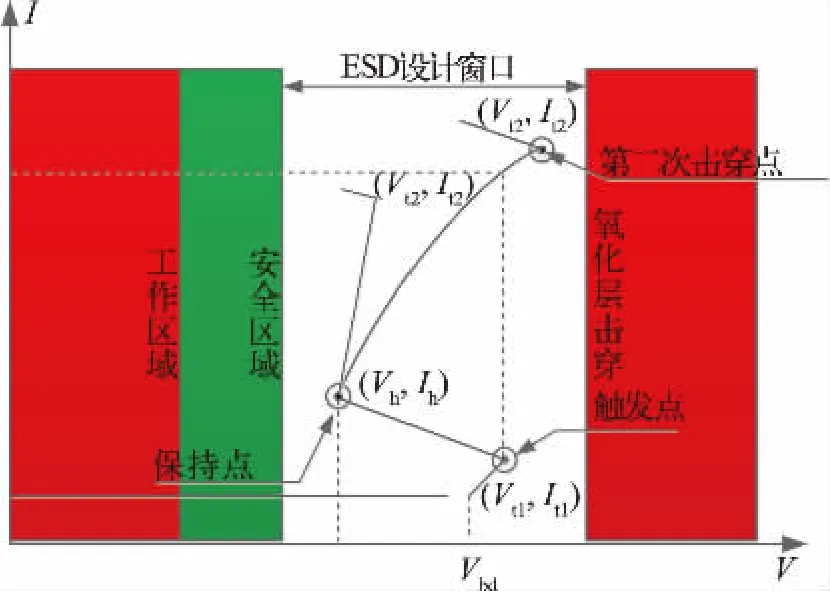

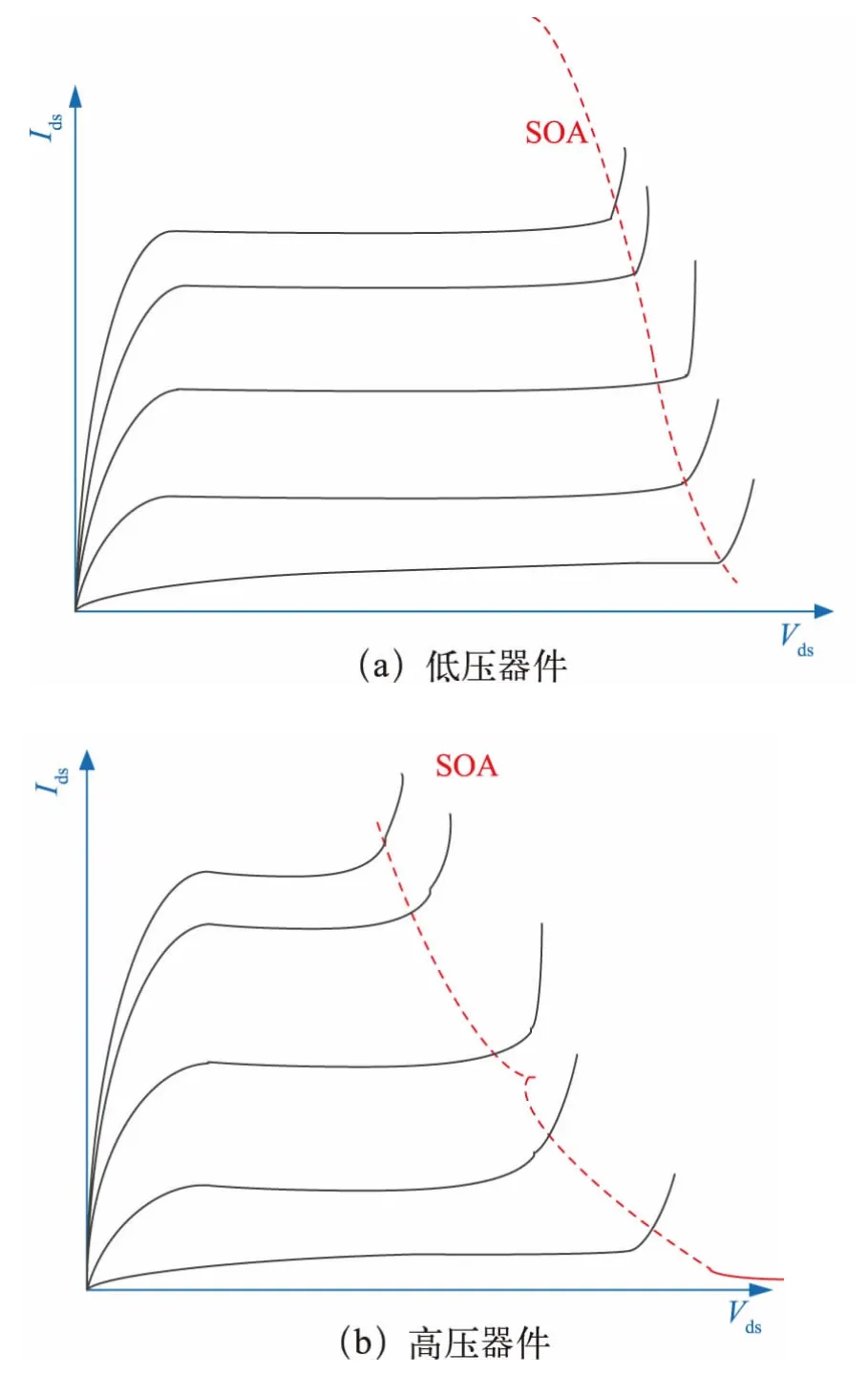

典型的ESD 保护器件I-V特性曲线如图1 所示,当在PAD 上加ESD 正向脉冲时,高静电电压加在漏结上,该结与衬底发生反偏,器件进入高阻抗状态,直到发生雪崩击穿,雪崩击穿电压为Vbd,在图1 中对应一次击穿电压Vt1并产生ESD 电流It1。所以器件在高压工作状态下,需要同时考虑电路内部的高压器件和外围的高压ESD 器件。内部器件的结击穿电压和栅氧击穿电压应该比外围控制器件的Vt1、维持电压Vh以及ESD 保护器件的Vt1大,这样内部电路就可以更有效地被保护;而工作电压VDD应该比Vh小,此时Vh是一个较低且安全的电压点,这时维持电流Ih也在较低的电流点,防止产生闩锁效应,在ESD 事件发生时,以保证器件具有好的稳健性。当电流继续上升,在漏端附近产生局部“热点”,流过器件漏端的电流密度过大,就会造成不可恢复性热击穿,热击穿对应图1 中的二次击穿电压Vt2,It2为失效电流。低压器件和高压器件的特性曲线如图2 所示,Vds为源漏电压,Ids为源漏电流,高压器件的ESD 保护窗口由高压器件的安全工作区域(SOA)特性曲线限定,其有很强的快速电压折回特性,且明显被压缩了。因此,在ESD 脉冲条件下,窗口上限和下限是应力条件的强函数。

图1 典型的ESD 保护器件I-V 特性曲线

图2 低压器件和高压器件的特性曲线

4 SOI 工艺高压ESD 器件防护设计

高压ESD 器件设计时通常会选用高压二极管、高压三极管、 高压MOS、SCR (Silicon Controlled Rectifier)等。高压二极管利用二极管的单向导通性,其设计简单,开启速度快,没有电压折回现象,容易满足Vt1大于VDD的条件,但二极管的反向稳健性极低,不能作为高压ESD 防护器件使用。高压工艺中的高压MOS 管也是高压静电防护设计中常用的器件,但高压NMOS 的ESD 性能是由寄生NPN 决定的,表现出典型的深度电压折回特性,伴随寄生NPN 的非均匀触发,容易引起器件损伤或失效。高压三极管一般分为NPN 管和PNP 管2 大类,而NPN 管和PNP 管的电压也是有规律的(处于放大状态时),当NPN 管的集电极(C)电压VC、基极(B)电压VB和发射极(E)电压VE满足VC>VB>VE时,发射极电位最低,集电极电位最高;当PNP 管满足VE>VB>VC时,集电极电位最低,发射极电位最高。三极管可以看作2 个PN 结,NPN 管要导通则需要2 个PN 结处于正偏电压,NPN 是用基极-发射极的电流IB控制集电极-发射极的电流IC,E 极电位最低,且正常放大时通常C 极电位最高,即VC>VB>VE,所以电流的流向是由C 极流向E 极。B 极是控制脚,B极的电流流向E 极。PNP 是用发射极-基极的电流IB控制发射极-集电极的电流IC,E 极电位最高,且正常放大时通常C 极电位最低,即VE>VB>VC,所以电流的流向是由E 极流向C 极。B 极是控制脚,E 极的电流流向B 极。当静电放电时,NPN 管是电压折回型器件,而NPN 管的β 系数比PNP 管大很多,PNP 管基本没有快折回功能。高压NPN 管触发电压高,维持电压也高,且电压越大,失效电流越低,稳健性越弱。

本文设计的一款驱动MOSFET 的控制器电路,其端口最高工作电压为115 V,根据端口工作电压,采用工艺推荐的开放式基极堆叠三极管结构作为ESD 防护结构,该低压横向PNP 晶体管结构具有PNP 管的放大原理和弱折回特性,同时开放式基极堆叠结构具有对称的夹钳行为且有强的抗闩锁性能。

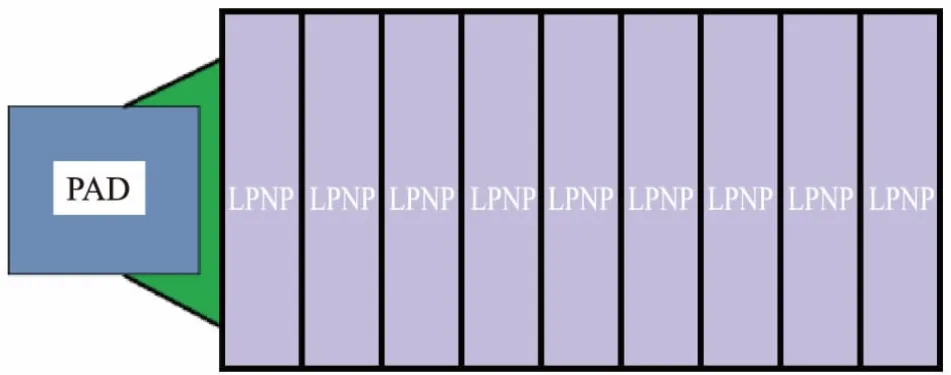

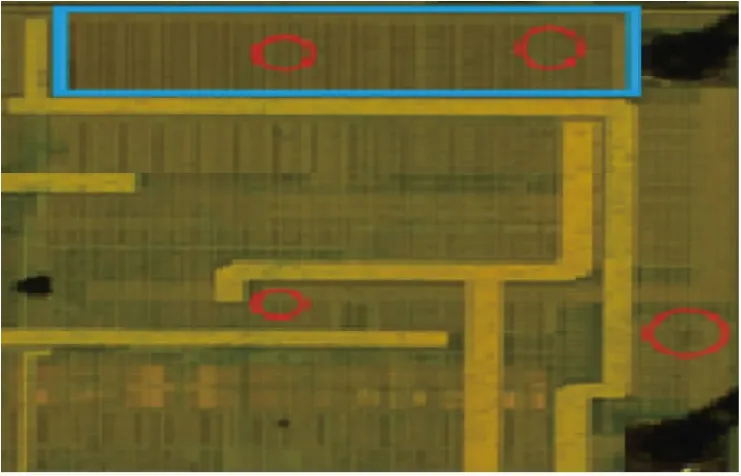

高压端口ESD 防护器件采用堆叠三极管设计,根据端口最高工作电压选取了N级级联结构(根据工作电压推算),堆叠三极管块状布局如图3 所示,其由多个金属层并联构成,以提供高电流能力和低串联电阻。

图3 堆叠三极管块状布局

5 全芯片ESD 防护网络布局设计

根据代工厂对全芯片ESD 防护网络的分析,要求VDD 总线和GND 总线的金属宽度至少为50 μm,以减小总线的寄生电阻。从I/O 端口到VDD/GND ESD泄放路径等效电阻不应超过3 Ω。如金属的单位电阻为100 mΩ/□,金属宽度为50 μm,则VDD/GND 到I/O 端口的总线距离限制为1 500 μm,如果超过限定,应在满足尺寸要求的情况下适当增加ESD 防护器件,以进一步降低ESD 泄放路径的等效电阻。

6 试验测试结果与分析

用本设计的电路进行标准流程人体模型(HBM)ESD 测试,第一次共测试3 颗芯片,ESD 起始电压为2 kV,步进电压为500 V。3 颗芯片在打击试验前经测试验证,功能正常,性能指标符合要求。经ESD 打击试验后,各端口ESD 电压超过500 V 时损坏。随后又选取3 颗芯片进行打击试验,ESD 起始电压为500 V,步进电压为100 V。各端口ESD 电压超过400 V 时就会随机损坏,ESD 电压未达到HBM 2 000 V 的要求。

6.1 ESD 器件失效分析

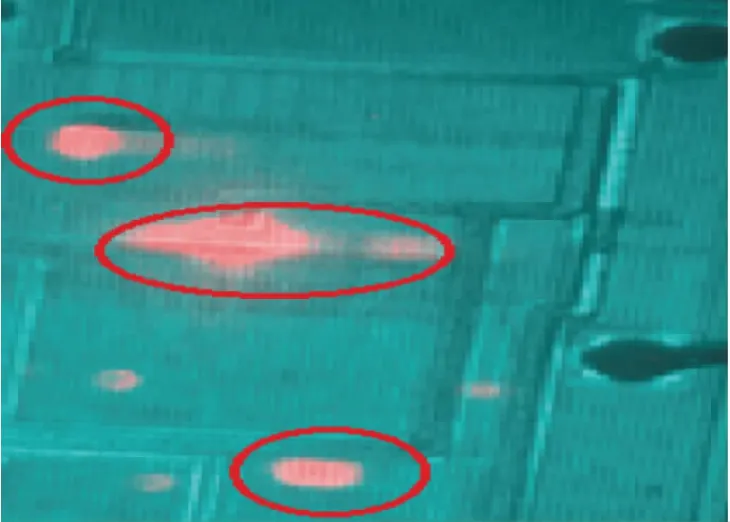

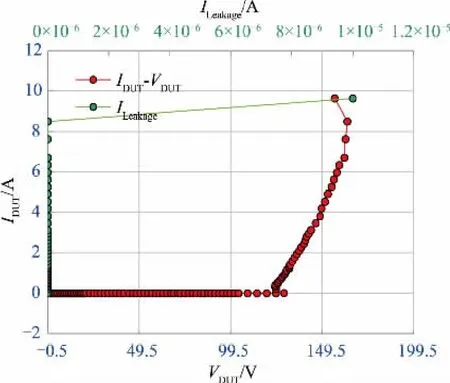

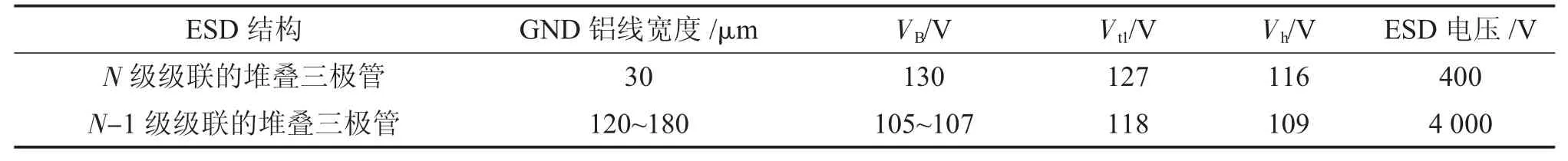

该电路开盖后经过光学显微镜(OM)、微显微镜(EMMI)定位分析,图像如图4、5 所示,再对该电路进行打击传输线路脉冲(TLP)曲线分析,如图6 所示。待测器件(DUT)在短时间的脉冲波形下进行电压和电流特性的测量,图6 中VDUT和IDUT分别为待测器件的电压和电流,ILeakage为漏电流。通过TLP 曲线锁定到ESD 失效是因为高压端口ESD 器件损坏或未起作用,导致高压和大电流灌入内部电路,引起器件击穿烧毁。端口ESD 器件采用N级级联三极管结构,TLP 曲线工作在SOA 内,因此曲线正确,但ESD 的Vt1为127 V,Vh为116 V,高于内部100 V 高压器件的击穿电压VB(≥110 V)。同时,硅膜厚度是SOI 工艺设计的一个关键参数[5],在相同的功耗下,随着硅膜厚度的减小,散热能力下降,SOI 工艺散热性不如体硅,导致大量热量积累在P 阱中[6],存在风险。

图4 OM 试验定位图

图5 EMMI 试验定位图

图6 N 级级联三极管TLP 曲线

6.2 全芯片ESD 防护网络布局分析

对该电路进行全芯片ESD 防护网络布局分析,发现2 点问题:1)版图设计时GND 地线没有形成完整的环路,打击ESD 时没有形成完整的低阻电流泄放通路[7];2)GND 线宽不够,宽度仅为30 μm,有些地方小于30 μm,铝线太细导致寄生电阻太大,承受不住打击试验时产生的瞬间大电流。

通过以上的分析对版图进行改版设计,端口ESD器件采用N-1 级级联三极管结构,通过聚焦离子束(FIB)试验,把最后一级级联三极管短接到GND,并利用短接并联铝线作为ESD 接地总线,使得该ESD 器件接地铝线更粗,寄生电阻更小。经过TLP 测试将ESD 器件的击穿电压降低至105~107V,Vt1降为118 V,Vh降为109 V。设计连接全芯片各端口形成完整的泄放环路,增加各端口高压ESD 器件接GND 铝线的宽度,最细的铝线为120 μm,最宽的铝线达180 μm。最后对3 只改版流片后的电路进行HBM ESD 测试,ESD 改版前、后的测试结果如表2 所示,电路通过HBM ESD 4 000 V 的要求。

表2 ESD 改版前、后的测试结果

6.3 设计结构测试分析

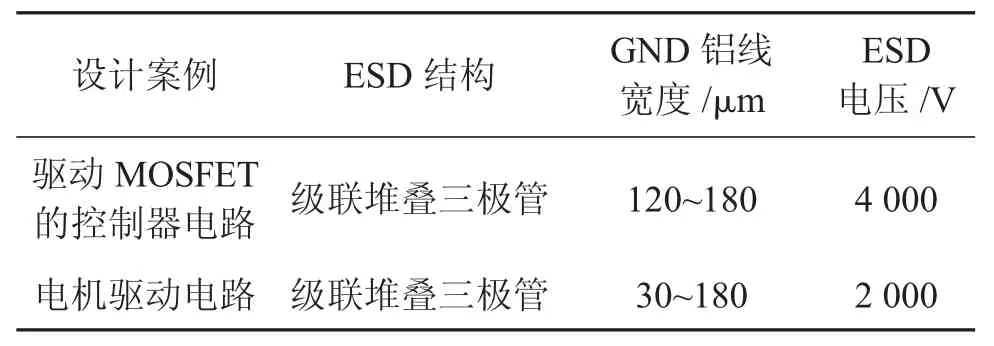

对本设计的驱动MOSFET 的控制器电路与一款采用同类设计的HBM ESD 电机驱动电路的测试结果进行比较,结果如表3 所示。

表3 2 款驱动电路ESD 测试结果对比

2 款电路的高压端口都采用了0.18 μm SOI 高压ESD 器件防护设计,由于电机驱动电路设计时面积布局的限制,部分端口接GND 的铝线宽度只有30 μm左右,ESD 泄放通路中铝线寄生电阻偏大。通过对比发现,采用本设计结构的0.18 μm SOI 工艺可以满足高压端口的ESD 防护要求,同时通过减小ESD 泄放路径的寄生电阻,合理布局ESD 器件,能进一步提升HBM ESD 的测试结果。

7 结论

深亚微米SOI 工艺高压ESD 器件设计时需要从工艺、器件、可靠性等方面考虑很多问题。本文通过测试试验分析出高压ESD 器件适合端口的击穿电压和触发电压,并通过增加GND 铝线宽度来降低寄生电阻。流片试验结果表明,采用开放式基极堆叠三极管结构作为高压ESD 器件防护结构时,需要考虑端口工作电压与ESD 器件触发电压的匹配性,还要提供完整的低阻电流泄放通路。

该驱动MOSFET 的控制器电路采用ESD 结构,在110 V 电源下,通过了4 000 V HBM ESD 测试。电路内部高压器件没有发生击穿漏电现象,产品工作稳定、性能可靠,并且整体性能良好,有效提升了SOI 工艺高压ESD 器件防护稳健性弱的问题。