用于GaN 半桥驱动的高可靠欠压锁定电路*

2023-10-25李亮周德金黄伟陈珍海

李亮,周德金,黄伟,陈珍海

(1.苏州市职业大学电子信息工程学院,江苏 苏州 215104;2.清华大学无锡应用技术研究院,江苏 无锡 214072;3.复旦大学微电子学院,上海 200433;4.黄山学院智能微系统安徽省工程技术研究中心,安徽 黄山 245041)

1 引言

GaN 高电子迁移率晶体管(GaN HEMT)与硅晶体管器件相比具有显著的优势,更适于工作在高温、高压及高频的应用场合,因此GaN 的驱动芯片技术已成为研究热点[1-4]。在高压电路驱动对象为大功率GaN半导体器件时,需要在电路系统出现异常时快速关闭系统控制信号,因此通常需要在高压集成电路内部集成过温保护、欠压锁定(UVLO)等电路[5-8]。欠压锁定电路是高压栅驱动芯片内部常用的保护电路,当芯片供电电压很小时,不会造成功能模块电路的损坏,但是各功能电路不能稳定工作,会使电路系统出现处理数据错误或者控制逻辑异常[9-12],因此,GaN 栅驱动芯片一般集成UVLO 电路。当供电电压降低并且低于供电下限时,UVLO 信号输出从而关闭电路。鉴于高压栅驱动集成电路越来越受欢迎以及电路安全保护的需要,本文设计了应用在GaN HEMT 高压半桥驱动芯片中的高可靠UVLO 电路,以解决反馈回路造成的开关噪声引起的电路不稳定问题。

2 电路结构

2.1 半桥电路

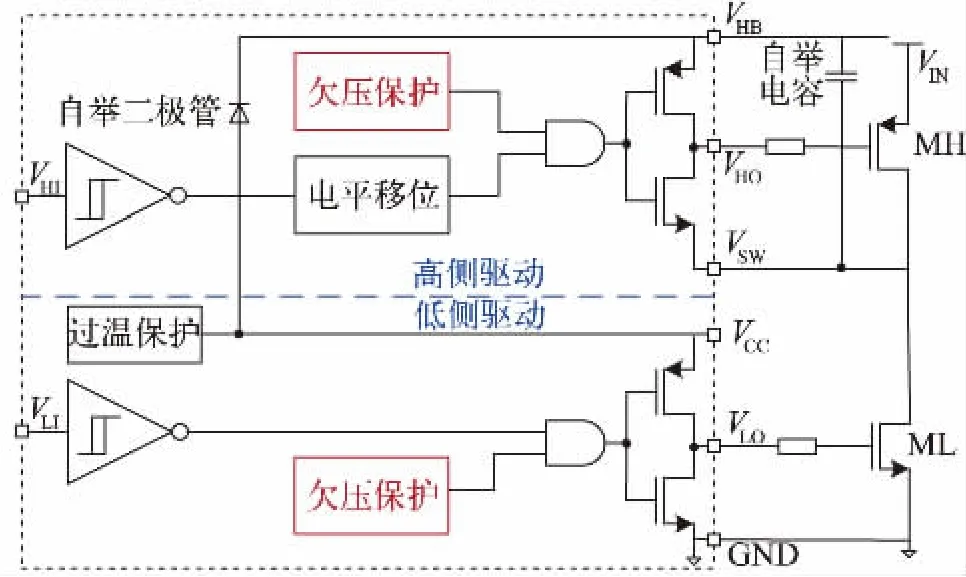

半桥驱动的电路结构如图1 所示。电路分为高侧驱动和低侧驱动,驱动信号直接控制GaN 功率器件MH 和ML 的栅极。VCC为供电电压,VHB/VSW为高侧浮动电源轨的高/低电压,VHI/VHO和VLI/VLO分别为高侧驱动和低侧驱动的输入/输出电压。为了保证电路功能的正常实现,高侧与低侧电路都需要UVLO 电路。另外,高侧驱动电路中,自举电容两极板的驱动电压始终在VHB和VSW之间摆动,导致高侧电路电源电压和衬底电位存在波动,产生噪声毛刺。因电源电压也存在供电不足的问题,需要在电压波动的影响下集成包含电源毛刺检测的UVLO 电路。

图1 半桥驱动的电路结构

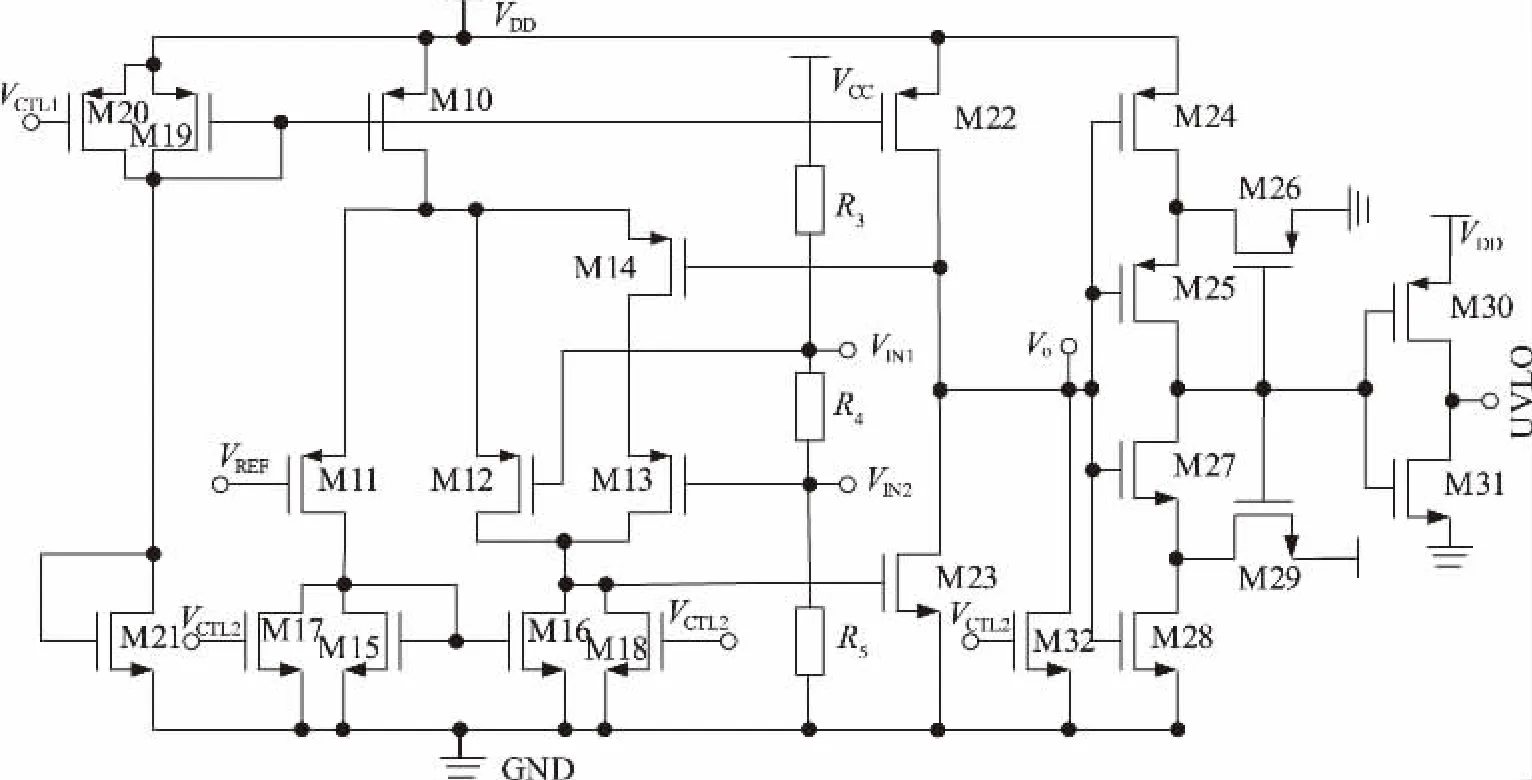

2.2 UVLO 电路结构

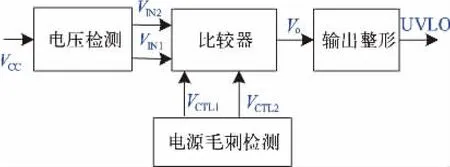

UVLO 电路结构如图2 所示,它包括电压检测、比较器、电源毛刺检测和输出整形电路。当VCC欠压时,欠压保护信号UVLO 为低电平;当电源毛刺检测电路检测到电路不稳定时,输出控制信号VCTL1为低电平、VCTL2为高电平,UVLO 为低电平;当电路正常工作时,UVLO 为高电平。

图2 UVLO 电路结构

3 UVLO 电路实现及仿真

3.1 电源毛刺检测电路设计

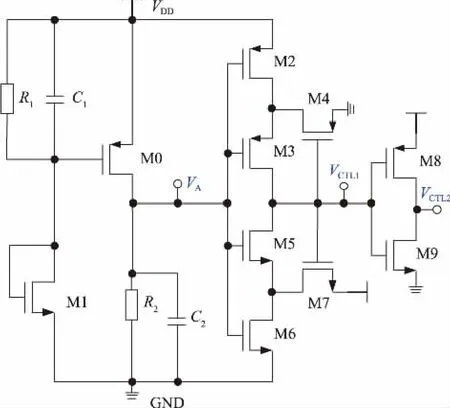

电源毛刺检测电路如图3 所示,电路正常工作时,PMOS 管M0 开启。在内部电源电压VDD存在毛刺波动信号时,并联电阻R1、电容C1两端有一个突变的电压,RC 延时会使M0 管瞬间关闭,这会使并联电阻R2、电容C2的电压VA由于RC 滤波的影响缓慢变低,VA连接施密特触发器的输入端,进而使施密特触发器状态发生反转,再经反相器整形转换为控制信号VCTL1和VCTL2,用于控制比较器电路,从而产生可靠的UVLO 信号。

图3 电源毛刺检测电路

3.2 电源毛刺检测电路仿真

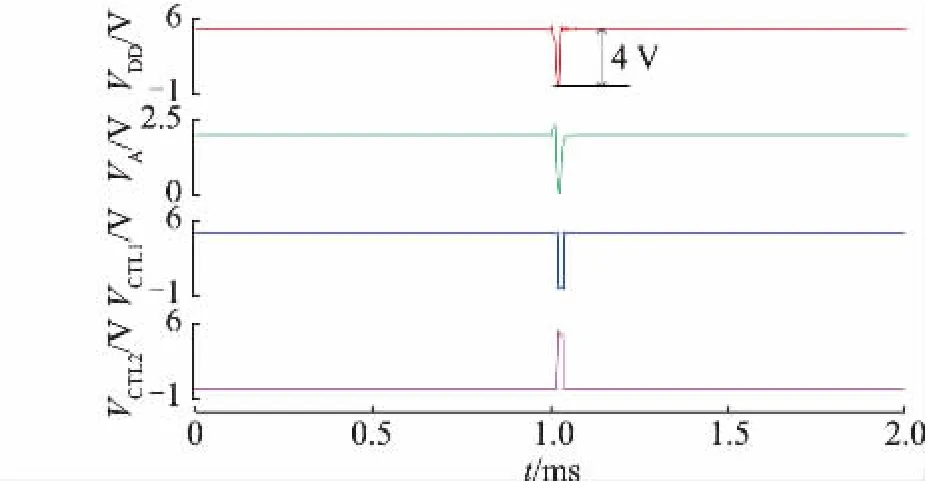

电源毛刺检测电路仿真结果如图4 所示。当VDD存在一个4 V 的毛刺电压时,施密特触发器的输入电压VA检测到这个毛刺信号,从而使VCTL1为低电平,VCTL2为高电平。正常工作时,VCTL1为高电平,VCTL2为低电平。

图4 电源毛刺检测电路仿真结果

3.3 UVLO 电路设计

UVLO 电路使用快速响应的两级差分比较器,提高了处理速度;电压采样电路使用电阻串联的无反馈控制结构,避免了反馈开关噪声造成的不稳定问题;输出整形电路主要滤除噪声,由施密特触发器和反相器组成。UVLO 电路如图5 所示。

图5 UVLO 电路

当VCC达到上限电压VH时,电路开始工作,当低于下限电压VL时,电路停止工作,以防止电压没有达到上限电压时电路启动或低于下限电压时还继续工作。本电路中VREF是比较放大电路的参考电压,VIN1和VIN2是UVLO 电路检测输入电压,Vo为比较放大电路的输出电压,为了防止输出信号受干扰而不稳定,由施密特触发器与反相器组成输出整形电路。UVLO 为低电平时,UVLO 电路开启,电路关断;UVLO 为高电平时,电路正常工作。当VCTL1为高电平、VCTL2为低电平时,比较整形电路正常工作。当VCTL1为低电平时,该电压控制的PMOS 管M20 导通,PMOS 管M22 栅压为高电平,M22 管不导通,同时VCTL2为高电平,该电压控制的NMOS 管M17、M18 导通,NMOS 管M23 栅压为低电平,M23 管不导通。VCTL2为高电平时,NMOS 管M32导通,Vo为低电平,UVLO 为低电平,UVLO 电路开启。

根据图5 可知,电阻分压电路的基本关系式为

很明显,VIN1>VIN2。在VCC从零增大到稳定电压的工作过程中,当VCC比较小,VIN2<VREF时,Vo为低电平,UVLO 电路开启,UVLO 为低电平。在VCC从小增大的过程中,UVLO 由低电平转变为高电平时的临界电压为VH,如果超过这个临界电压,电路正常工作。此时必须使较小的VIN2大于VREF(VIN2>VREF),那么有VIN1>VREF,比较输入差分对管由M11、M12 组成,因此,Vo为高电平,此高电平使PMOS 管M14 不导通。

临界点VCC等于VH,则有

VH为

在VCC从稳定电压减小到零的过程中,在VIN2<VREF<VIN1时,由对管M11、M12 组成的比较差分电路使Vo为高电平,PMOS 管M14 维持不导通。电压VCC从大减小的过程中,UVLO 电路由高电平转变为低电平时的临界电压为VL,如果低于这个临界电压,UVLO 电路开启。此时,必须使较大的VIN1小于VREF(VIN1<VREF),那么由对管M11、M12 组成的比较差分电路使Vo为低电平,PMOS 管M14 导通,比较差分电路由对管M11、M13 组成,由于VIN2<VREF,Vo为低电平,此时UVLO 电路开启,UVLO 为低电平。

临界点VCC等于VL,则有

VL为

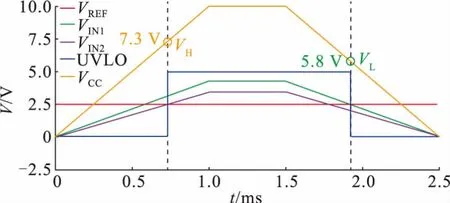

3.4 UVLO 电路仿真

电路设计采用CSMC 0.18 μm BCD 工艺,UVLO电路的仿真结果如图6 所示。VREF=2.5 V,表明VCC从低电压0 V 到高电压10 V 变化时,大约在0.7 ms 以前VIN2<VREF,UVLO 为低电平,即VCC处于欠压状态;随着VCC的不断增大,VIN2在0.7 ms 后大于VREF,此时UVLO 电路由低电平转变为高电平时的VH为7.3 V,UVLO 为高电平,表明VCC处于正常状态。在VCC从稳定高电压10 V 到低电压0 V 变化时,在1.9 ms 以后VIN1<VREF,UVLO 电路由高电平转变为低电平时的VL为5.8 V,UVLO 为低电平,那么VCC处于欠压状态。随着VCC的上升和下降,UVLO 信号存在1.5 V 的迟滞量,可以避免电路反复开启和关闭。

图6 UVLO 电路的仿真结果

4 结论

在分析半桥驱动电路工作原理的基础上,本文设计了应用于GaN 栅驱动的高可靠UVLO 电路,加入电源毛刺检测电路以避免电源噪声影响,采用差分两级比较器电路与电阻分压采样以提高响应速度,避免了反馈回路开关噪声引起的电路不稳定问题,输出整形电路使用施密特触发器和反相器组合防干扰与整形,以滤除噪声的影响,产生高可靠的UVLO 信号。使用CSMC 0.18 μm BCD 工艺完成了电路设计与仿真。仿真结果表明,VCC上升时阈值电压为7.3 V,VCC下降时阈值电压为5.8 V,迟滞量为1.5 V,避免了电路在阈值电压附近反复开启与关断,UVLO 电路功能正确。