张应力调制SOI FinFET器件及其性能

2023-10-20王一杰林鸿霄李梦达徐步青RADAMSON

王一杰,张 静,林鸿霄,李梦达,徐步青,RADAMSON H H,闫 江

(1. 北方工业大学 信息学院,北京 100144;2. 中国科学院 微电子研究所,北京 100029)

在过去的数十年中,集成电路产业在追求低成本、高性能和高集成的过程中不断缩小关键尺寸。然而,CMOS工艺技术中关键尺寸越来越逼近物理极限,因此,人们对新结构和新技术探索的兴趣变得越来越浓厚。近年来,3维全耗尽鳍式场效应晶体管(FinFET)器件结构由于在抑制短沟道效应、缩小器件尺寸、增加集成度方面具有极大的潜力,被视为最有望延续摩尔定律的新结构之一[1]。

易非轻轻推了推门,永南桥上的路灯照亮了她的双眼,那橘黄色的灯光甚至都温暖了她的心。她就那么静静地站着,她想站得笔直,不发出一点儿声音来打扰他们,可她的身子还是忍不住轻轻晃动着。她看着眼前的那张大床,那张简陋的大床,向南和李倩倩就睡在上面。自己的弟弟和未来的侄儿,就睡在上面,自己能说什么呢?易非看见弟弟的拖鞋甩在门口,倒扣着,他能想象出弟弟飞奔过去的样子,她真不忍心打扰他们,她弯腰把拖鞋拾起来,放好,轻轻带上门出来了。

自FinFET器件结构的出现及与之相应的新材料、新工艺的革新,使摩尔定律得以延续。SOI衬底上的FinFET结构不仅能有效抑制小尺寸效应,还能消除Bulk衬底上FinFET器件的闩锁效应,具有短沟道效应小,抗辐射性能好等优点[2]。但随着器件尺寸的不断缩小,SOI FinFET遇到的困难和挑战也越来越多,包括成本、设计、工艺、性能及可靠性等诸多方面的限制,使SOI FinFET很难再满足PPAC(performance,power,area,and cost)的需求[3]。沟道高掺杂带来的库仑散射、栅介质变薄引起的有效电场强度提高和界面散射增强等因素导致的迁移率退化,是限制PPAC的重要原因之一。目前,应变硅技术被认为是解决这一问题的有效方法之一[4-9]。而施加的应力可分为张应力与压应力。已有学者使用TCAD仿真研究了SiN薄膜引入的张应力对FinFET器件性能改进的影响,结果表明,张应力的引入使得器件的漏极电流增加了约60%[10]。也有研究发现,引入压应力后,SiGe沟道堆叠全环绕栅极纳米片pFET的峰值空穴迁移率提升了100%,相应的沟道电阻降低了40%,同时保持了低于70 mV·dec-1的优异亚阈值斜率[11]。应变硅技术通过对器件沟道施加诱生应变增强载流子的迁移率,弥补沟道因高浓度掺杂产生的较强库仑相互作用,同时也可补偿栅介质减薄过程中引起有效电场增强和界面散射增大等因素导致的迁移率退化问题,为摩尔定律的延续带来了新的希望。

本文基于SOI衬底制备了3种栅长的FinFET器件,利用等离子体增强化学气相沉积(plasma enhanced chemical vapor deposition,PECVD)法将50 nm张应力SiN薄膜覆盖在器件表面,将张应力引入到器件Fin沟道中。通过对比引入应变前后SOI FinFET器件的开态电流Ion、关态电流Ioff、电流开关比Ion/Ioff、跨导gm、漏致势垒降低VDIBL和亚阈值摆幅SSS等电学特性,研究了应力对SOI FinFET器件性能的影响。

1 实验与方法

1.1 SOI FinFET的器件制备

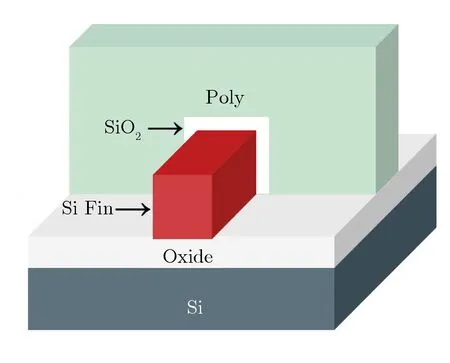

本文所制备的SOI FinFET器件宽长比分别为Weff∶Lg=280 nm∶20 nm,Weff∶Lg=280 nm∶100 nm,Weff∶Lg=280 nm∶500 nm,制备中使用I-Line步进式光刻设备,最小线宽可达到0.35 μm。Fin的形貌、高度、宽度和间距均会对器件的驱动电流等特性产生一定的影响。为避免由于设备问题对Fin宽的限制,本文采用了侧墙转移技术(spacer transfer lithography,STL)来实现Fin的结构[12-13]。SOI FinFET器件的3维立体结构及Fin的透射电子显微镜(transmission electron microscope,TEM)图像如图 1所示。由图1(b)可见,Fin为高度为51.72 nm,上底为21.03 nm,下底为35.62 nm的梯形结构。

1)将药品审评审批、质量标准管理和药品监管(例如:药品注册管理、药品说明书的管理[9]等)有机结合起来,将药品质量标准的发布、修订、勘误等信息及时在国家标准管理部门网站公布,以便相关企业、药检机构和社会公众查询、执行和使用,切实提高质量标准的可及性。

(a) 3D schematic diagram of SOI FinFET device

(b) TEM image of the Fin in SOI FinFET

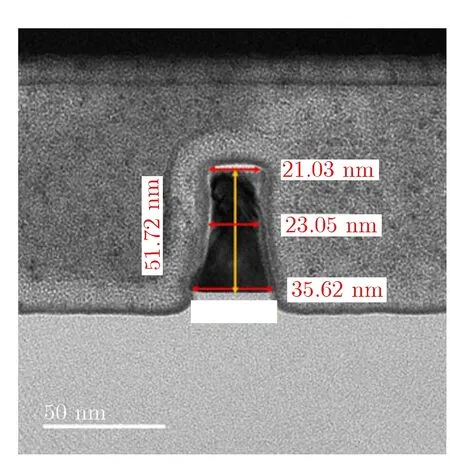

图2 侧墙转移制备Fin的流程图Fig.2 Flow chart of Fin made by Spacer Transfer Lithography

图2为侧墙转移技术制备Fin的流程图。

提前计算年终奖个税,合理避税。各公司在发放年终奖时,建议合理安排好金额,适当注意避开个税税率中的几个“盲区”,计算税后收入,避免出现“企业多给,员工少拿”的尴尬。

(2) 接着利用深紫外光(DUV)光刻机曝光和干法刻蚀形成SiN和a-Si的矩阵图形;

(3) 并通过140℃的H3PO4溶液去除顶部SiN;

(4) 利用PECVD方法生长一层30 nm的SiN,覆盖住a-Si矩形图形;

(5) 接着利用干法刻蚀在a-Si两侧形成SiN侧墙;

(8) 再分别利用H3PO4和HF溶液去除SiN和SiO2,完成Fin的图形化。

(7) 再将SiN侧墙作为硬掩模,进行SiO2和Top-Si的刻蚀,形成立柱结构;

(6) 再使用四甲基氢氧化铵溶液(TMAH)去除SiN侧墙之间的a-Si;

具体的反应方程式可表示为

1.2 PECVD SiN薄膜张应力的引入

在完成SOI FinFET器件的制备后,使用PECVD技术来生长SiN张应力薄膜,将张应力引入到器件沟道中,具体工艺流程为:

对于合并结核病的患者,需密切监测药物不良反应并注意药物间相互作用,必要时调整抗病毒或抗结核药物的剂量,必要时进行血药浓度监测。

(2) 再以一定的速率被释放到反应腔体内;

(3) 在此期间,分子在等离子体中发生撞击和反应;

福克纳是一位思想复杂的作家,他在作品中揭露了美国南方深刻的社会矛盾,谴责奴隶制度的残余势力,同情下层劳动人民的苦难境遇;但也往往充满着对生活失望后的变态心理和精神恐怖症的描写。他还以奥地利心理学家弗洛依德的精神分析学说为依据,采用“意识流”的创作手法,企图通过时序的颠倒、叙述角度的变动和对人物潜在意识活动的推测等来加强作品的艺术效果。这些非现实主义的创作方法对后来的美国文学的发展和演变带来了极大的影响。

(4) 反应产生的SiN产物通过等离子体被运送到器件表面产生吸附;

(5) 吸附在器件表面的SiN会通过扩散运动,形成SiN小岛;

(6) 通过不断反应使小岛增大并聚合产生完整的SiN薄膜;

在完成Fin的图形化后,进行HfO2和Poly-Si的沉积并平坦化。继续沉积硬掩模并对栅极图形进行刻蚀,形成多晶硅假栅。对源漏区进行轻掺杂漏(lightly doped drain,LDD)注入后,沉积并刻蚀形成栅极侧墙结构。再对S/D进行离子注入并激活,沉积绝缘介质层并平坦化,覆盖源漏区域。去除假栅后制作High K金属栅,再制作导电通孔及金属pad,完成SOI FinFET器件的制备。

经过个性化调整,医院把分时段预约进一步精细化,预约时间具体到分钟。同时,医院还为患者提供动态等候讯息,推出“排队等候提醒”服务,患者通过手机即可查询排队情况,等候更加灵活,不再局限于候诊区。

反应过程中,在高频高温(13.5 MHz/550 ℃)条件下,在SOI FinFET器件表面生长了50 nm张应力SiN薄膜,将张应力引入到器件沟道中。

2 结果与讨论

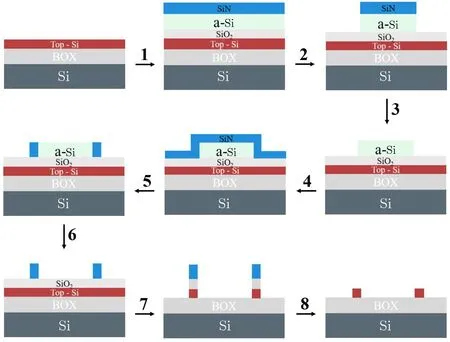

2.1 SOI FinFET器件特性表征

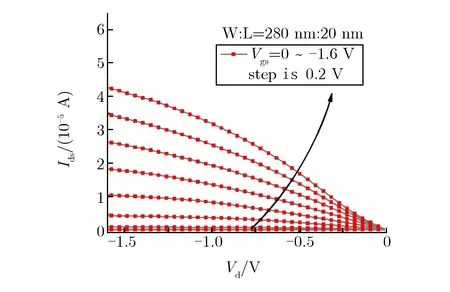

SOI FinFET的基本电学特性采用半导体参数分析仪进行表征,测试包括转移特性曲线和输出特性曲线。图 3为所制备SOI FinFET器件的转移特性曲线和输出特性曲线。由图3可见,漏端电流Ids随着栅极电压Vgs的减小而增大,表明器件呈P型特性。同时,较高的开关比(>106)表明SOI FinFET的栅极对源极/漏极电流具有良好的调节作用。

(a) Transfer characteristics curve

(b) Output characteristics curve

2.2 SOI FinFET应变性能表征

随着2016年我国加入华盛顿成员国,国内高校掀起工程教育国际认证的浪潮。工程教育认证中强调学生的实作技能,鼓励课程设计/毕业设计能出实际作品,鼓励学生以团队合作的形式完成,这是顶石(Capstone)的基本要求。3D打印技术是实现产品从电脑屏幕到实物最为便捷的方式,具有时间和成本优势,从而备受关注和学生喜爱。从专业认证的发展需求看,3D打印技术在高校中的应用将逐步扩大。

导师(通讯作者):邓金祥(1965-),男,教授,博士,主要研究方向为半导体光电薄膜材料与器件. Email:jdeng@bjut.edu.cn

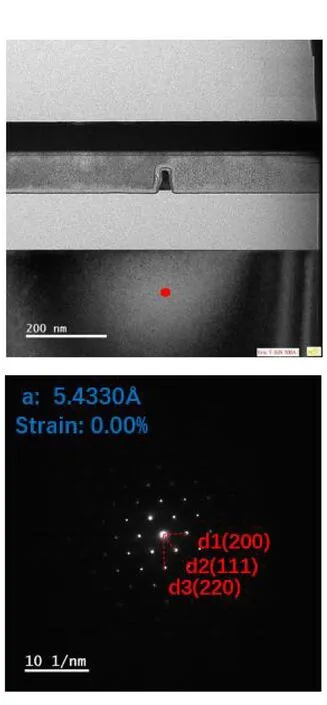

(a) TEM image and SAED pattern of the bottom silicon region of the SOI substrate

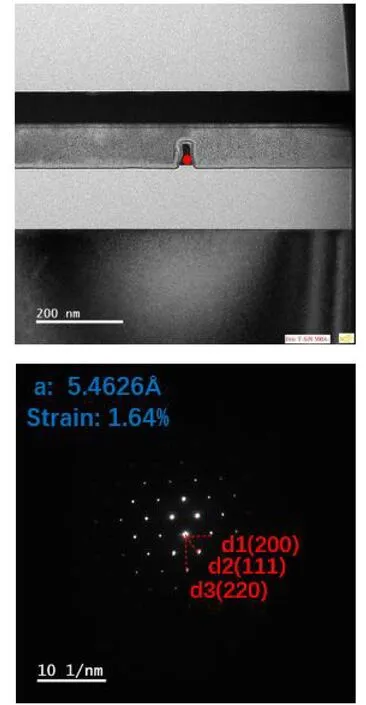

(b) TEM image and SAED pattern of the Fin channel region of the SOI FinFET

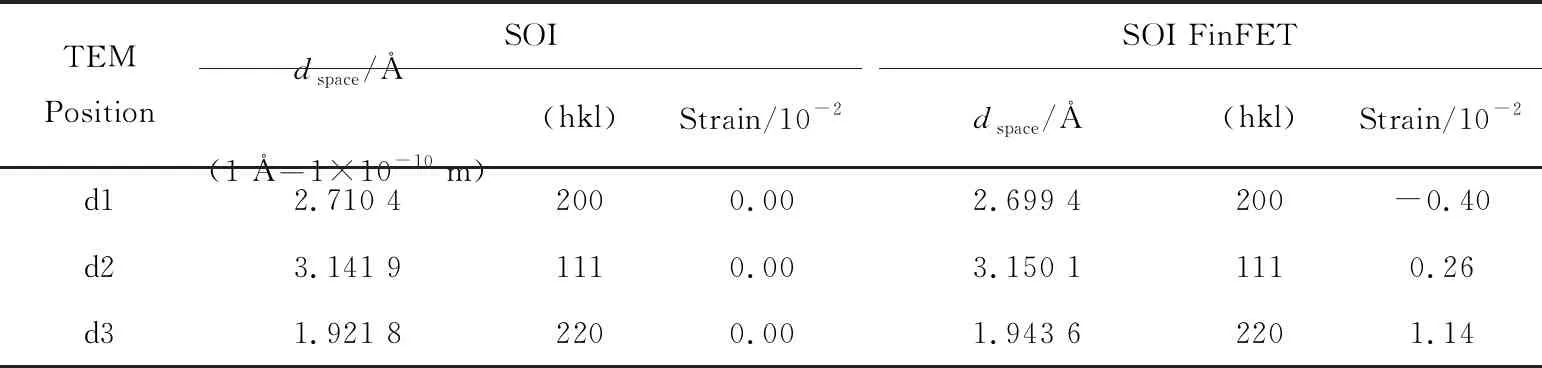

表1 TEM测试选取点的SAED信息对比Tab.1 Comparison of SAED information for TEM test selection points

为表征SiN薄膜覆盖对SOI FinFET沟道内部产生的应变,本文利用TEM进行电子衍射测试(selected-area electron diffraction,SAED),在膜层结构中,选取SOI衬底底部无应力硅来对比SOI FinFET器件硅沟道中的应变情况。引入张应变后SOI FinFET器件的TEM测试结果如图4所示。图4(a)为SOI衬底底部硅的测试点,图4(b)为SOI FinFET器件沟道内部的测试点,将两测试点进行对比计算应力,如表1所列。

(1) 首先硅烷和氨气在机器内部均匀混合;

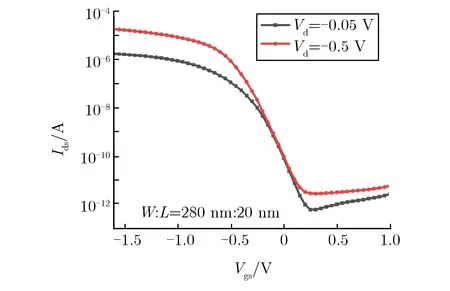

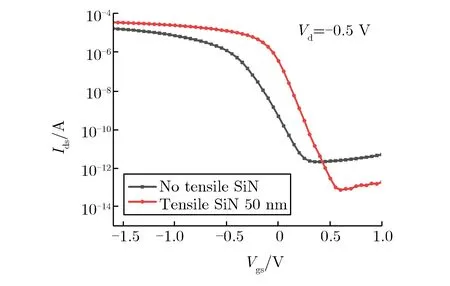

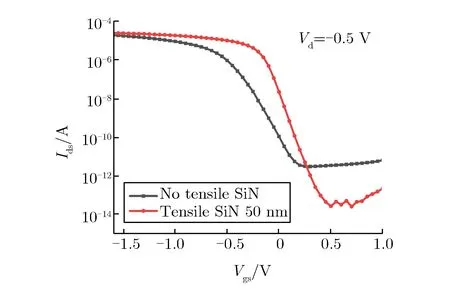

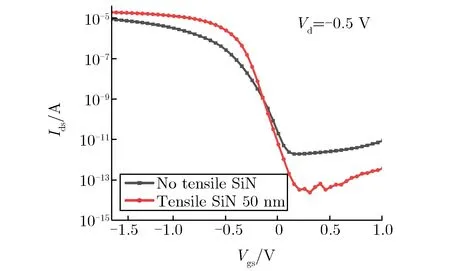

2.3 SOI FinFET应变引入前后的电学特性比较

为探究应变对SOI FinFET器件电学特性的影响,分别测量引入应变后不同栅长SOI FinFET的转移特性曲线,如图5所示。由图5可见,3种尺寸下器件的转移特性曲线均有着一定程度的优化,根据转移特性曲线的对比可见器件的开态电流Ion显著提升,关态电流Ioff显著降低,电流开关比Ion/Ioff显著增大,亚阈值摆幅也有不同程度的优化。

(a) Weff∶Lg =280 nm∶20 nm

(b) Weff∶Lg =280 nm∶100 nm

(c) Weff∶Lg =280 nm∶500 nm

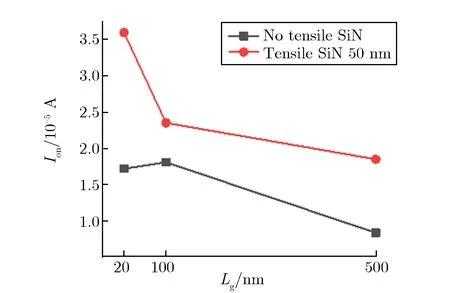

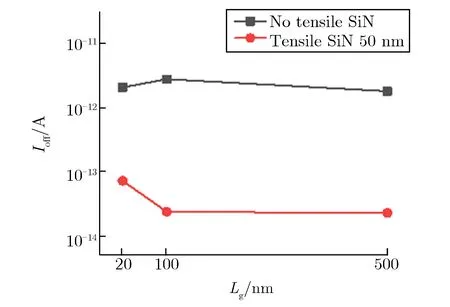

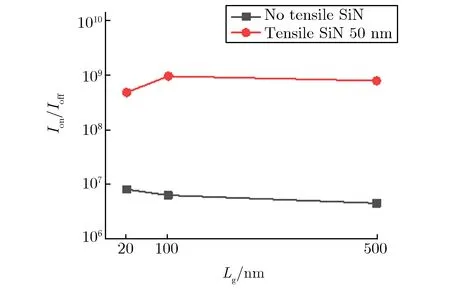

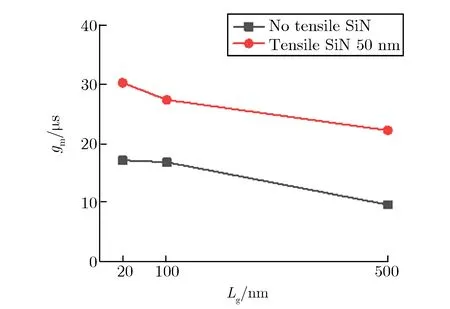

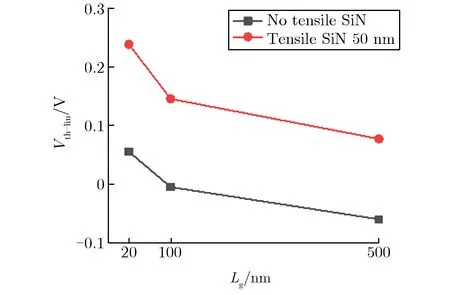

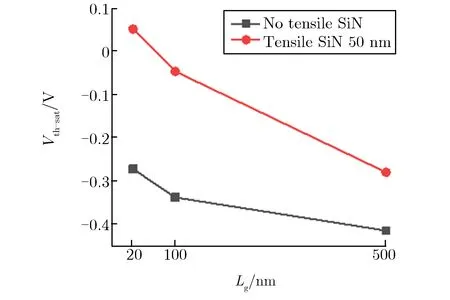

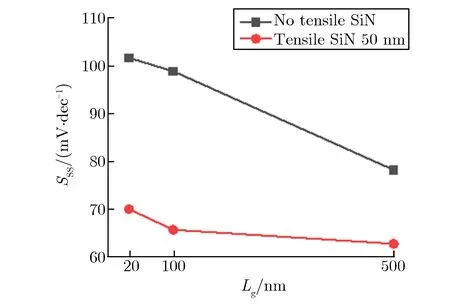

为探讨引入应变前后SOI FinFET器件电学性能的优化,根据应变引入前后的转移特性曲线提取了开态电流Ion、关态电流Ioff、电流开关比Ion/Ioff、跨导gm、线性区阈值电压Vth-lin、饱和区阈值电压Vth-sat、漏致势垒降低VDIBL和亚阈值摆幅SSS等关键电学参数。图6为引入张应力的SOI FinFET的电学参数随栅长的变化关系。其中:开态电流为Vds=-0.5 V,Vgs=-1.6 V时对应的漏端电流;关态电流为漏端电流的最小值;跨导为器件跨导曲线的峰值;Vth-lin与Vth-sat采用固定电流法提取;VDIBL为阈值电压变化与漏极电压变化的比。

(a) Ion

(b) I off

(c) Ion/Ioff

(d) gm

(e) Vth-lin

(f) Vth-sat

(g) VDIBL

(h) SSS

2.3.1 开态电流与跨导

由图6(a)可见,器件的Ion随着栅长的减小而增大。同时,在引入应力后,3个尺寸器件的Ion均有着不同程度的提升,特别是栅长为20 nm时,Ion的提升最为显著。Ion的变化与迁移率μ的变化密切相关,且两者之间的关系可表示为[14]

(1)

其中:Cox为栅极电容密度;Vg,on为开态电流对应的栅极电压。由式(1)可知,图6(a)所示结果与式(1)相符。张应力引入后,3个尺寸器件的Ion都有明显的提升,原因为:(1)张应力的引入显著提高了SOI FinFET器件的沟道载流子迁移率;(2)张应力的引入使SOI FinFET器件的阈值电压向正方向漂移,如图6(e)和图6(f)所示。

迁移率的定义是单位电场内载流子的平均速度,可表示为[15]

(2)

为进一步验证器件迁移率的提升,本文提取了3种尺寸SOI FinFET器件的跨导,如图6(d)所示。跨导与迁移率的关系可表示为[16]

比如,以运满满为例,运满满是一个车货匹配网络平台,这种平台的出现大大提升了车货匹配效率,这是因为这一移动互联网产品是以去中间化设计的,司机端与货主端是运满满网络平台的两大产品,信息部和物流公司通过将货主知己需求发布到平台上,通过平台司机端匹配项有关路线司机用户推动信息和路线,这种运力共享平台的搭建,能够将社会的运力资源充分整合,降低运力成本和消耗,为社会减少了空货车行驶的现象,节省了燃油量,更好地满足了物流的需求双方。

(3)

由式(3)可知,跨导与迁移率正相关,即迁移率增大,跨导升高。由图6(d)可见,器件的跨导随栅长的减小而增大。张应力引入后,3个尺寸器件的跨导都有明显的提升,表明张应力的引入显著提高了SOI FinFET器件的沟道载流子迁移率。

(1) 首先在SOI衬底上依次沉积25 nm的SiO2,100 nm的a-Si和25 nm的SiN;

由图6(e)和图6(f)可见,引入张应力后,器件的阈值电压向正方向发生漂移。阈值电压与Ion的关系如式(1)所示,阈值电压朝正方向发生漂移会使Ion增大。综上所述,引入张应力后,SOI FinFET器件Ion的增大主要是由于迁移率增大和阈值电压的漂移而引起的。

2.3.2 关态电流与电流开关比

余秋雨先生曾经给文化下了一个可谓全世界最简短的定义:“文化,是一种包含精神价值和生活方式的生态共同体。它通过积累和引导,创建集体人格。”剖析余秋雨先生的文化定义,对比“看客文化”,实在为“看客”竟然能够成为一种“文化”而悲哀。

由图6(b)可见,器件的Ioff均有接近两个量级的下降。Ion/Ioff的大小反映了器件对沟道电流的调控能力,Ion/Ioff越大,器件的栅控能力越强,所以在器件制备中会追求更高的Ion/Ioff。由图6(c)可见,与引入张应力前相比,引入张应力后,不同栅长器件Ion/Ioff均有接近两个量级的提升,表明张应力引入后,器件对沟道电流的调控能力得到了显著提升。

2.3.3 漏致势垒降低

(2)二维码支付对手机没有硬件要求,只要是智能手机都支持二维码支付。二维码过闸支付将不断适应城轨客流密度高、快速通行的特征,带回写功能的脱机二维码更符合城轨运营实际需求。二维码支付系统建设一要注重标准化,二要与其它交通行业互联互通。APP专用文件和蓝牙回写技术结合使用,可实现交通部二维码在城轨应用。过闸信息存储在APP专用文件内,闸机通过蓝牙读写专用文件计算票价,解决后台匹配交易、负荷大的缺点。脱机二维码在上海有大规模运营的成熟经验,总体效果平稳可靠。二维码支付体系标准化建设,有利于推动跨行业、跨区域的互联互通。

在小尺寸器件中,漏致势垒降低效应会导致器件的阈值电压随着漏端电压的变化而发生漂移,是反映器件性能的重要指标之一。本文中提取器件VDIBL可表示为[19]

(4)

其中:Vds1与Vds2为给器件加入的不同漏极电压,分别为-0.05 V与-0.5 V;Vth-lin和Vth-sat为器件在2种漏极电压下的阈值电压。由式(4)可知,器件的VDIBL越小,器件的稳定性越高,性能也就越好。由图6(g)可见,张应力的引入使不同栅长器件的VDIBL均有着显著的改善,VDIBL降低的原因是应变在沟道中产生的横向电场阻止了漏致势垒的降低[20-21]。

2.3.4 亚阈值摆幅

亚阈值摆幅Sss是反映器件开启状态与关断状态之间转换速率快慢的性能指标,是亚阈区源漏电流密度变化的一个数量级所需要的栅压增量,Sss越小,代表器件的栅控能力越强,是极其重要的参数,可表示为[19]

(5)

由图6(h)可见,引入张应力后,3种栅长器件的Sss均有显著下降,其中20,100,500 nm 3种栅长器件的Sss分别为69.9,65.6,62.6 mV·dec-1,与引入张应力之前相比,分别降低了31.7,33.2,15.5 mV·dec-1。对比不同栅长器件SSS的变化量,张应力能改善器件的栅控能力。

3 结论

本文基于SOI衬底制备了FinFET,并使用PECVD技术在器件表面淀积了50 nm张应力SiN,将张应力引入器件沟道中,使SOI FinFET器件沟道的载流子迁移率提升,导致Ion得到了明显的提升。此外,还观察到器件的Ioff,Ion/Ioff,gm,VDIBL和SSS等多个电学参数都有着不同程度的优化。值得一提的是,应变对栅长较小器件的Ion和SSS有更明显的改善。

浏览这五道题,我们便可知道这是一个关于旅行的故事。因为第一题暗示了因为某种缘故,要去某个地方;第二题暗示了主人公去某个地方的目的;第三题暗示了出行方式;第四题则暗示了主人公对某种旅行的看法。第五题暗示了旅行的出行时间。