集成电路的闩锁测试

2023-09-06赵俊萍孙健

赵俊萍,孙健

(北京微电子技术研究所,北京 100076)

引言

随着集成电路制造技术的发展,CMOS 电路由于具有高集成度、低功耗、工艺成熟等优点而成为了大规模集成电路制造中的主流,而CMOS 的闩锁效应(Latchup)是CMOS 集成电路在产品可靠性上可能发生的特有现象:当集成电路受到外界的信号干扰时,寄生在电路中的NPN 和PNP 结构会被触发而形成低阻通路,从而在电路的电源和地之间产生大电流,并且由于正反馈的存在而形成闩锁导致电路无法正常工作,甚至烧毁芯片,严重影响电路的可靠性。据统计,CMOS 集成电路由于闩锁效应而引发的失效占失效总数的三分之一以上。[4]所以在军用集成电路检验中,用户极为关注电路的抗闩锁能力。以CMOS、HV-CMOS 和Bi-CMOS 等工艺为基础的产品,几乎都有进行闩锁测试的要求。

1 集成电路闩锁测试标准

目前,国外集成电路闩锁测试标准主要就是JEDEC(Joint Electron Device Engineering Council,电子器件工程联合委员会)协会的标准。该协会于1989年发布实施了JESD17 《CMOS IC Latch-up Test 》,之后在1997年发布了JESD78《IC Latch-up Test》。1999年JEDEC 发布公告JESD17 被JESD78 代替而废止。2006年JESD 发布实施了JESD78A 版,2011年发布实施了JESD78D 版。目前能查到的最新版本是JESD78E 版。国内集成电路闩锁的测试标准主要有两个,一个是SJ 20954《集成电路锁定试验》,是2006年由信息产业部发布的一个电子行业军用标准。另外一个是GJB 9389《集成电路锁定试验方法》,是2018年由中央军委装备发展部颁布的国家军用标准。SJ 20954 和GJB 9389 两个测试标准中的测试流程及测试方法等内容,基本与JESD78 中规定的相同。在2021年公布的GJB 548C 中,也加入了闩锁测试的内容,方法3023 集成电路锁定试验中规定的测试方法,同GJB 9389。

2 集成电路闩锁测试流程

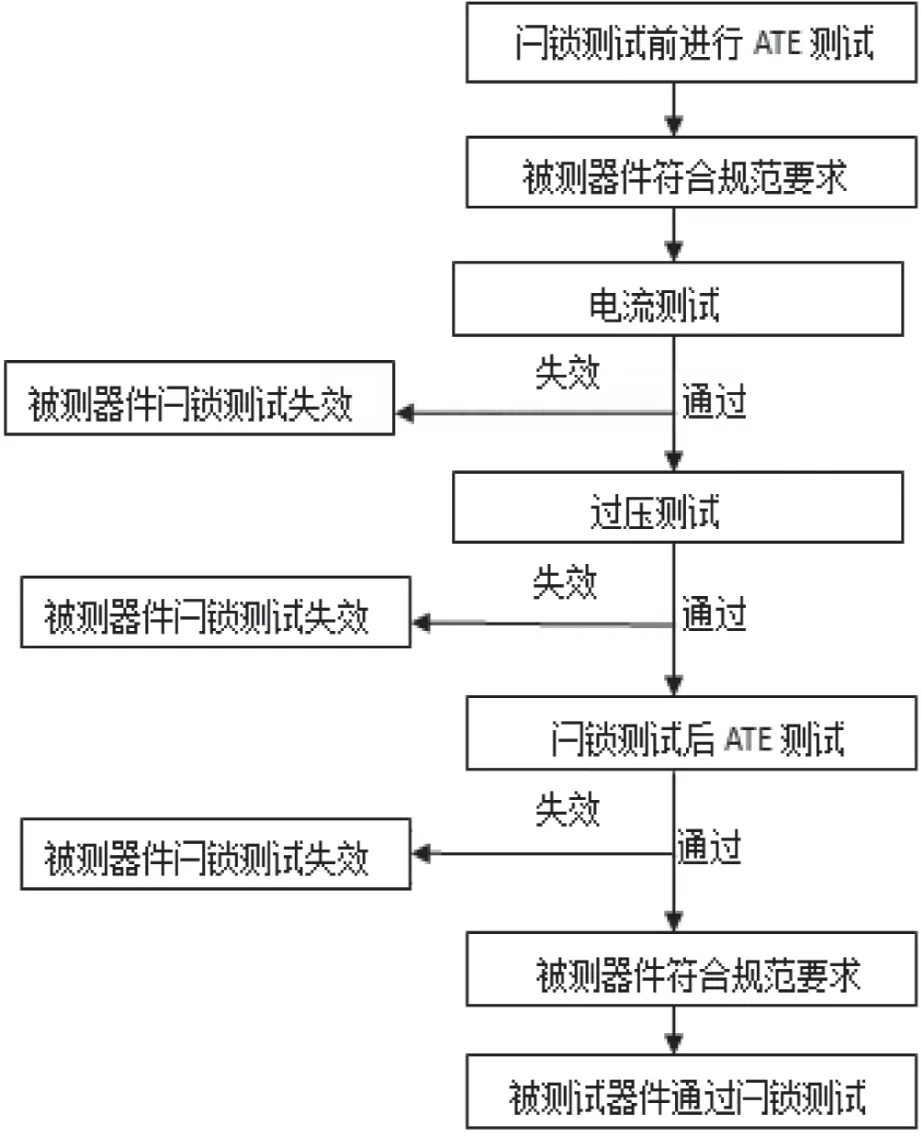

以JESD78E 为例,典型的闩锁测试流程如图1 所示。闩锁测试分为电流测试和过压测试。电流测试是对输入、输出及可配置的I/O 引脚进行的,又分为正电流测试和负电流测试。电流测试实际模拟的情况是浪涌电压出现在非电源管脚(输入、输出及输入/输出),浪涌电压超出电源电压与地之间的范围,在该管脚连接电路中产生电流,当电流足够大,触发寄生NPN 和PNP,导致闩锁。过压测试是对电源引脚进行测试。过压测试模拟的实际情况是当芯片开始通电时、芯片正常工作时或者发生ESD 静电放电时,出现浪涌电压在电源管脚导致NW和PW 之间的PN 结雪崩击穿、从NW 到PW 的n+有源区穿通、从P 型衬底到NW 的p+有源区的穿通和漏极雪崩击穿等,从而形成击穿电流,当电流足够大,触发寄生NPN 和PNP,导致闩锁。[1]在电流测试和过压测试时,被测器件施加的条件、失效判断、施加的电流和电压波形的时序要求在测试标准中都有规定。在测试过程中,要求至少对同一制程下的三只电路进行电流测试和过压测试,也允许采用新的样品分组进行电流测试和过压测试。

图1 典型闩锁测试流程

3 集成电路闩锁测试时特殊管脚的处理方法

集成电路闩锁测试的详细步骤,在相关标准及很多文献中都有描述,本文就不再赘述。对于复杂的CMOS集成电路,通常包含许多特殊性质的管脚。这些特殊性质的管脚,在实际闩锁测试过程中,需要进行特殊处理。在实际测试过程中,一些特殊引脚的处理方法如下:

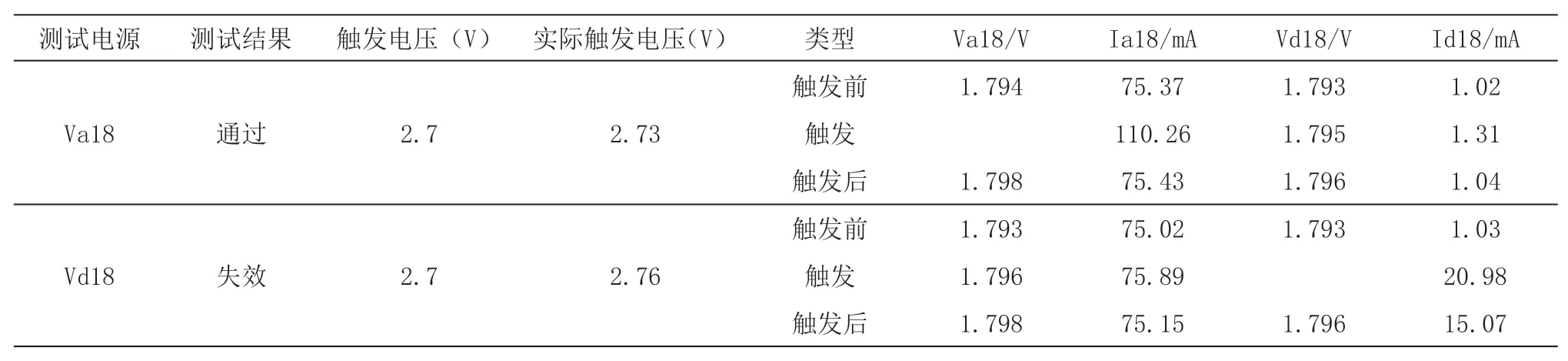

1)对于有多组电源的集成电路,在对电源进行过压测试时,电压相同的电源引脚可以合并成一个电源组,该电源组的钳位电流根据总的标称电流来设定。例如电路中有Va18 和Vd18,这两组电源的工作电压都为1.8 V,标称电流分别为Ia18 和Id18,过压测试时可将它们合并成一组进行测试,合并后的电源组的钳位电流I1.8=100mA+Ia18+Id18 或1.5(Ia18+Id18), 取电流较大者。如果Va18 和Vd18 的标称电流Ia18 和Id18相差较多时,则不推荐将两组电源进行合并后测试。如表1 为将Va18 和Vd18 两组1.8 V 的电源分开进行过压测试时的测试结果。从测试结果中可以看出,当单独对Vd18 进行触发时,Vd18 的电源电流从触发前1.03 mA 增大到触发后的15.07 mA,闩锁效应被触发,按照闩锁判断标准,Vd18 闩锁过压测试不合格。但如果将Va18 和Vd18 两组1.8 V 电源合并后进行闩锁测试的话,有可能无法检查到Vd18 电源发生闩锁时电流发生的变化,造成漏判。

表1 相同电压的电源分组进行过压测试结果

2)对于数字差分输入管脚来说,在实际工作中,正负两个差分输入通常是一个接高电平,一个接低电平,一般不同时为高电平或者低电平。在闩锁测试时,如果把差分管脚按照普通输入对待,当它们同时为高电平或者低电平,电路的状态不稳定,可能会出现较大的电源电流,造成误判。如表2 中的闩锁数据为某包含差分输入端口的电路中两个输出管脚电流测试的结果。由于该电路中的一对差分输入,在同时置高的状态下,BI 输出端在进行电流测试时,电源电流从触发前的1.13 mA 增大到触发后的50.31 mA,按照标准,该输出端闩锁测试失效。但该电源电流的增大,不一定是发生了闩锁导致,有可能是因为电路状态不稳定导致。所以在闩锁测试时,不能同时将正负两个差分输入端置于高电平或者低电平。处理的方法为:当所有输入置于高电平时,将正输入置于高电平,而负输入置低电平;当所有输入置于低电平时,将正输入置于低电平,而负输入置于高电平。这样电路的状态稳定,不会出现电源电流忽然变大的现象。按照这两中处理方法对上述电路重新进行闩锁试验,未出现大电流的情况,闩锁测试合格。

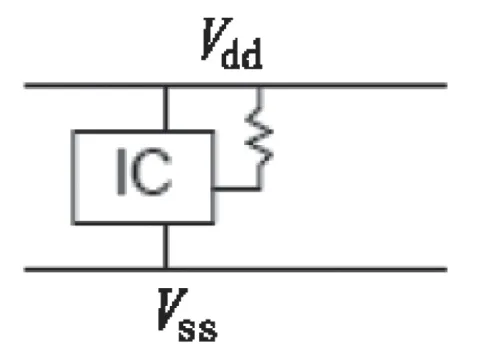

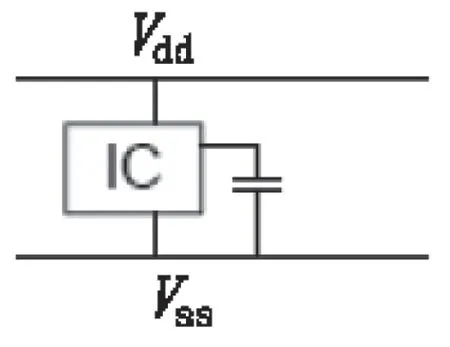

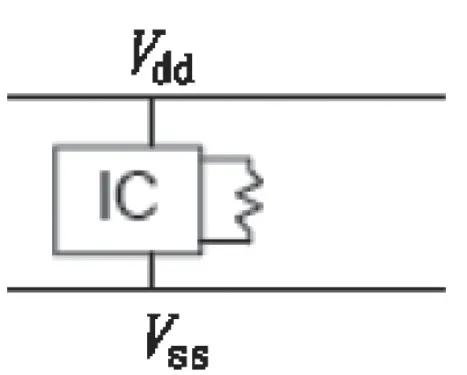

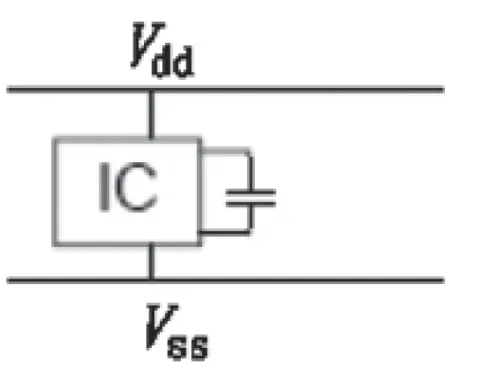

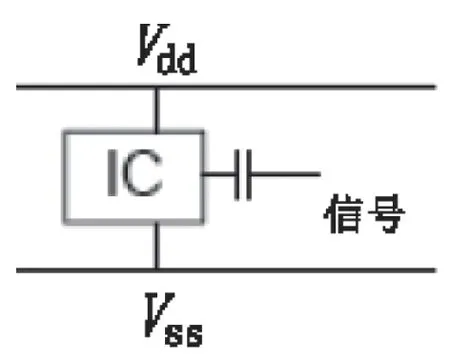

3)并不是所有管脚都需要执行相同的测试标准,要分析电路的实际情况,根据电路的实际情况进行相应的测试。例如在复杂集成电路中,有些管脚,例如通过无源元件(电阻、电容)与电源或者地直接相连的管脚,如图2~5 所示,这些管脚电位固定,触发闩锁的可能性非常小,通常不需要进行闩锁测试;通过无源元件(电阻、电容)相连接的两个管脚,如图6、图7 所示,通常不会有其它浪涌信号出现在这两个管脚之间,所以触发闩锁的可能性较小,也不需要进行闩锁测试。有些管脚,存在串联电阻,如图8 所示,在进行闩锁测试时,需要依据加载在该管脚的电压值除以电阻值计算出注入的触发电流。如果管脚串联电容,如图9 所示。闩锁测试时可不带电容进行测试,但是需要通过假设信号端在最坏情况下的电压瞬变值,来计算出触发电流的值[2]。

图3 某管脚通过电阻接电源

图4 某管脚通过电容接地

图5 某管脚通过电容接电源

图6 两管脚通过电阻相连接

图7 两管脚通过电容相连接

图8 管脚存在电容

图9 管脚存在电阻

4)对于可配置的I/O 引脚,若测试时无法判断其是输入还是输出,可当作输出处理。如能判断其输入输出属性,根据其实时属性参与接高或者接低进行闩锁测试。

5)集成电路中的NC 引脚、接地引脚以及与时间相关的引脚不需要进行测试。

6)电路中有些管脚是按电源类的规则命名的,而实际上它们并不是电源管脚,属于非电源类管脚,例如Vref,在进行闩锁测试时,按输入处理,进行电流测试。

4 集成电路闩锁测试过程中的注意事项

为了保证闩锁测试的有效性,在闩锁测试过程中需要注意以下两个方面:

1)在测试过程中,要关注被测电路测试数据中电源电流的值。正常情况下,测试过程中电路的标称电流Ionm 值较小且具有重复再现性。如果测试到的电源电流标称值太大或者不稳定,说明有输入管脚的状态没有设置正确。此时,要检查一些特殊管脚,如时钟、使能、差分等端口是否在合适的工作状态。

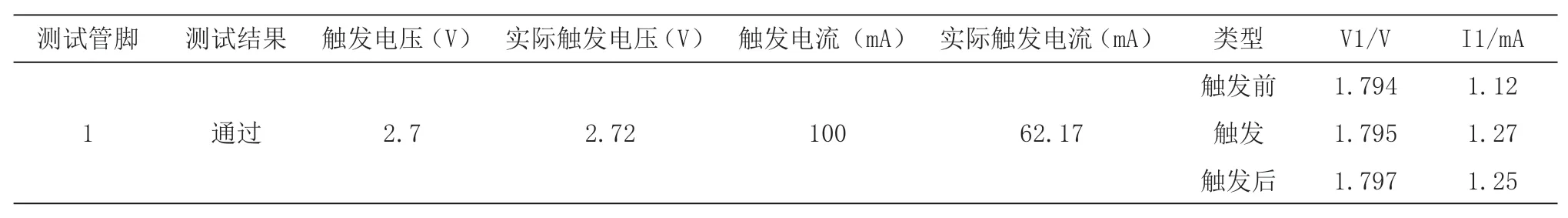

2)在闩锁测试过程中,需要关注电流测试数据中实际触发电流和过压测试中实际触发电压的值。在实际测试中,由于钳位电流和钳位电压的限制,使得实际触发电流和实际触发电压达不到设定的值。如表3 中所示的某输入管脚的电流测试结果。该输入管脚的触发电流为100 mA,输入管脚的钳位电压=1.5V1=1.5*1.8=2.7 V。而实际触发时触发电流只达到62.17 mA,由于实际触发电压达到了测试管脚的钳位电压2.7 V,所以触发电流不能再增大。这种情况虽然没有违反失效判据,且闩锁测试后电路ATE 测试无异常,理论上可以判该管脚能通过100 mA 的电流测试,但实际上100 mA 的电流测试是无效的,有效电流为62.17 mA。如果将输入管脚的钳位电压增大,测试过程中会导致该管脚端口发生烧蚀,电路失效,但电路的失效不是由于闩锁造成的,而是电路管脚端口引入了大于管脚端口能承受的最大电流导致。这种情况,测试过程中按标准要求设置好钳位电压和电流,并在测试结果中记录实际触发电流和电压,让委托方知悉测试情况。

表3 钳位电压限制时输入管脚电流测试结果

5 结论

为了能够很好地表征出集成电路的抗闩锁能力,在集成电路闩锁测试过程中,正确理解和执行集成电路的闩锁测试标准尤为重要。但有些集成电路的结构和功能较为复杂,它包含有相当数量的特殊性质的管脚。正确处理这些特殊性质管脚的方法,对准确评估集成电路的抗闩锁能力也十分关键。此外,通过闩锁测试数据,能够发现并解决测试过程中存在的问题,也是闩锁测试中的难点。