一种基于FPGA的高速并行传输系统设计

2023-06-21毕涛刘迪张大为葛宝川

毕涛 刘迪 张大为 葛宝川

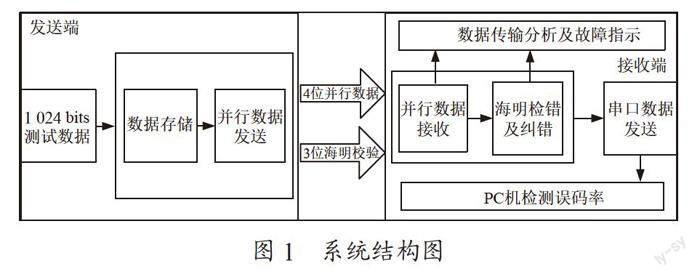

摘 要:该系统使用FPGA芯片完成了高速并行传输系统设计,其由并行数据发送端、并行数据信道、并行数据接收端和数据分析显示装置四部分构成。并行数据发送端实现海明编码和数据格式转变的功能;并行数据信道由7根同轴电缆及相应电路组成;接收端进行故障检测、数据同步提取、抽样判决和校验纠错。在传输过程中实时监测数据状态,最后通过RS232串口发送给PC机用于检测误码率。系统创新地使用了“多采样点判决算法”,降低了传输过程中的误码率。

关键词:现场可编门阵列;并行数据传输;误码率;海明码;串行通信

中图分类号:TP274+.2 文献标识码:A 文章编号:2096-4706(2023)01-0058-04

Design of a High-Speed Parallel Transmission System Based on FPGA

BI Tao, LIU Di, ZHANG Dawei, GE Baochuan

(School of Basic Science for Aviation, Naval Aviation University, Yantai 264001, China)

Abstract: This system uses FPGA chip to complete the design of high-speed parallel transmission system. The system consists of four parts: parallel data sending end, parallel data channel, parallel data receiving end and data analysis and display device. The parallel data sending end realizes the functions of Hamming coding and data format transformation. The parallel data channel is composed of 7 coaxial cables and corresponding circuits. The receiving end performs fault detection, data synchronous extraction, sampling decision and check and error correction. In the transmission process, the data status is monitored in real time, and finally sent to the PC through RS232 serial port for detecting the bit error rate. The system innovatively uses the “multi sampling point decision algorithm” to reduce the bit error rate in the transmission process.

Keywords: FPGA; parallel data transmission; bit error rate; Hamming code; serial communication

0 引 言

隨着数字式设备的大量使用,设备之间的数据传输、控制、接收和处理显得尤为重要。传统的数据传输系统速率低,在传输过程中不能校验编码是否正确,已经不能适应数据传输业务的发展。设计一套高速并行的数据传输系统,实现数据高速的可靠传输,并且能够在传输工程中实现检错和纠错。该系统具有传输速度高、传输数据误码率低的特点。

1 系统结构

本系统能够满足以下指标:

数据实现并行传输的数据位大于4 bit;数据传输的线缆长度大于50 cm,传输速率大于20 Mbps;误码率低于1/1 000;可传输任意1 024 bit数据接收端,接收端配RS232接口,波特率9 600,以便用计算机检测误码率;在传输过程中当一根导线断路、两根导线短接或导线持续高低电平时,接收器能检错报警,且能够实现数据纠错等功能。

并行数据发送端和接收端均使用硬件描述语言在FPGA芯片中构建可编程逻辑实现。发送端进行海明编码和数据格式转变;传输信道由7根同轴电缆组成;接收端进行故障检测、数据同步提取、抽样判决和校验纠错;在传输过程中通过显示装置实时监测数据状态;最后通过RS232串口发送给PC机检测误码率。系统结构如图1所示。

2 系统方案设计

2.1 主控模块

STC系列单片机资源丰富,但在速度和精度上难以满足要求。高速并行数据传输逻辑可通过FPGA实现,时序上控制严格,有较高的速度和精度,能够很好地完成设计指标要求。

2.2 RS232通信电路

串口通信芯片选用TI公司的MAX3232,能实现FPGA端口电压和PC机串口电压的转换,转换速率高达250 KB/s,符合设计要求。

2.3 传输线的论证与选择

高速数字信号对导线有严格的要求,信号在普通导线中反射和失真严重,普通导线不能满足该信道的要求,所以选用同轴电缆。同轴电缆的抗干扰能力强、屏蔽性能好、传输数据稳定、信号衰减小、传输速度高。

2.4 校验码的论证与选择

奇偶校验码只能检测出奇数位出错,而且奇偶校验码无法检测出哪位出错,接收端不仅具有报警检错功能,还要具有数据纠错功能,所以奇偶校验码不满足设计的要求。海明码是一种多重奇偶校验检错系统,它通过在数据位之间插入k个校验位,从而实现检错并且能够确定一位错误数据的位置,符合设计的要求。

3 系统理论分析与计算

3.1 信号基带传输原理

M信号基带传输系统是指不经过载波调制而直接传输二进制数字信号的系统,基带传输系统适用于近距离通信,该设计要求发送端和接收端使用50 cm的电缆进行通信,比较适合直接使用基带进行数据传输,属于基带传输系统。下面对高速并行传输系统中的两个概念进行分析和说明。

3.1.1 误码率分析

主要从信道噪声、码间干扰、传输线带宽限制三个方面进行分析:

(1)信道噪声。基带传输系统中信道加性噪声通常被视为均值为0、平均功率为 ,噪声瞬时值V服从高斯分布为:

(1)

噪声的引入会使得信号波形发生畸变,门限判决失误,导致误码产生。结合题目要求,我们应该使用合适的滤波器将频带外的噪声滤除,同时采用多点抽样判决的方法将噪声的干扰降到最低。

(2)码间干扰。由于基带信号受信道传输时延的影响,信号波形将被延迟从而扩展到下一码元,形成码间干扰,造成系统误码。二进制单极性基带传输系统误码率公式为:

(2)

结合设计要求,使用的滤波器参数设置尽量考虑产生码间干扰的情况,从而提高并行数据传输速率。

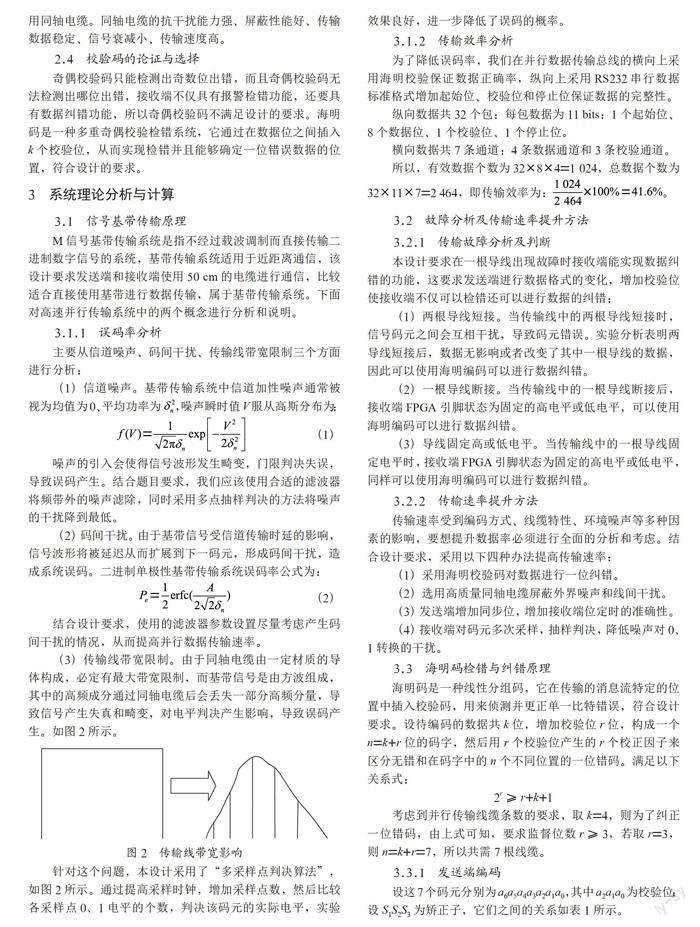

(3)传输线带宽限制。由于同轴电缆由一定材质的导体构成,必定有最大带宽限制,而基带信号是由方波组成,其中的高频成分通过同轴电缆后会丢失一部分高频分量,导致信号产生失真和畸变,对电平判决产生影响,导致误码产生。如图2所示。

针对这个问题,本设计采用了“多采样点判决算法”,如图2所示。通过提高采样时钟,增加采样点数,然后比较各采样点0、1电平的个数,判决该码元的实际电平,实验效果良好,进一步降低了误码的概率。

3.1.2 传输效率分析

为了降低误码率,我们在并行数据传输总线的横向上采用海明校验保证数据正确率,纵向上采用RS232串行数据标准格式增加起始位、校验位和停止位保证数据的完整性。

纵向数据共32个包:每包数据为11 bits:1个起始位、8个数据位、1个校验位、1个停止位。

横向数据共7条通道:4条数据通道和3条校验通道。

所以,有效数据个数为32×8×4=1 024,总数据个数为32×11×7=2 464,即传输效率为:。

3.2 故障分析及传输速率提升方法

3.2.1 传输故障分析及判断

本设计要求在一根导线出现故障时接收端能实现数据纠错的功能,这要求发送端进行数据格式的变化,增加校验位使接收端不仅可以检错还可以进行数据的纠错:

(1)两根导线短接。当传输线中的两根导线短接时,信号码元之間会互相干扰,导致码元错误。实验分析表明两导线短接后,数据无影响或者改变了其中一根导线的数据,因此可以使用海明编码可以进行数据纠错。

(2)一根导线断接。当传输线中的一根导线断接后,接收端FPGA引脚状态为固定的高电平或低电平,可以使用海明编码可以进行数据纠错。

(3)导线固定高或低电平。当传输线中的一根导线固定电平时,接收端FPGA引脚状态为固定的高电平或低电平,同样可以使用海明编码可以进行数据纠错。

3.2.2 传输速率提升方法

传输速率受到编码方式、线缆特性、环境噪声等多种因素的影响,要想提升数据率必须进行全面的分析和考虑。结合设计要求,采用以下四种办法提高传输速率:

(1)采用海明校验码对数据进行一位纠错。

(2)选用高质量同轴电缆屏蔽外界噪声和线间干扰。

(3)发送端增加同步位,增加接收端位定时的准确性。

(4)接收端对码元多次采样,抽样判决,降低噪声对0、1转换的干扰。

3.3 海明码检错与纠错原理

海明码是一种线性分组码,它在传输的消息流特定的位置中插入校验码,用来侦测并更正单一比特错误,符合设计要求。设待编码的数据共k位,增加校验位r位,构成一个n=k+r位的码字,然后用r个校验位产生的r个校正因子来区分无错和在码字中的n个不同位置的一位错码。满足以下关系式:

2r≥r+k+1

考虑到并行传输线缆条数的要求,取k=4,则为了纠正一位错码,由上式可知,要求监督位数r≥3,若取r=3,则n=k+r=7,所以共需7根线缆。

3.3.1 发送端编码

设这7个码元分别为a6a5a4a3a2a1a0,其中a2a1a0为校验位;设S1S2S3为矫正子,它们之间的关系如表1所示。

由表格1可见:矫正子S1为1时,错码位置在a2、a4、a5、a6,所以可得出矫正子和错码位置的关系:

S1=a6⊕a5⊕a4⊕a2

S2=a6⊕a5⊕a3⊕a1 (4)

S3=a6⊕a4⊕a3⊕a0

若要求校验位可以对数据位进行检错和纠错,则S1=S2=S3=S0,解得:

(5)

所以发送端编码时校验位的计算方法如式(5)所示。

3.3.2 接收端解码

接收端收到每个码组后,按照式(4)计算出S1、S2和S3,再按照表格2就可以判定错码情况;若有错码,则对错码进行取反即可得到原始正确的数据。

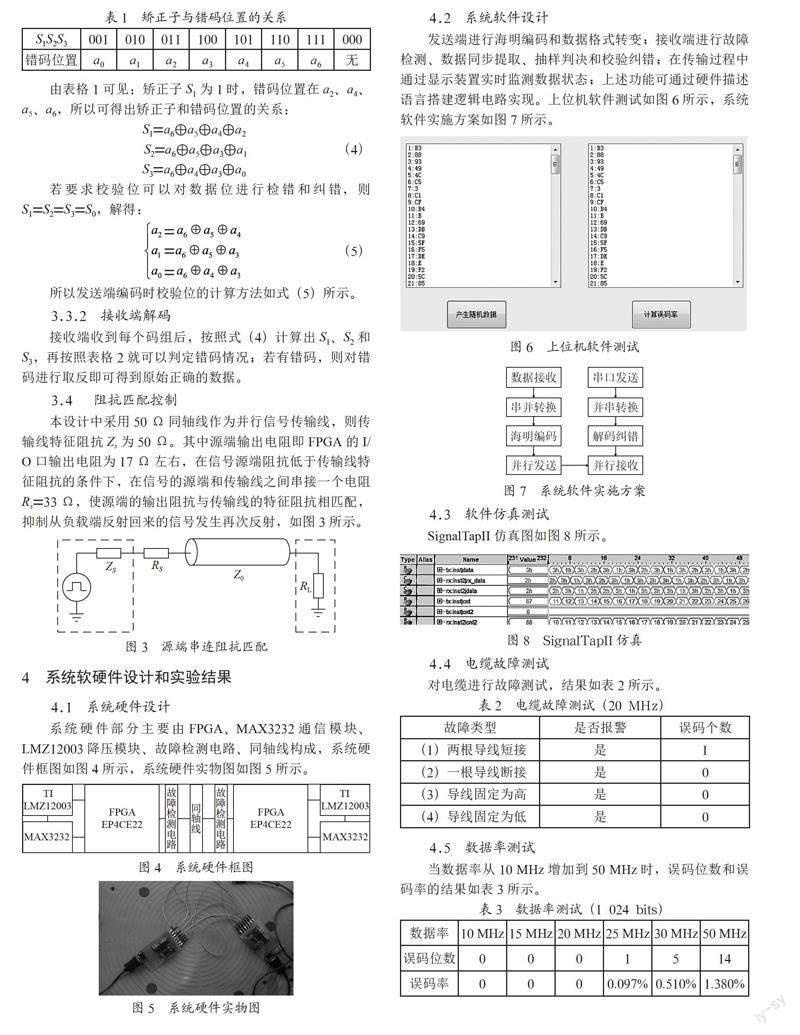

3.4 阻抗匹配控制

本设计中采用50 Ω同轴线作为并行信号传输线,则传输线特征阻抗Zs为50 Ω。其中源端输出电阻即FPGA的I/O口输出电阻为17 Ω左右,在信号源端阻抗低于传输线特征阻抗的条件下,在信号的源端和传输线之间串接一个电阻Rs=33 Ω,使源端的输出阻抗与传输线的特征阻抗相匹配,抑制从负载端反射回来的信号发生再次反射,如图3所示。

4 系统软硬件设计和实验结果

4.1 系统硬件设计

系统硬件部分主要由FPGA、MAX3232通信模块、LMZ12003降压模块、故障检测电路、同轴线构成,系统硬件框图如图4所示,系统硬件实物图如图5所示。

4.2 系统软件设计

发送端进行海明编码和数据格式转变;接收端进行故障检测、数据同步提取、抽样判决和校验纠错;在传输过程中通过显示装置实时监测数据状态;上述功能可通过硬件描述语言搭建逻辑电路实现。上位机软件测试如图6所示,系统软件实施方案如图7所示。

4.3 软件仿真测试

SignalTapII仿真图如图8所示。

4.4 电缆故障测试

对电缆进行故障测试,结果如表2所示。

4.5 数据率测试

当数据率从10 MHz增加到50 MHz时,误码位数和误码率的结果如表3所示。

5 结 论

本设计硬件电路采用两块FPGA开发板及其外围电路,实现了高速并行数据传输系统。重点在于软件的设计,实现数据传输的稳定可靠,具有传输效率高、传输距离长、误码率低等特点。当线缆出现故障能够自行报警,接收端能够实现数据纠错功能。扩展了传输监测的软件显示,自行分析传输过程中的误码率,具有一定的实际应用价值。

参考文献:

[1] 王平,张新东.基于智能仪表的数据采集系统设计 [J].自动化与仪表,2009,24(4):9-10+18.

[2] 王金庭,杨敏,田浩,等.基于FPGA的函数发生器 [J].电子测量技术,2010,33(4):32-34.

[3] 杜里,张其善.电子装备自动测试系统发展综述 [J].计算机测量与控制,2009(6):1019-1021.

[4] 王刚,乔纯捷,王跃科.基于时钟同步的分布式实时系统监控 [J].电子测量与仪器学报,2010,24(3):274-278.

[5] 李惠,徐小川,于学伟,等.基于STM32的智能发电机电参量测量装置的设计 [J].电测与仪表,2016,53(2):125-128.

[6] 张磊,康家方,赵志勇,等.基于PSWF的非正弦通信系统的同步的方法 [J].无线电通信技术,2011,37(4):7-9.

[7] 种兰祥,朱春香,游涛.数字存储示波器的计算机控制与同步测量 [J].电子测量技术,2008,31(10):73-75+96.

[8] 邹建,林强,王二锋.基于FPGA的波形发生器设计 [J].电子测量技术,2012,35(7):47-50.

[9] 朱军,高清维,韩璐.基于DSP和FPGA的数据通信实现方案 [J].电子测量技术,2009,31(1):102-104+119.

[10] 孟庆生,徐中干.基于无线传感器网络的电参数测量系统设计 [J].数字技术与应用,2019,37(1):195-196+198.

[11] 陆翔,刘邦经.基于STM32的嵌入式综合实验开发平台研究 [J].实验室研究与探索,2017,36(10):57-60.

[12] 唐亚平.基于FPGA与DSP的等精度数字频率计设计 [J].微计算机信息,2007(2):249-250+91.

[13] 楊旭.传感器技术在机电技术中的应用 [J].当代化工研究,2020(22):73-74.

[14] 邢兰昌,祁雨,刘昌岭,等.电-声-热多参数联合测试系统开发 [J].实验技术与管理,2017,34(11):78-85.

作者简介:毕涛(1986—),男,汉族,山东烟台人,讲师,硕士研究生,研究方向:控制工程。收稿日期:2022-09-02