精密测距器专用检测设备设计与验证

2023-06-16谢洪森刘云飞黄子革张建明

谢洪森,王 鼎,刘云飞,黄子革,张建明

(1.海军航空大学青岛校区,山东 青岛 266041;2.中国电子科技集团公司第二十研究所,陕西 西安 710068)

0 引 言

现代航空飞行器飞行空域大、速度快,对航空导航引导性能提出了更高要求,尤其是飞机着陆飞行过程中对导航引导精度要求更高。精密测距器主要是用于机场或航路,保障飞机精准测定相对固定标志点的距离信息,确保飞行员据此信息操纵飞机并及时调整控制飞机空中飞行或下降着陆姿态[1]。当前,导航测距系统安装位置周边地理地质环境条件等复杂多变,加上空中各类电磁信号经常会干扰系统测距性能,为此对导航测距系统开展常态化和定期主要性能检测校验是非常必要的。目前,国内尚无针对精密测距器专用的检测设备[2]。传统的检测校验方法是依托专用导航校验飞机对测距系统实施的专项飞行,但飞行计划复杂、检验周期长,受空域飞行条件限制等多种因素制约,无法满足高效率、大批次飞行保障任务的精密测距系统快速检测校验需求。

本文所设计的精密测距器专用检测设备采用FPGA、DSP 和ARM 技术为主体的设计架构[3],综合运用嵌入式微处理器显示控制、询问与应答信号调制解调、测距精度标校、PFE 与CMN 精度分析、天线方向图仿真等技术方法,基于C/C++语言编程、VHDL 或Verilog 硬件描述语言等方式,在不同要求的运行环境下进行软件开发设计,实现测距设备在IA 模式和FA模式下的应答延时、目标距离、应答效率、发射速率等测试,以及PFE、CMN 精度解算常规测试;完成对测距设备灵敏度和动态范围、应答器译码能力[4]、应答器邻道抑制和通频带等性能的高级测试。经现场与精密测距器配合测试试验,结果表明:设备性能稳定可靠,现场使用便携,测试精度满足测距设备检测误差要求,能够有效解决精密测距器无法实现常态化和定期检测校验的难题。

1 检测设备结构及原理

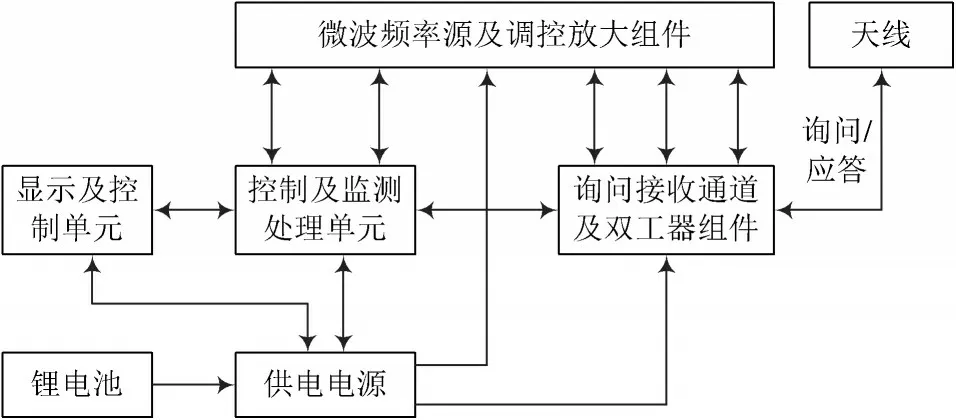

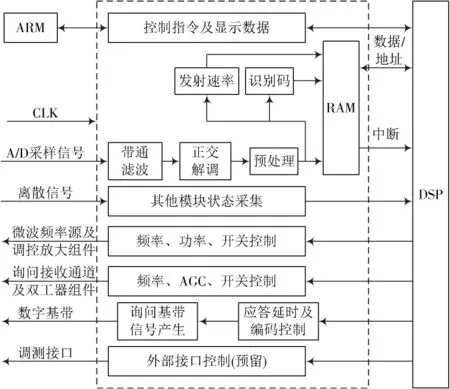

专用检测设备主要包括询问器、天线和馈线三部分,其总体构成框图如图1 所示。询问器由控制及监测单元、微波频率源及调控放大组件、询问接收通道及双工器组件、显示及控制单元、电源模块等组成。在控制及监测处理单元控制下,微波频率源及调控放大组件生成激励信号,经过调制、放大处理产生距离询问脉冲对,通过询问接收通道及双工器组件和天线,向被测测距设备发射询问脉冲对。测距设备应答器接收该询问脉冲,经系统固定延时T0(单位为μs)后,发出应答脉冲对至专用检测设备接收,应答脉冲经双工器组件进入询问接收通道,放大、处理进入控制及监测处理单元,如确认为本次询问的应答脉冲,即测出发射询问脉冲至应答脉冲之间的延时时间T,所测距离L为:

图1 专用检测设备总体构成框图

式中C为电磁波传播速度,取值为3×108m/s。

2 检测设备硬件设计

2.1 控制及监测单元

控制及监测单元采用FPGA、DSP 和ARM 为主体的设计架构,主要包括ADC 及DAC、FPGA、DSP、ARM、电源等单元电路。单元电路原理框图如图2 所示。

图2 控制及监测单元电路原理框图

2.1.1 ADC 及DAC 单元设计

ADC 单元主要基于AD9467 芯片,采用差分双巴伦平衡设计,对输入的70 MHz 模拟中频进行滤波,单端到差分转换,将模拟中频信号转换为数字信号,并传送到FPGA 单元进行处理。DAC 单元主要基于LTC1668 芯片,输出采用差分电流型设计,将FPGA 传送的数字基带包络信号转换为模拟基带包络信号,并通过放大器放大到0~4 V 幅度输出。

2.1.2 FPGA 单元设计

FPGA 选 用XC7K325T-2FFG900I 芯 片[5],主 要 产 生控制逻辑信号,发送基带包络信号,接收预处理70 MHz中频信号。设计采用了Master SPI 配置模式,M[2:0]=001,按照x4 总线宽度的程序加载设计。系统时钟由恒温晶振10 MHz 参考时钟经PLL 芯片产生150 MHz 的LVDS 时钟提供。

2.1.3 DSP 单元

DSP 单元选用TMS320C6416 芯片作为信号处理算法的主体,对FPGA 预处理的数据进行分析、计算。设计采用了EMIF 8 bit ROM BOOT 模式,即BEA[19:18]=10。DSP 时钟是通过DSP 的PLL 输入时钟50 MHz,经内部12 倍频(600 MHz)为CPU 提供信号。

2.1.4 ARM 单元设计

ARM 选用MCIMX6Q6AVT10AC 芯片,主要与显示及控制单元键盘、显示屏等协作实现人机交互界面设计。设计采用8 bit eMMC Boot,启动SD4S 接口,即单板设 置BOOT_CFG1[7:4]=011X,BOOT_CFG2[6:5]=10,BOOT_CFG2[4:3]=11。ARM 的 源 端 时 钟 由24 MHz 和32.768 kHz 两个高低频晶体振荡器提供。ARM 的DDR使用多模式DDR 控制器,设计中使用DDR3×64 存储类型,DDR3 存储大小为1 GB,数据位宽为64 bit。

2.1.5 环路滤波器设计

根据环路滤波器设计准则,环路带宽小于1 /10 的鉴相频率(10 MHz)即小于1 MHz,相位裕度大于45°。实际设计环路带宽为409 kHz,相位裕度为66.2°,滤波器电容选择温度系数好的NPO 电容。

2.1.6 电源单元设计

电源单元主要是将外部输入的5 V 电源转换为各个芯片的工作电源,并实现电源的上电时序控制。

2.2 微波频率源及调控放大组件

组件工作在L 波段,微波频率源主要实现1 024~1 151 MHz询问脉冲发射,产生一本振1 642~1 893 MHz和二本振750 MHz 的激励工作频率;调控放大组件对询问发射激励频率进行脉冲调制和幅度调制,实施功率控制并放大至20 W 功率,同时给出相应的监测信号。

2.2.1 频率合成源

频率源是低相噪、多频点组件,主要为设备提供低相噪的L 波段频率合成信号,即产生1 个P 波段的单点频率和2 个L 波段的多点频率。电路采用模块化设计,实现了电路小型化、高稳定度、低相位噪声、宽频带、小步进的技术要求。

2.2.2 调制放大器

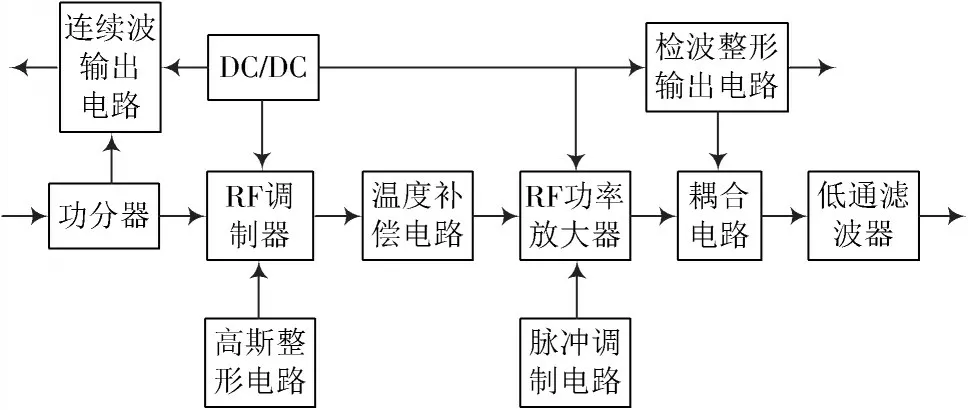

电路采用线性放大电路,由功率分配器、RF 高斯脉冲调制器、RF 功率放大器、高斯脉冲整形电路、开关脉冲调制电路等组成,其原理图如图3 所示。

图3 调制放大器原理框图

功率分配器将频率源输出信号进行功率分配,一路放大输出至(10±1.5)dBm,为连续波输出,输出选用GALI-2 器件,采用开关控制,保证其辐射泄漏低于-40 dBm;另一路进入RF 高斯脉冲调制器,调制器采用两个高线性高速衰减器完成高斯脉冲的射频线性调制,调制度大于50 dB。RF 功率放大器设计选用GaAsFET 进行三级放大,将调制的高斯脉冲信号不失真放大输出至20 W 电平,输出通过微带低通滤波器,其抑制谐波电平输出大于50 dBc。脉冲调制器即RF 开关,主要是提高收发之间的隔离,降低反射通道的漏信号对接收的干扰,开关射频通断比设计大于50 dBc。

2.3 询问接收通道及双工器组件

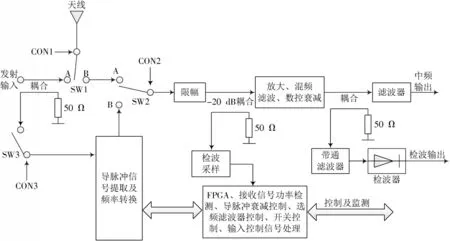

组件工作在L 波段,主要实现应答信号和导脉冲信号的变频滤波和放大、应答信号和导脉冲信号功率检测、中频信号视频检波、接收通道增益控制以及数字处理与控制等功能。其原理框图如图4 所示。

图4 询问接收通道及双工器组件原理框图

设备为收发分时工作模式[6],天线端口设计分立式PIN 开关实现收发状态切换。在询问信号通过天线发射时,导脉冲电路耦合提取询问信号(1 025~1 150 MHz)与63 MHz 本振信号,混频得到962~1 213 MHz 的导脉冲信号,FPGA 接收外部送入的频率码,对其进行控制、选频及滤波放大,由SW2 选通输出至接收通道。导脉冲信号通过低噪声放大和镜频滤波送入增益控制衰减器进行幅度控制,与一本振(1 642~1 893 MHz)和二本振(750 MHz)混频滤波输出70 MHz 中频信号,同时经耦合检波输出视频脉冲信号。接收功率检测是通过低噪声放大器后检波输出包络信号,经A/D 视频包络采样处理,再通过FPGA 计算出对应的输入功率值。

2.4 显示及控制组件

显示及控制组件主要包括键盘、导光板LED、液晶显示屏、对外接口及指示灯等驱动控制。键盘采用十六进制扫描码对应数字、字母及标准功能键;背光采用LED 冷光源,提高发光效率;显示屏支持垂直和水平视角大于70°,亮度非均匀性小于20%;17 个外部接口完成指示灯、开关和通信接口,RJ 45 网口、USB 接口及RS 232 采用标准定义,RF 输入、连续波输出、发射检波、中频检波、同步输出采用射频接口;液晶显示控制组件主要完成键盘数据、显示屏驱动、以太网口、RS 232 数据、RF 开关、电源等低频信号传送;电源采用直流12 V稳压供电。

2.5 电源模块

电源模块采用单相交流、直流和锂电池三种供电方式,按照优先交流再直流,最后锂电池顺序供电。单相AC 220 V/50 Hz 交流经AC/DC 整流滤波输出24 V 电压,一路给16.8 V/10 A 锂电池充电,另一路经DC/DC 固定稳压器输出5 V、12 V、8 V 电压供设备使用。外部15 V 电压或锂电池组16.8 V 电压经稳压输出供设备使用。电源模块具备过欠压、过温、输出短路等保护功能,可通过RS 485 接口实现对锂离子蓄电池组容量、电压及温度监测实时显示功能。

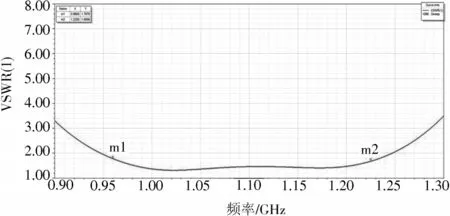

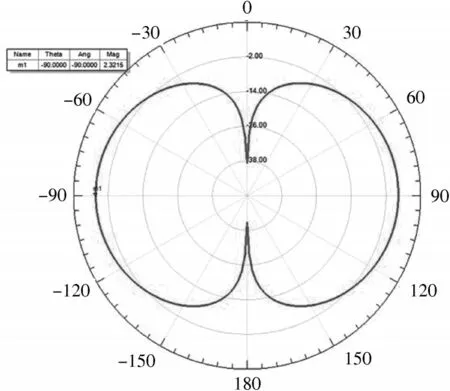

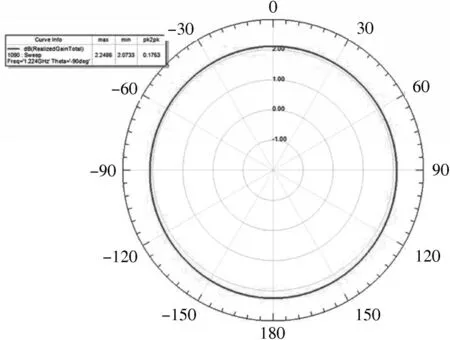

3 天线设计与仿真

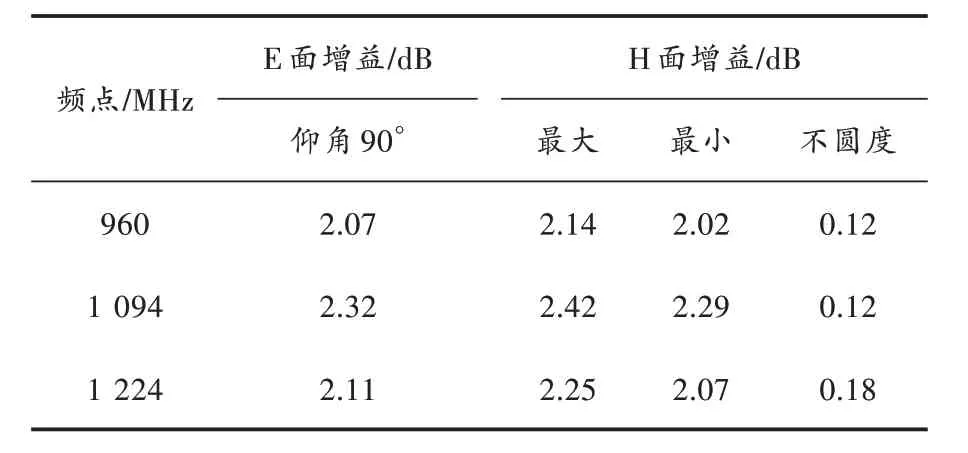

天线设计采用宽带偶极子结构形式,工作在L 频段,相对带宽为24%,建立了天线仿真模型,通过仿真软件Ansoft HFSS 对整个频段内电压驻波比进行仿真设计,仿真结果如图5 所示,满足电压驻波比小于2.0 的性能要求。设计中分别选取960 MHz、1 094 MHz、1 224 MHz低中高3 个频率点,在阻抗50 Ω 条件下进行了E 面和H 面方向图仿真,表1 给出了方向图增益仿真数据表。图6 为1 094 MHz E 面方向图,其天线增益为2.32 dB;图7 为1 224 MHz H 面方向图,其天线增益为2.07 dB,方向图增益均大于0 dB 设计指标要求。

表1 E 面和H 面方向图增益仿真数据表

图5 天线电压驻波比

图6 1 094 MHz E 面方向图

图7 1 224 MHz H 面方向图

4 检测设备软件设计

软件设计包括FPGA 信号处理、显示与控制、DSP 监控软件,在控制及监测处理单元运行。其中FPGA 信号处理软件采用VHDL 或Verilog 硬件描述语言,在ISE 环境下调试;显示与控制软件采用C/C++语言编程,在Qt环境下开发调试;DSP 监控采用C 语言和汇编语言相结合编程,在CCS 环境下调试。

4.1 FPGA 信号处理软件

FPGA 信号处理软件主要为外部电路提供离散控制信号,通过DAC 输出基带包络信号,控制ADC 对70 MHz 中频信号采样和信号处理,对外具有多种通信功能,其信号处理功能框图如图8 所示。中频信号解算过程:70 MHz 中频模拟信号经A/D 采样和数字带通滤波电路滤波,采用正交解调方式解调出基带信号,通过对信号预选判断和缓存有效信号。一是采用延迟比较法进行脉冲对识别,根据缓存基带信息进行应答脉冲的搜索、锁定,计算出距离值,将距离值作为PFE 和CMN评估模块的输入,完成对距离解算结果评估;二是记录满足脉冲编码要求的脉冲对,计算每秒钟有效脉冲对数目,即为测距设备的发射速率。

图8 FPGA 信号处理功能框图

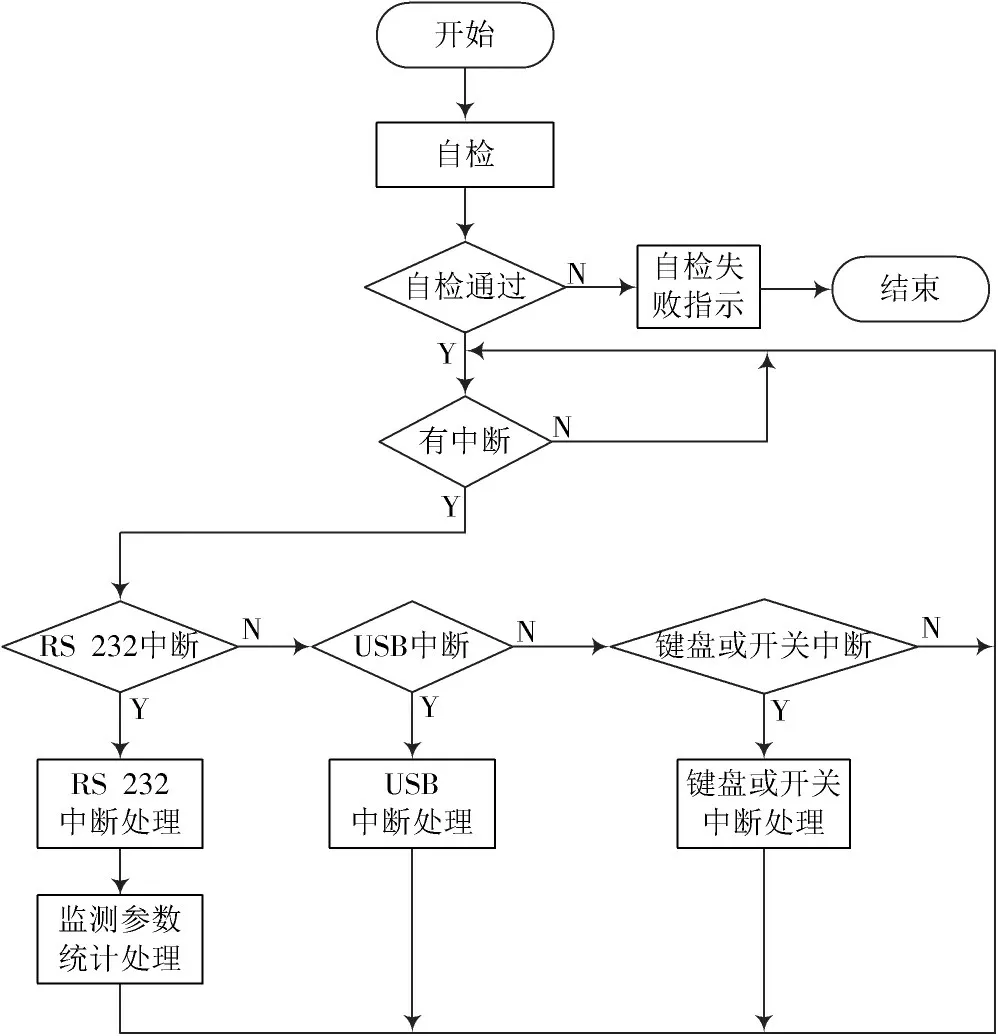

4.2 显示与控制软件

显示与控制软件主要实现对内控制及监测处理单元通信,对外提供人机交互界面,在ARM 中运行,支持用户设置参数、实时测试数据、文件管理和校准操作等功能。软件主流程如图9 所示,常规测试和高级测试功能界面如图10、图11 所示。

图9 显示与控制软件主流程

图10 常规测试功能界面

图11 高级测试功能界面

常规测试主要完成的内容有:设置波道、工作模式、距离真值、询问电平、询问速率,软件打开关闭射频,实时显示测试测量结果、延时、效率、速率、PFE、CMN 以及识别码信息;查看当前CMN 和PFE 曲线动态图;显示时间、温度、参数范围提示等。高级测试可选择指定测试选项测试,主要完成通频带测试、邻波道抑制测试、译码测试、灵敏度和动态范围测试,实时显示当前测试结果。

文件管理支持选择存储时间1 min、2 min、5 min 和10 min,存储数据自动生成以当前时间为文件名的CSV格式文件,可更新存储列表,支持数据回放。校准功能实现用户对参数进行校准,参数包含IA 和FA 模式下的X 延时、Y 延时、W 延时和Z 延时。

4.3 DSP 监控软件

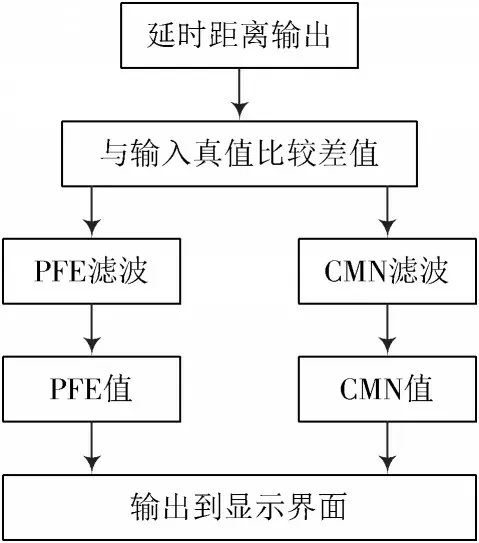

监控软件主要完成测距解算,为延时距离解算、PFE、CMN 解算及应答效率测试等提供数据输入。延时距离解算流程如图12 所示,FPGA 产生询问脉冲基带信号,经DAC 转换调制生成70 MHz 询问脉冲信号;通过AGC 脉冲峰值平均值与上下限比较控制,对应答脉冲对编码间隔进行鉴别和滤除;根据发射信号记录定时点,估算应答脉冲出现时间窗口,对窗口内记录的所有脉冲进行有效应答脉冲识别,完成距离解算,经平滑滤波解算输出延时距离[7]。

图12 测距解算流程

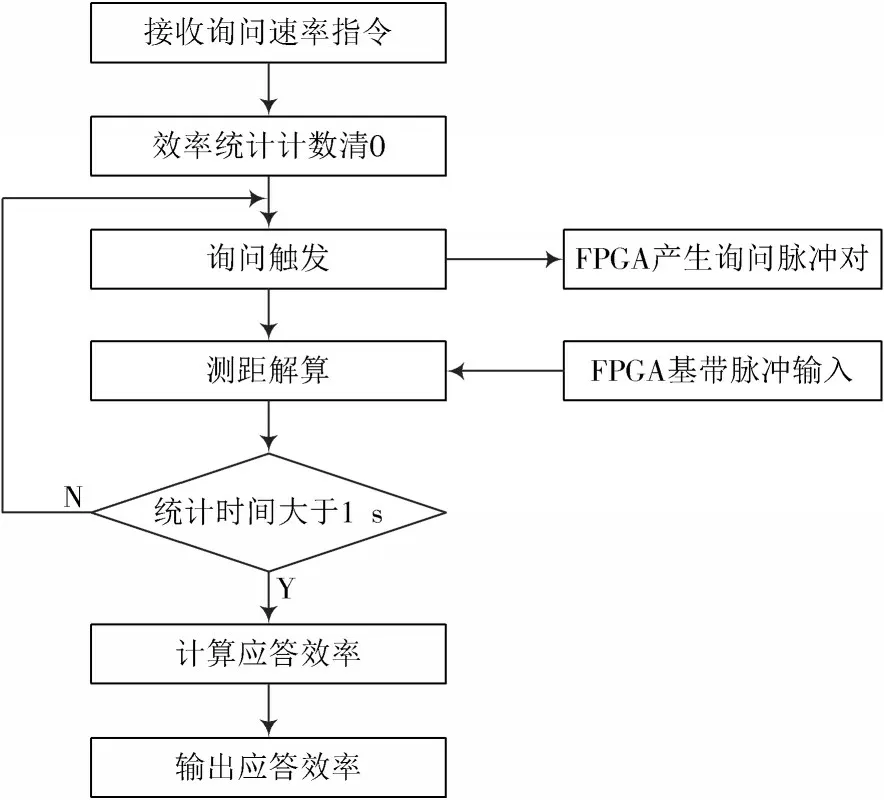

根据距离解算得到延时距离输出以及显示控制软件输入的距离真值[8],解算出PFE、CMN,软件流程如图13 所示。由显示与控制软件设置发射速率,DSP 监控软件定时触发询问脉冲发射指令,通过测距解算流程记录应答脉冲对数,1 s 计算一次应答脉冲对数与发射速率比值,即为应答效率。由FPGA 软件通过脉冲识别算法对接收信号进行筛选,若当前脉冲对满足编码要求,则认为设备发射有效脉冲对,统计1 s 内有效脉冲对的个数,即为发射速率[9]。每隔1 s,DSP 监控软件从FPGA 软件中读取一次发射速率,并输出到界面显示,具体软件流程如图14 所示。

图13 PFE、CMN 解算流程

图14 应答效率测试流程

5 实验数据与结论

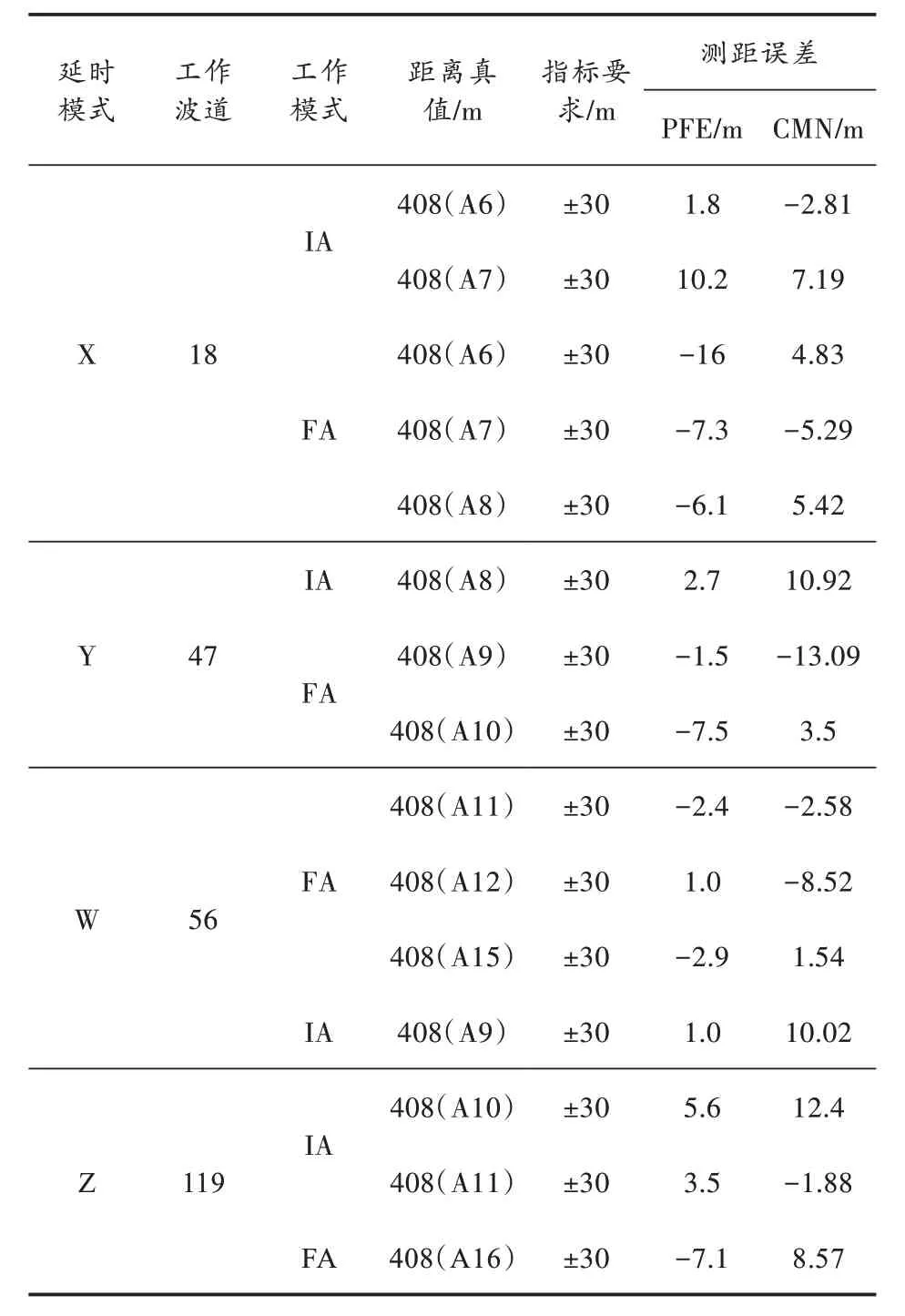

测距专用检测设备利用某机场精密测距器配合进行了现场测试验证。依据导航测距设备使用相关标准规定要求,测试环境场地选择距精密测距设备天线正向408 m、天线中心左右±20°扇区内,一字分布设置11 个测试点(A6~A16)作为标定点,标定中采用408 m 作为距离真值,专用检测设备测距天线架设高度[10]大于3 m。将设备天线、馈线与主机正确连接后,依次在A6~A16标定测试点处与实装进行配合测试,测试过程中在IA和FA 模式下分别设置X 延时、Y 延时、W 延时、Z 延时对应18、47、56、119 工作波道,在IA 和FA 模式下实测距离值,实测结果如表2 所示。

表2 专用检测设备距离测试实测数据表

表2 测试结果表明:专用测试设备具备IA 模式和FA 模式的应答延时及目标距离测试功能,验证了检测设备功能、性能的有效性和准确性。

6 结 语

本文针对精密测距器周边电磁干扰环境复杂多变、需进行常态化性能指标检测标校的实际应用情况,采用ARM 微处理器、DSP 和FPGA 等技术设计一种便携式专用检测设备。综合运用C/C++、汇编语言、VHDL 与Verilog 等,在不同编程环境下开发软硬件测试程序。在实现对精密测距器在IA 和FA 模式下的应答延时、目标距离、应答效率等常规测试的基础上,创新性地加入接收机灵敏度、动态范围、邻波道抑制和通频带等高级测试功能,并结合精密测距系统进行测试实验。

实验结果表明,所设计的专用检测设备测距精度误差满足指标要求(优于±30 m),能够有效满足精密测距器常态化检测的需求。