高带宽存储器的技术演进和测试挑战*

2023-03-22陈煜海余永涛刘天照刘焱罗军王小强

陈煜海,余永涛,刘天照,刘焱,罗军,王小强

(工业和信息化部电子第五研究所,广州 511300)

1 引言

当代电子计算机的性能表现依赖于中央处理器(CPU)和动态随机存取存储器(DRAM)内存的协同配合,在冯·诺伊曼计算机架构中,计算处理单元根据指令从内存中读取数据,完成计算处理后将数据存回内存。多年以来,CPU 的运行速度在摩尔定律的推动下快速提升,目前主流CPU 的主频高达5 GHz,而DRAM内存性能取决于电容充放电速度以及DRAM 与CPU之间的接口带宽,总体来看其性能提升速度远远慢于CPU。先进的DDR4 内存主频为2 666~3 200 MHz,带宽为6.4 GB/s。在高性能计算、数据中心、人工智能(AI)应用中,顶级高算力芯片的数据吞吐量峰值在数百TB/s 级别,但主流DRAM 内存或显存带宽一般为几GB/s 到几十GB/s 量级,与TB/s 量级还有较大差距。DRAM 内存带宽已经成为了制约计算机性能发展的重要瓶颈,即所谓阻碍性能提升的“内存墙”[1-3]。

随着集成电路工艺技术的发展,3D 和2.5D 系统级封装(SiP)和硅通孔(TSV)技术日益成熟,为研制高带宽、大容量的存储器产品提供了基础。针对内存高带宽、大容量、低功耗的需求,从2013 年开始,国际电子元件工业联合会(JEDEC)先后制定了3 代、多个系列 版 本 的 高 带 宽 存 储 器(HBM、HBM2、HBM2E、HBM3)标准[4-8]。2022 年1 月28 日,JEDEC 正式发布了JESD238 HBM DRAM(HBM3)标准,技术指标较现有的HBM2 和HBM2E 标准有巨大的提升,芯片单个引脚速率达到6.4 Gbit/s,实现了超过1 TB/s 的总带宽,支持16-Hi 堆栈,堆栈容量达到64 GB,为新一代高带宽内存确定了发展方向[9]。HBM 通过TSV 和微凸块技术将3D 垂直堆叠的DRAM 芯片相互连接,突破了现有的性能限制,大大提高了存储容量,同时可提供很高的访存带宽[10]。

目前国内对HBM 技术的研究较少,本文系统分析了HBM 标准和技术发展,研究了HBM 的晶圆级芯片测试技术。

2 HBM 的3D 结构和技术特点

2.1 HBM 的3D 堆叠结构

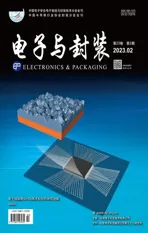

HBM 堆叠结构如图1 所示,包含多层DRAM 芯片和一层基本逻辑芯片[10]。4 层或8 层甚至更多层数的DRAM 芯片以堆叠形式整合在一起,不同DRAM芯片之间以及DRAM 芯片与逻辑芯片之间用TSV 和微凸块技术实现通道连接。每个HBM DRAM 芯片可通过多达8 条通道与外部相连,每个通道可单独访问1 组DRAM 阵列,通道间访存相互独立[11]。逻辑芯片可控制DRAM 芯片,并提供与控制器芯片连接的接口,主要包括测试逻辑模块和物理层(PHY)接口模块,其中PHY 接口通过中间介质层与CPU/图形处理器(GPU)/片上系统(SoC)直接高速连通,直接存取(DA)端口提供HBM 中多层DRAM 芯片的测试通道。中间介质层通过微凸块连接到封装基板,从而形成2.5D 的SiP 系统。

图1 HBM 堆叠结构[12]

2.2 HBM 的技术特点

2.2.1 高速、高带宽

HBM 堆栈没有以外部互连线的方式与信号处理器芯片连接,而是通过中间介质层紧凑而快速地连接,同时HBM 内部的不同DRAM 采用TSV 实现信号纵向连接,HBM 具备的特性几乎与片内集成的RAM 存储器一样。

HBM 的高速、高带宽指标如图2 所示,HBM2E和HBM3 的单引脚最大输入/输出(I/O)速度分别达到3.2 Gbit/s 和6.4 Gbit/s,低于第五版图形用双倍数据传输率存储器(GDDR5 存储器,7.0 Gbit/s)。但HBM的堆栈方式可以通过更多的I/O 数量提供远高于GDDR5 存储器的总带宽,如HBM2(1 024)带宽可以达到307 GB/s,而GDDR5 存储器(32)的带宽仅为28 GB/s。

图2 HBM 高速、高带宽性能指标

2.2.2 可扩展更大容量

HBM 具有可扩展更大容量的特性。HBM 的单层DRAM 芯片容量可扩展;HBM 通过4 层、8 层以至12层堆叠的DRAM 芯片,可实现更大的存储容量;HBM可以通过SiP 集成多个HBM 叠层DRAM 芯片,从而实现更大的内存容量。SK Hynix 最新的HBM3 堆栈容量可达24 GB。

2.2.3 更低功耗

由于采用了TSV 和微凸块技术,DRAM 裸片与处理器间实现了较短的信号传输路径以及较低的单引脚I/O 速度和I/O 电压,使HBM 具备更好的内存功耗能效特性[11]。HBM2 与传统DDR 存储器的单引脚I/O 带宽功耗比对比如图3 所示,以DDR3 存储器归一化单引脚I/O 带宽功耗比为基准,HBM2 的I/O 功耗比明显低于DDR3、DDR4 和GDDR5 存储器,相对于GDDR5 存储器,HBM2 的单引脚I/O 带宽功耗比数值降低42%[12]。

图3 HBM2 与传统DDR 存储器的单引脚I/O 带宽功耗比对比

2.2.4 更小体积

在系统集成方面,HBM 将原本在PCB 板上的DDR 内存颗粒和CPU 芯片一起全部集成到SiP 里,因此HBM 在节省产品空间方面也更具优势。相对于GDDR5 存储器,HBM2 节省了94%的芯片面积。

2.2.5 高性能计算应用

目前HBM 主要用于数据中心、AI 等高性能计算机、AI 计算加速卡、高端专业显卡,可以显著提高AI、机器学习运算的性能,如AMD Instinct、NVIDIA A100、华为Ascend 910 等AI 训练加速器以及Xilinx的Virtex UltraScale FPGA 都搭载了HBM 芯片[13-14]。未来,各种服务器、网络和其他应用程序也可能使用HBM 芯片,支持HBM 的SoC 也将更多。

3 国外HBM 产品及技术发展

HBM 在主机计算与分布存储间构建了一个紧密耦合的高速、高带宽接口,计算处理器可通过HBM 的高速宽通道完成高效、低功耗的访存操作。HBM 技术从HBM1 发展到目前最新的HBM3,I/O 速度从1 Gbit/s 提升到6.4 Gbit/s,带宽从128 GB/s 提升到819 GB/s,高性能计算与内存的差距不断减小。

3.1 第一代HBM(HBM1)

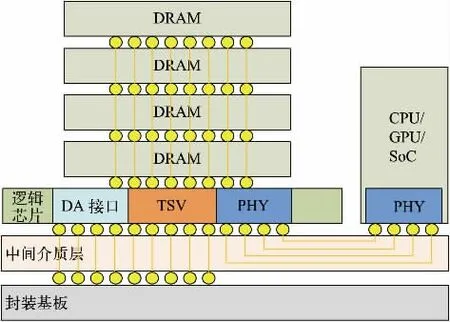

2013 年10 月,JEDEC 发布了第一个HBM 标准JESD235[4]。JESD235 标准定义了具有1 024 bit 接口和单引脚1 Gbit/s 数据速率的HBM1 存储芯片,该芯片堆叠了2 个或4 个DRAM,HBM1 堆叠DRAM 架构如图4 所示[1],在基本逻辑芯片上,每个DRAM 芯片具有2 个128 bit 通道,共有8 个阵列(B0~B7),最多支持8 个128 bit 通道(CH0~CH7),总带宽为128 GB/s。每个通道实质上是具有2n(n 代表总线位宽)预取架构的128 bit DDR 存储器接口,主要包括128 bit 数据、8 bit 行命令地址和6 bit 列命令地址、源同步时钟、校验、数据屏蔽等信号,还包括复位、IEEE 1500 测试端口和电源、地等公共信号。访存的读、写操作过程基本与DDR 存储器芯片相同。HBM1 芯片具备半独立的行、列命令接口,支持读、写命令与其他命令并行执行,增加了命令接口带宽,提高了访存性能。

图4 HBM1 堆叠DRAM 架构[1]

2015 年11 月,HBM1 标准更新为第二版——JESD235A。HBM 的位宽仍是1 024 bit,支持的数据速率提高到单引脚2.0 Gbit/s,总带宽提升到256 GB/s,堆栈容量提升到8 GB。HBM1 主要增强的功能之一是伪通道模式,该模式将通道分为2 个单独的子通道,每个子通道分别具有64 bit I/O,从而为每个存储器的读写访问提供128 bit 预取。伪通道以相同的时钟速率运行,它们共享行列命令总线、时钟信号CK 和时钟使能信号CKE。HBM1 使用伪通道模式,进一步优化通道带宽性能,降低延时,提升速率。其他改进包括用于通道软硬修复的通道重新映射模式、防过热保护等[4]。

2015 年,SK Hynix 推出HBM1,堆叠了4 个2 Gbit DRAM 芯片,采用29 nm 工艺,每个引脚的数据速率为1 GB/s,位宽为1 024 bit,每个堆栈具有1 GB 的容量和128 GB/s 的总带宽。AMD 采用HBM1 构建了其GPU 系统封装和Radeon R9 Fury/R9 Nano 视频卡[13]。

3.2 第二代HBM(HBM2)

2018 年11 月,JEDEC 在JESD235A 的基础上发布了JESD235B 标准,即HBM2 技术[5]。HBM2 充分融入了I/O 高带宽存储技术、TSV 工艺,支持最多12 层的TSV 堆叠,单片容量达到16Gbit,使用1024bit 总线,分成8 个相互独立的128 bit 通道,单引脚数据速率提升到2.4 Gbit/s,总带宽达到307 GB/s。HBM2 可以在全带宽下支持2 层、4 层、8 层和12 层的TSV 堆栈,从而使系统在容量要求方面具有灵活性,堆栈容量为1 GB 和24 GB。为适应12 层大容量高密度封装,HBM2 增加了新的封装选项,并更新多输入特征寄存器(MISR)的配置,测试部分和兼容性与HBM1 保持一致。

相对于SK Hynix 主导研发的HBM1 存储芯片,三星、镁光等公司也都推出HBM2 产品,且三星更为领先。2018 年,三星宣布量产第二代高带宽显存Aquabolt(HBM2),可提供每引脚2.4 Gbit/s 的数据传输速度,I/O 电压为1.2 V,8 GB HBM2 封装将提供307 GB/s 的数据带宽,数据传输速度是GDDR5 存储器芯片(32 GB/s 数据带宽) 的9.6 倍,包含4 个Aquabolt 的显卡,传输性能可达到1.23 TB/s[15]。

3.3 第三代HBM(HBM2E)

2020 年1 月,JEDEC 更新发布HBM 技术标准JESD235C,并于2021 年2 月更新为JESD235D,以支持增加的带宽和容量,即HBM2E[7-8]。按照HBM2E 技术规范,单片最大容量为16 Gbit,支持2 层、4 层、8 层和12 层的TSV 堆栈,无标准高度限制,最大堆栈容量为24 GB,支持IEEE 1500 测试,独立8 通道和16 个伪通道,单引脚的数据传输速率提升到3.2 Gbit/s,匹配1 024 bit 总线,单堆栈理论最大带宽为410 GB/s。

2019 年,三星推出Flashbolt HBM2E 内存,堆叠8个16 Gbit DRAM 芯片,使用TSV 技术实现8 芯片堆栈配置互连。每个Flashbolt 封装都具有1 024 bit 总线,每个引脚的数据传输速率达到3.6 Gbit/s,提供高达460 GB/s 的带宽[16]。

3.4 第四代HBM(HBM3)

2022 年1 月,JEDEC 发布了HBM3 高带宽内存标准JESD238,即第四代HBM 技术[9]。HBM3 在带宽、通道、存储密度、可靠性、能效等层面进行了扩充升级。

在HBM2 架构基础上,HBM3 扩展到更高的带宽,将HBM2E 的每引脚数据速率提高1 倍,并定义了高达6.4 Gbit/s 的数据传输速率,相当于819 GB/s;将独立通道的数量从HBM2 的8 个增加到16 个,每个通道有2 个伪通道,HBM3 实际上支持32 个通道;支持4 层、8 层和12 层TSV 堆栈,并为未来扩展至16层TSV 堆栈做好了准备,支持8~32 Gbit 的单层存储容量,堆栈容量为4~64 GB。HBM3 引入了片上纠错(ECC)技术,支持实时错误报告,满足更高级平台的可靠性、可用性和可维护性(RAS)需求。I/O 电压降低至1.1 V,能效进一步提升。

在HBM3 标准推出前,SK Hynix 推出了HBM3内存。SK Hynix 最新的HBM3 芯片堆栈容量为24 GB,最高带宽达到了819 GB/s,相比HBM2E 提升了78%。目前,HBM3 内存提供16 GB 和24 GB 2 种类型,分别为8 层和12 层堆叠,每层容量为16 Gbit[17]。Rambus推出的HBM3 内存单引脚的数据传输速率高达8.4 Gbit/s,带宽突破1 TB[18]。

3.5 HBM 技术性能对比

从2013 年JEDEC 发布第一代HBM 技术标准JESD235 到2022 年发布第四代HBM 技术标准JESD238,在不到10 年的时间里,HBM 技术发展经历了4 代,其性能对比如表1 所示,芯片I/O 速度和带宽大幅度提升。

表1 HBM 技术性能指标对比[4-9]

4 HBM 测试方法

与DRAM 芯片不同,HBM 采用多层“已知良好堆叠芯片”(KGSD)设计,将4 层或者更多层的DRAM芯片堆叠在基础逻辑芯片上,每层KGSD 采用了大量的TSV 和微凸块,且最终的HBM 产品不是封装级成品而是以KGSD 的形式提供,这对HBM 产品的测试技术提出了重要挑战。

4.1 HBM 的测试流程

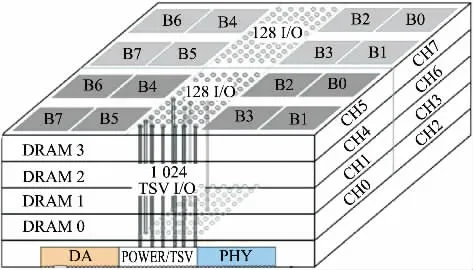

常规的DRAM 芯片测试包括晶圆级测试和封装级测试。晶圆级测试包括晶圆老化(WLBI)、高低温测试和存储修复等,通过测试的晶圆方可进行封装。封装级测试主要包括高低温条件下的功能、电性能、电参数以及老化应力测试等。

DRAM 和HBM 测试流程如图5 所示。HBM 测试包括晶圆级测试和KGSD 测试,晶圆级测试针对DRAM 芯片和逻辑芯片,其中DRAM 晶圆测试与常规DRAM 测试相同,而逻辑晶圆需要进行逻辑测试,主要测试嵌入式知识产权(IP)(IEEE Std 1500)、存储器内建自测试(MBIST)和PHY 电路中的缺陷。对测试合格的HBM 晶圆进行切片和多层堆叠工艺处理,即可形成KGSD 产品。HBM KGSD 测试包括老化应力测试、高低温条件下的功能、电性能、电参数测试等[20]。

图5 DRAM 和HBM 测试流程

对于堆叠KGSD 结构的HBM 产品,无法使用传统的DRAM 封装级产品测试设施和解决方法,与常规DRAM 测试相比,HBM KGSD 裸片测试的挑战主要包括逻辑芯片测试、动态向量老化应力测试、TSV 测试、高速性能测试、PHY I/O 测试以及2.5D SIP 测试。

4.2 HBM KGSD 芯片测试方法

4.2.1 HBM 逻辑芯片测试

HBM 的逻辑芯片主要包括PHY 接口、TSV、可测试设计(DFT)测试逻辑模块和DA 端口。HBM KGSD通过PHY 接口与处理器芯片连接进行读写操作,而DA 端口是HBM KGSD 主要的测试接口。DA 端口具有微凸块和焊盘,进而通过中间介质层和封装基板直接连接到球栅阵列(BGA)封装的焊球。HBM 标准对DA 端口数量及位置进行了规定,成为HBM 逻辑芯片和DRAM 芯片测试和故障分析的主要通道[1]。

HBM 逻辑芯片的DFT 测试逻辑模块实现逻辑芯片的测试,包括扫描测试和高速PHY 测试。扫描测试矢量的设计要求满足大于99%的固定故障和大于85%的转换故障的测试覆盖率[19]。为了适应DRAM 测试设备的测试矢量存储深度,扫描测试矢量被分解成较小的测试矢量。HBM 逻辑芯片测试通过使用DFT减少了所需要的DA 端口。

4.2.2 HBM DRAM 芯片老化应力测试

为了保证HBM KGSD 的质量,需要在高温条件下对HBM DRAM 芯片进行动态和静态应力测试。在HBM 晶圆键合前的测试阶段,只采用静态应力测试。与DRAM 封装级测试的情况不同,由于晶圆级产品动态老化应力施加技术难度大、成本高,难以对KGSD进行老化动态应力测试。

针对HBM KGSD 芯片老化动态应力测试问题,SK Hynix 研究开发了基于DFT 的HBM KGSD 晶圆级动态应力老化测试方法,覆盖了电压应力、温度应力以及存储状态翻转,可代替DRAM 封装级产品老化应力测试[1]。

4.2.3 TSV 测试

HBM KGSD 芯片有超过10 000 个内部TSV,用于传输逻辑芯片和DRAM 芯片之间的数据和命令信号。常见的TSV 失效包括开路、裂纹、沾污以及微小开路。TSV 测试主要是开路/短路测试,确认TSV 和微凸块的连接性。巨大的TSV 数量对TSV 可靠性及其测试提出了挑战。

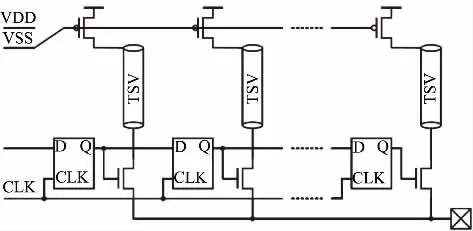

TSV 开路/ 短路测试电路如图6 所示,包括DRAM 芯片的驱动晶体管和选择TSV 路径的逻辑电路。在驱动晶体管开启条件下,电流通过TSV 和选择逻辑电路流向DA 监测端口,测试电流大小并判定合格或失效。良好的TSV 通道电流在合格范围内,开路的TSV 可以通过冗余TSV 进行修复。对于大量的TSV 测试和修复,采用内建自测试方案以减少测试时间,由于可现场修复失效的TSV,现场可靠性更好。TSV 测试可以精确定位每个失效的TSV,并进行关键的故障分析,有利于进一步改进工艺。

图6 TSV 开路/短路测试电路[12]

4.2.4 HBM KGSD 高速性能测试

针对DRAM 芯片高速信号性能测试要求,常规DRAM 封装级测试使用自动化测试机台(ATE)配合专用测试座来进行高速测试。根据HBM KGSD 的测试流程,HBM KGSD 的高速性能测试是晶圆级测试,采用ATE 机台、晶圆探针台结合测试探针卡的测试方法[20]。基于测试探针卡的HBM KGSD 高速性能测试难点主要涉及高速信号传输的信号完整性保证、功率传输以及大量高可靠的电气连接需求[21]。以HBM2 测试要求为例,信号传输速率大于2.4 Gbit/s,需要提供5 000~10 000 个微凸块可靠电气连接。为了提高测试效率,HBM KGSD 高速测试需要多芯片并行测试,进一步提高了测试难度。对于性能指标更高、容量更大的HBM3 KGSD 产品,高速测试挑战将进一步提升,MBIST 可能是高速测试的解决方案。

4.2.5 HBM KGSD PHY I/O 测试

HBM KGSD 芯片有超过1 000 个PHY I/O 和微凸块,由于直径和间距很小,只能通过DA 端口进行测试。如何覆盖大量PHY I/O 通道和微凸块,并测量GB/s 级的高速信号是HBM KGSD PHY I/O 的测试难点。HBM 标准规定了采用DFT 可测性设计功能进行PHY I/O 测试的方法,主要包括直流(DC)测试和交流(AC)测试[19]。另外,使用微观视觉检查方法可以检测微凸块缺失、错位或倾斜等芯片I/O 结构失效。

4.2.6 HBM 2.5D SiP 系统测试

在HBM 堆叠完成后,HBM 产品以KGSD 的形式交付,然后与处理器芯片一起集成到2.5D SiP 结构中。2.5D SiP 通过微凸块实现HBM 和处理器芯片的超短间距连接,使得SiP 具有更小的结构几何尺寸、更高的速度、更大的功率和更好的延迟性能。2.5D SiP 结构也对HBM 的测试和调试提出了挑战,需要平衡高质量和低成本。2.5D HBM SiP 的设计和制造是一个复杂体系,涉及HBM 堆栈、信号处理芯片和中介层芯片供应商,以及组装和测试厂商。HBM KGSD 是非常敏感的器件,在2.5D 组装过程中容易退化或损坏。与PCB 上的传统封装芯片不同,2.5D SiP 系统中,晶圆级的HBM 堆栈和信号处理器芯片既不可返修也不可重新测试,基于DFT 的HBM 测试和故障修复是主要的技术手段。JEDEC 的HBM 标准规定了通过IEEE 1500 接口进行测试和修复的功能指令,如EXTEST_TX/_RX、DWORD/AWORD_MISR、MISR_MASK、MBIST、SOFT/HARD_LANE_REPAIR 以及SOFT/HARD_REPAIR[9]。

5 结束语

HBM 作为一种新型的内存技术,为高性能计算处理器提供了一个紧密耦合的高速、高带宽接口,在高性能计算技术牵引下,HBM 的技术性能快速提升,并已广泛应用于高性能计算处理器、AI 计算加速卡、高端专业显卡等。从2013 年JEDEC 发布第一代HBM技术标准JESD235 到2022 年发布第四代HBM3 技术标准JESD238,其I/O 速度从1 Gbit/s 提升到6.4 Gbit/s,HBM 堆栈容量从1 GB 提升到64 GB,带宽从128 GB/s 提升到1 TB/s 及以上,内存与高性能计算需求的差距不断缩小。

与DRAM 内存芯片相比,HBM 是一种3D 堆叠DRAM,由带有大量微凸块的KGSD 堆叠构成,采用TSV 和2.5D SiP 技术,实现了更高带宽的内存访问、更小的功率和外形尺寸,对HBM 测试也提出了诸多挑战。HBM 测试包括晶圆级测试和KGSD 测试,晶圆级测试增加了逻辑芯片测试,KGSD 测试替代了常规的封装级成品测试。HBM KGSD 测试主要采用ATE测试机台、晶圆探针台和专门制作的测试探针卡,通过DA 端口进行基础逻辑芯片测试和DRAM 核心芯片测试。HBM KGSD 的动态老化应力测试、大量内部TSV 结构的可靠性测试、高速信号测试、数量超过1 000 的PHY I/O 测试等是芯片测试和质量保证的难点。可测性设计、扫描测试、内建自测试是目前国外HBM 芯片测试的主要方法。