基于FPGA的多功能阵列信号处理系统设计

2023-03-19孙卫杰刘马良

罗 欣,冯 武,孙卫杰,刘马良

(1.中国电子科技集团公司第二十七研究所,河南 郑州 450047;2.西安电子科技大学 微电子学院,陕西 西安 710071)

随着现代雷达的发展,新体制和新技术不断涌现,针对阵列信号处理的研究成为雷达领域的一个热点[1-4]。阵列信号处理通过采用分散排列的传感器阵列和多通道接收机,来获取信号在时域和空域等多个维度的信息,以达到目标检测和跟踪的目的。与传统的雷达相比,阵列信号处理具有通道数多、实时性强、数据量大等特点[5-6]。

在现有的阵列信号处理系统中,通常选择现场可编程门阵列(Field Programmable Gate Array,FPGA)芯片或数字信号处理器(Digital Signal Processor,DSP)芯片来进行设计[7-10]。随着采样通道数的增多,系统设计的复杂度进一步加大。为了降低开发难度并提高设计效率,本文结合某项目的实际需求,设计了一种集成度较高的多功能阵列信号处理系统。该系统通过选用先进的超大规模FPGA器件和高性能模数转换器(Analog to Digital Converter,ADC),实现了对40路中频回波数据的采集控制,并完成数字下变频、数字波束合成、波束控制、通信交互以及高速数据传输等多种功能。

1 主要芯片选型

1.1 FPGA电路设计

系统的核心处理器件FPGA选用一片XILINX公司生产的VIRTEX-7(V7)系列的XC7VX690T。该FPGA的主要资源介绍[11]如表1所示。

从表1中可以看出,XC7VX690T具有丰富的逻辑资源、计算单元以及大量的高速接口资源。其中,多吉比特速率收发器(Multi-Gigabit Transceiver,MGT)接口通过配置GTH(Gigabyte Transceiver H)模块来实现。

表1 XC7VX690T资源

1.2 ADC电路设计

通道数据采集是本系统的核心功能之一。本系统要求同时采集40个通道数据。由于通道数量多且设计难度大,模数转换之后数字信号性能将直接影响信号处理性能[12-13],因此在设计时,需要保证足够的信噪比,并且要尽可能降低40个AD通道间的串扰和不一致性。为了提高系统的集成度、降低设计难度、减少系统功耗,本文采用单片多通道ADC芯片来代替多个单通道ADC芯片。

结合实际项目需要,通过前期调研和选型后,本文选用TI 公司的 8 通道14 bit的高速ADC 芯片ADS5294。该芯片具有较低的工作电压,最大采样速率高达80 Msample·s-1[14]。在本系统中,仅使用5片就可以实现对40个通道中频信号的同步采集。

1.3 网口电路设计

为了实现本系统与外围上位机软件的通信控制,采用网络信号来进行设计。考虑到FPGA主控芯片要实现的功能较多,为了进一步节省资源,选用W5300网络芯片。

W5300内部集成了物理层(PHY)芯片,可支持10 BaseT/100 BaseTX的以太网速率。它与主控芯片通过每个发射器/接收器(TX/RX)端口的先进先出(First In First Out,FIFO)寄存器进行访问,可以选择直接访问或者间接访问的方式,与FPGA配合良好,对片内资源占用较少[15]。

2 系统架构实现

2.1 总体结构

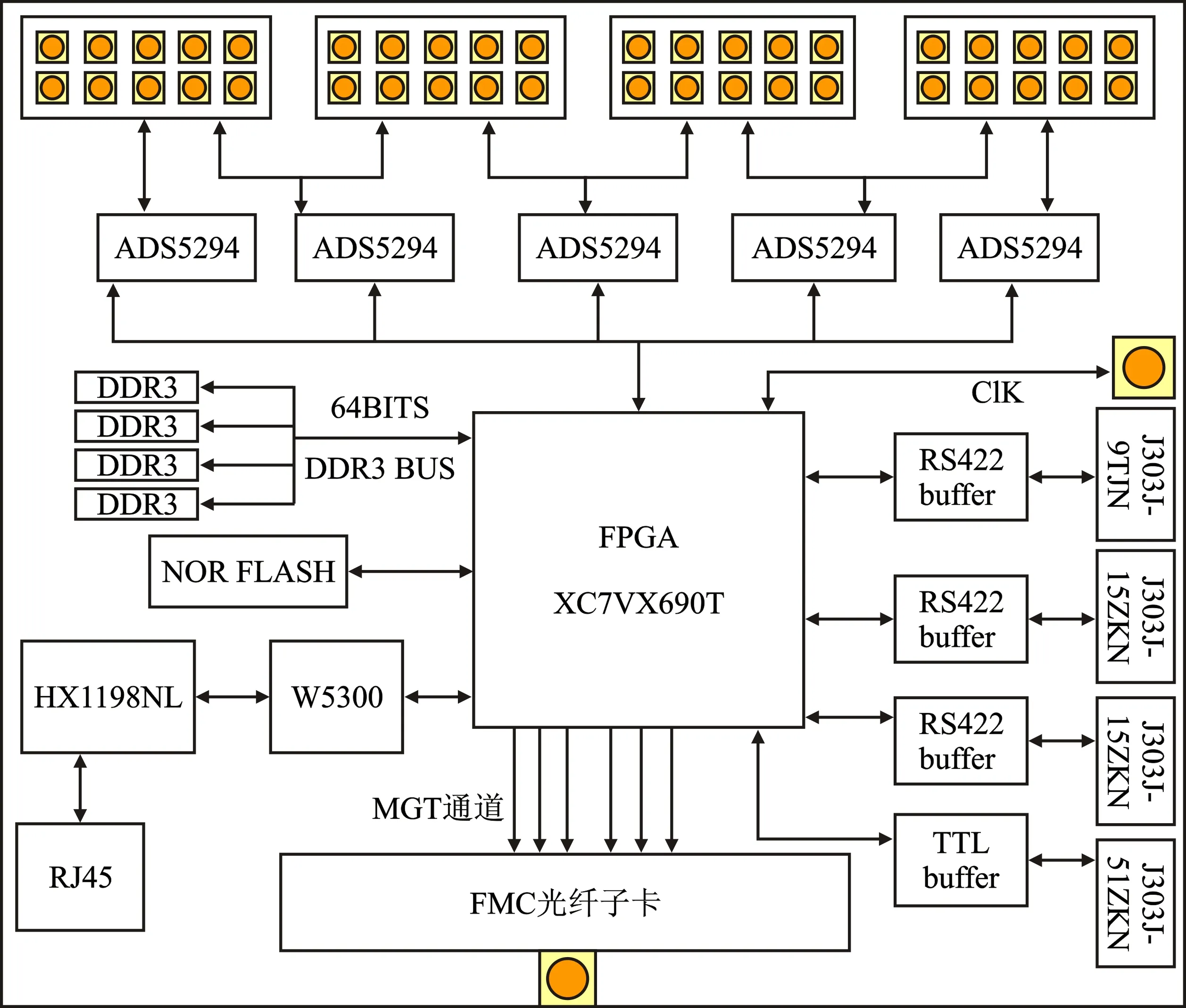

通过采用V7 FPGA和多通道高速ADC芯片,本系统具备了较好的海量数据实时处理能力。为了满足大数据量的传输需求,本文设计采用了MGT接口,并通过外接光纤模块来输出处理后的数字信号[16-17]。

在结构上,采用母板与子板的设计方式:母板采用非标准尺寸,设计时尽量节约空间;子板主要包括光纤收发器和波分复用模块。两者通过标准的FPGA夹层卡(FPGA Mezzanine Card,FMC)高速接口进行连接。外部配套专门的壳体结构件,将板卡安装在结构件内部,使得整个系统具有较好的稳定性和便携性,也便于配套雷达整体安装。系统的总体结构框图如图1所示。

图1 多功能阵列信号处理系统总体框图Figure 1. Overall block diagram of multifunctional array signal processing system

2.2 对外接口

本系统包含大量对外接口,可作为主控模块,实现与多个功能模块互联。

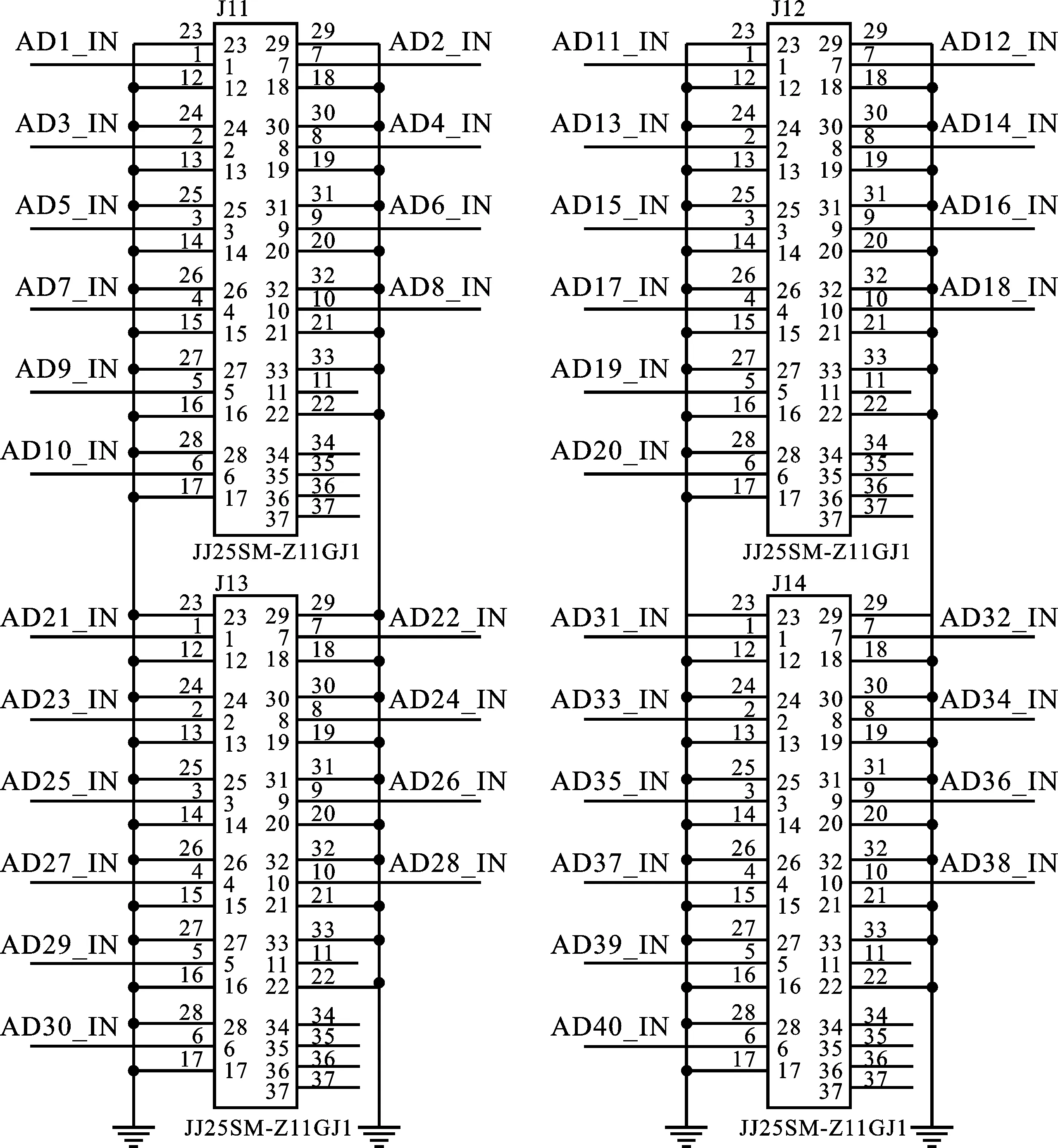

ADC采样部分由于通道数多,选用集成式连接器,这样既可以增加系统的稳定性,又可以节约板卡的设计面积。其接口示意图如图2所示。

图2 ADC接口示意图Figure 2. Interface diagram of ADC

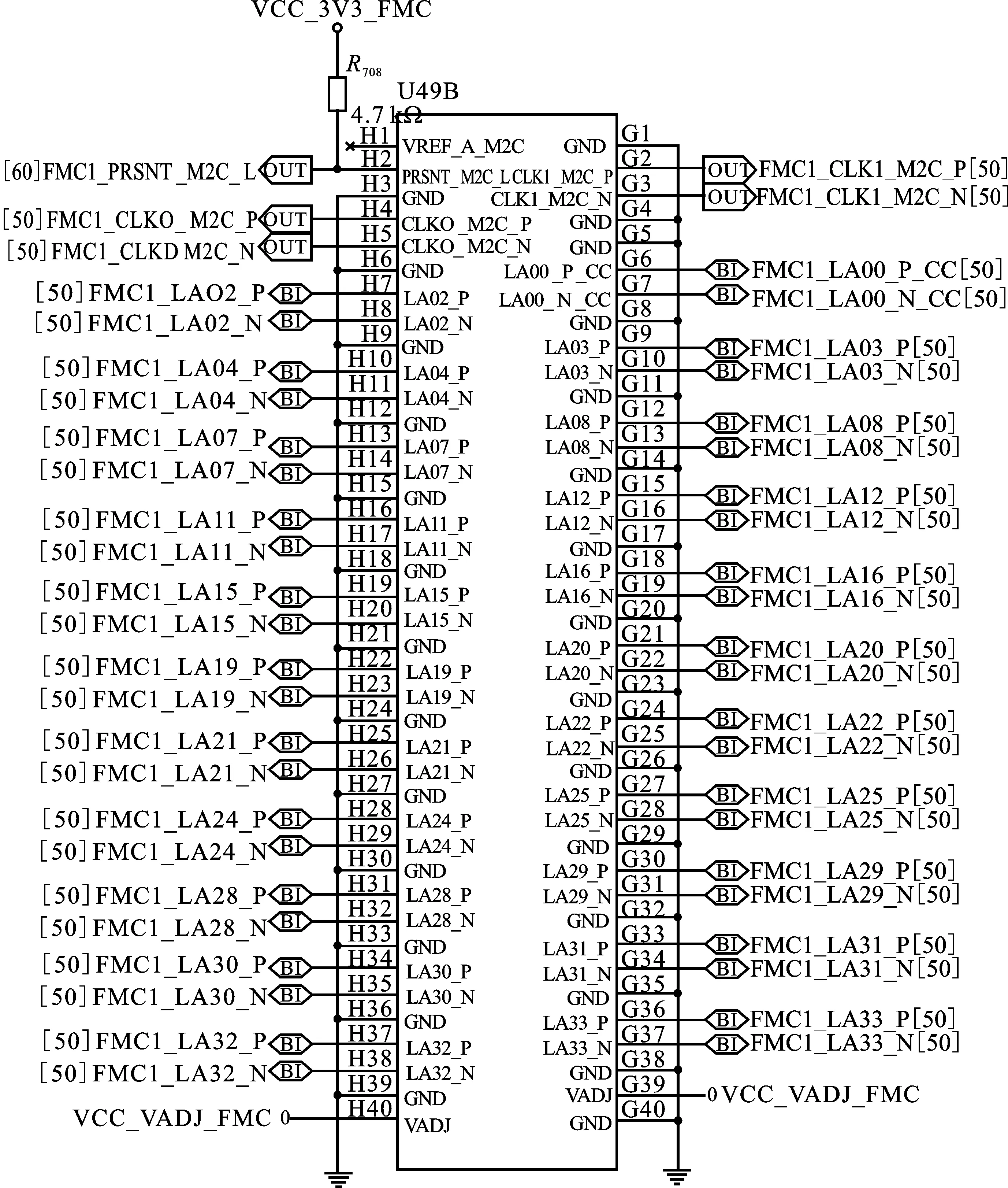

FMC接口的IO数量较多,其部分结构如图3所示。

图3 FMC接口部分示意图Figure 3. Interface diagram of FMC

对外通讯接口还包含章节1中提到的1路百兆网口,其可与上位机软件进行指令交互。3路RS-422接口可实现与波形板、伺服转台、编码器的通信控制。另外,本系统还具有40路对外的TTL(Transistor-Transistor Logic)接口,可与T/R(Transmitter and Receiver)组件进行连接,以实现对波束的控制。

3 软件功能设计

本系统的所有功能都通过设计FPGA软件来实现,其框图如图4所示。

图4 FPGA软件功能示意图Figure 4. Schematic diagram of FPGA software function

首先,FPGA接收40路中频ADC信号并进行数字下变频(Digital Down Converter,DDC)处理,得到40路基带I/Q(In-Phase and Quadrature)信号。然后,由网络数据转发模块负责与上位机软件的通信,交互指令,并下发数字波束合成所需的权重数据。最后,对合成后的波束数据进行组帧处理,并通过GTH发送模块传出。同时,由RS-422串口信号和TTL信号对本系统的外联设备进行控制指令的上传下达。

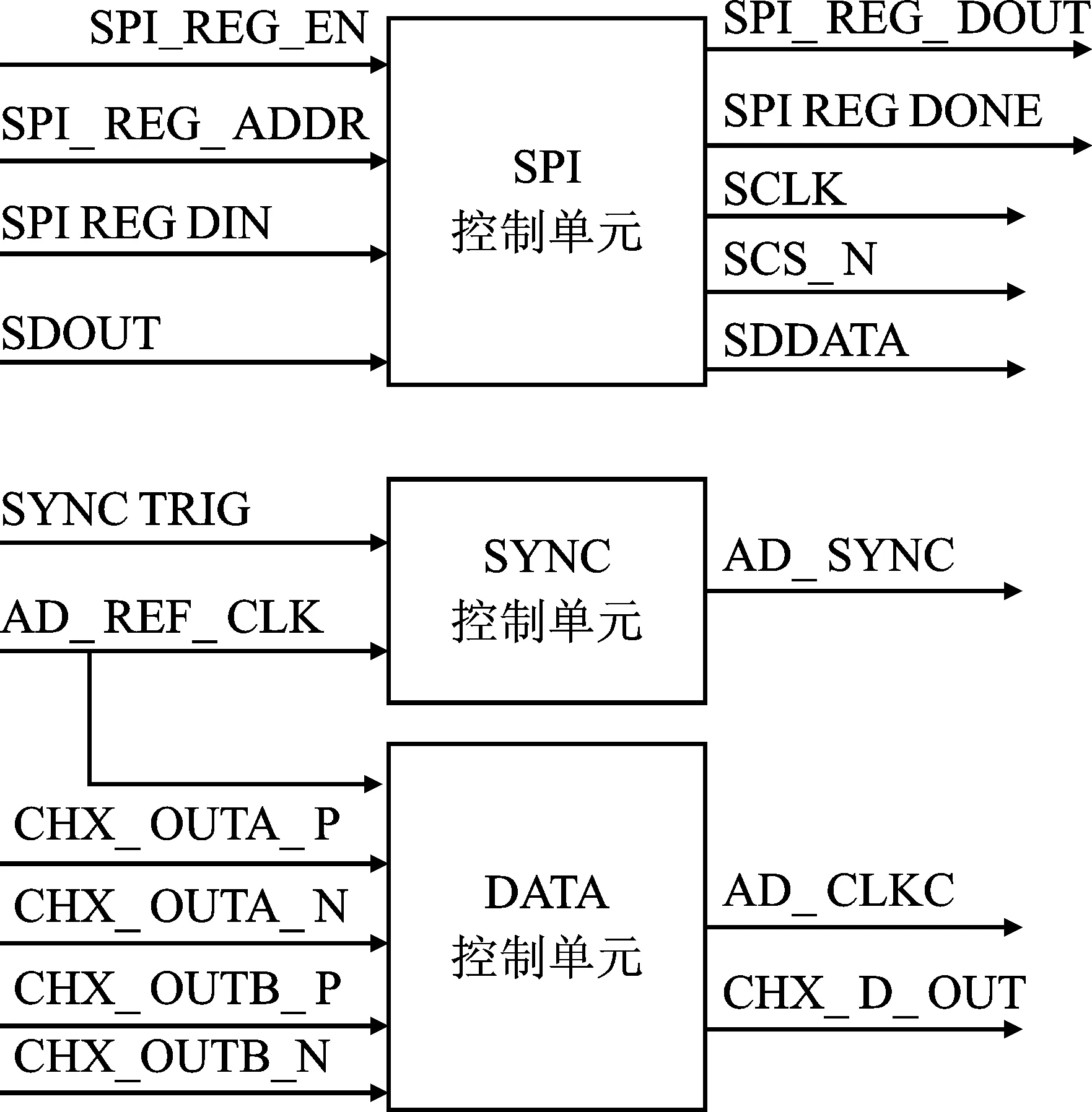

3.1 信号采集模块

信号采集模块与ADC采样电路相连,用来获取40路中频段的高速采样数据,主要包括SPI(Serial Peripheral Interface)控制单元、SYNC控制单元和DATA控制单元3大部分。其主要信号示意图如图5所示。

图5 信号采集模块示意图Figure 5. Schematic diagram of signal acquisition module

FPGA通过SPI控制单元完成对ADS5294内部寄存器的访问,并对该芯片的工作参数进行配置。 SYNC控制单元输出SYNC信号,在物理通道和时序设计时,使得SYNC脉冲在同一时刻到达所有ADC芯片的所有通道,可让多通道数据保持同步采样。DATA控制单元负责采集40路AD串行数据,为了增加系统的稳定性,保证较低的功耗,在设计实现时,选用每通道2线制的LVDS(Low Voltage Differential Signaling)信号模式,一路采样数据对应A、B两组差分信号。

3.2 数字下变频模块

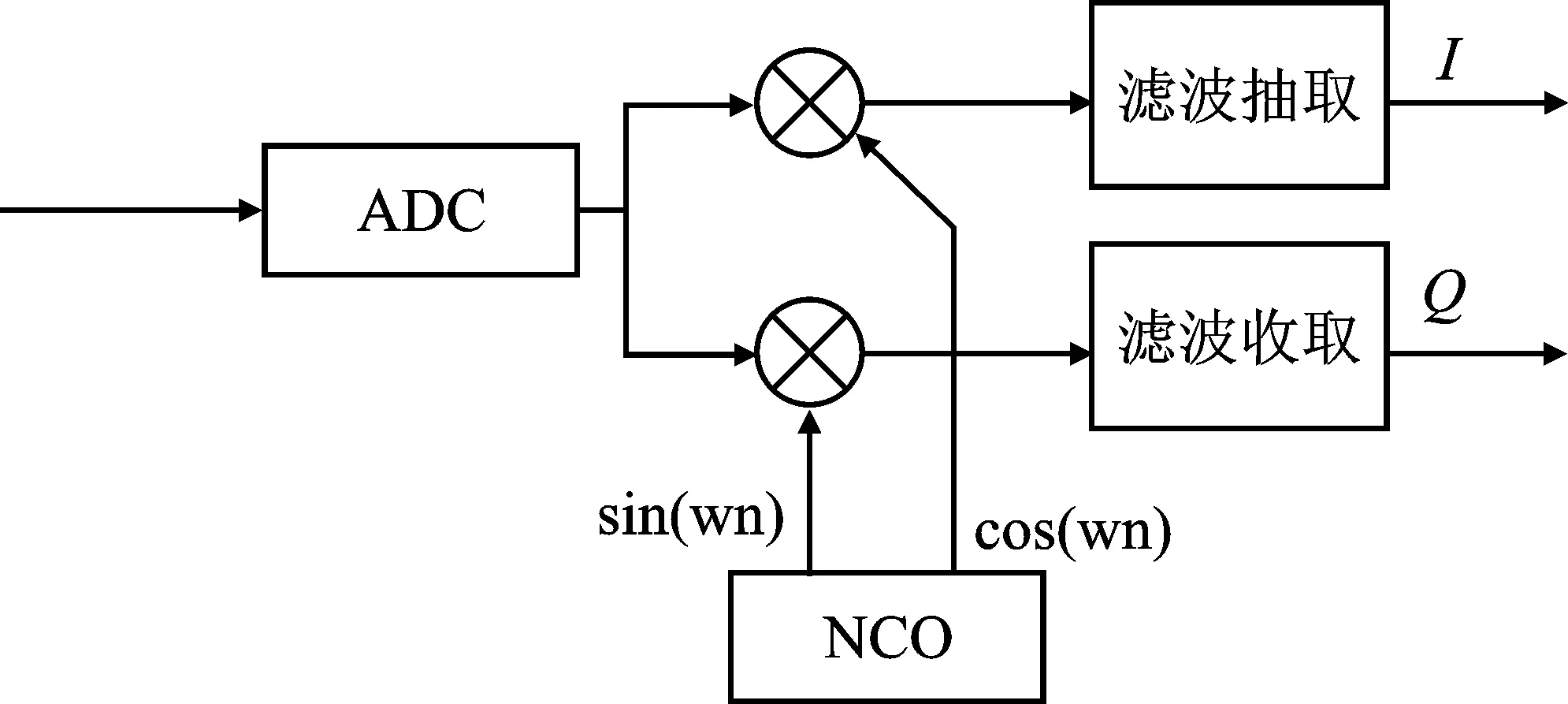

在通过FPGA完成对40路中频信号的采样时,为了减小数据量,提高后续信号处理的效率,采用DDC技术将信号频谱搬移到基带,获得40组基带I/Q信号。

DDC原理框图如图6所示,其主要由混频器、数控振荡器(Numerically Controlled Oscillator,NCO)和滤波抽取3部分组成。在FPGA中实现时,采用IP(Intellectual Property) core的设计思想,混频器通过乘法器来实现。NCO为两组系数,存储在两个数组中,其具体数值由AD采样频率和信号频率确定。滤波抽取则通过FIR(Finite Impulse Response)滤波器的IP core设计实现。抽取后的数据率为10 MHz,数据位宽为16 bit,为I/Q两路。

图6 DDC原理框图Figure 6. Schematic diagram of DDC

3.3 数字波束合成模块

在获得基带I/Q数据之后,便可进行数字波束合成(Digital Beam Forming,DBF)运算,即对天线各阵元接收信号的幅度和相位进行加权求和。DBF技术可以根据信号及环境变化形成波束,主瓣对准期望信号方向,并形成零陷去抑制不需要方向上的干扰,在提升探测性能方面具有一定的优势[18-19]。

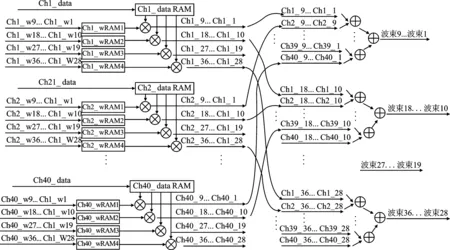

波束合成示意图如图7所示,本系统需要形成36个波束。波束合成模块接收40路基带数据和上位机下发的40组权重数据,每组包含36个数,分别缓存到相应的乒乓RAM(Random Access Memory)中。在具体实现时,36个权重被存到4个乒乓RAM中,每个权重RAM存9个数据。基带数据率为10 MHz,采用200 MHz的工作时钟,乘法器被复用9次,可节省大量计算时间和硬件资源。

图7 波束合成示意图Figure 7. Schematic diagram of beamforming

3.4 GTH高速发送模块

GTH是V7 FPGA内部的高速数据收发器硬核模块,专门用于与外部的高速数据通信。在本系统中,使用GTH接口,把光纤作为传输介质,可实现高速数据的向外传输。

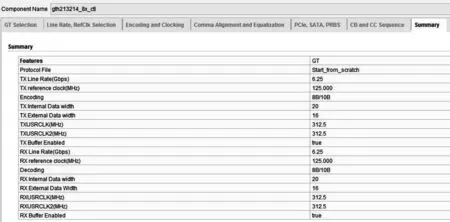

波束形成后的I/Q数据各为32位,数据率为10 MHz,则单个波束数据率为0.64 Gbit·s-1,总共36个波束,考虑8 b/10 b编码,则总数据率至少在28.8 Gbit·s-1以上。实现时,将单路的线速率设计为6.25 Gbit·s-1,使用6路这样的通道,完全满足系统需求。在FPGA中,通过配置GTH的IP core来实现,配置示意图如图8所示。

图8 IP核配置示意图Figure 8. Schematic diagram of IP core configuration

3.5 波束控制模块

系统的波束控制模块采用TTL接口与外部T/R组件相连,以实现对波束方向的控制。

在FPGA程序设计中,需完成配相计算和配相发送两大功能。在计算单元中,采用ROM(Read Only Memory)查找表的设计方法,存储频率、波位、发射初相和接收初相等相关信息,根据上位机指令发送的频率号和波位号,计算得出收发通道的配相码。同时,从上位机指令中解析得到接收衰减码及功放开关等信息。在时序信号的控制下,发送单元按照T/R组件的通信协议,分别将接收和发射的配相码及接收衰减码等信息发至T/R组件,以实现对相扫波束的控制。波束控制示意图如图9所示。

图9 波束控制示意图Figure 9. Schematic diagram of beam control

4 测试结果

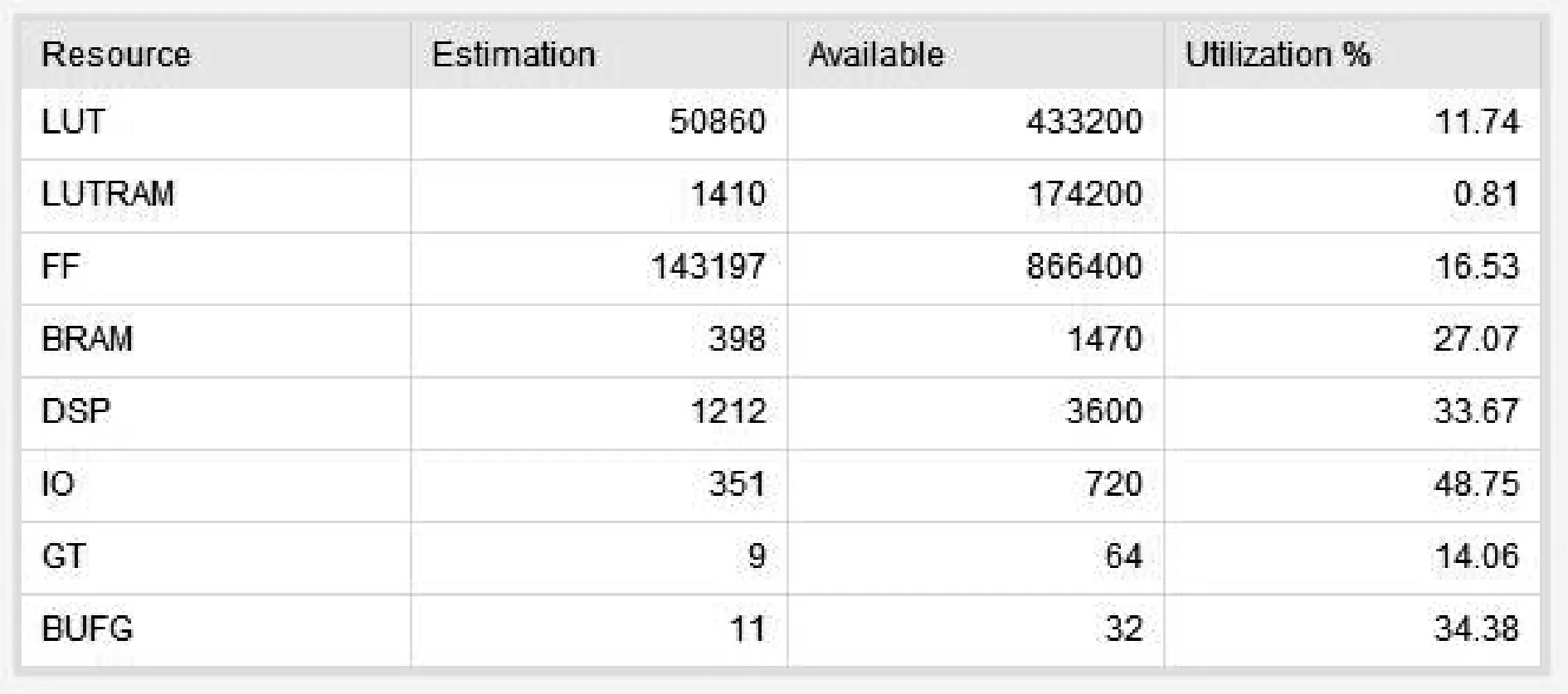

经设计实现,本系统FPGA硬件资源的占用情况如图10中所示。从图中可以看出,大部分资源的使用都在50%以下,预留部分较为宽裕,使得本系统具有一定的可扩展性。

图10 FPGA硬件资源占用情况Figure 10. Occupation of FPGA hardware resource

在雷达整机中开展试验,对本系统的部分功能模块进行测试。试验时,在射频端接入1路带偏置的正弦波信号,通过天线回路馈到各个接收通道,连接JTAG(Joint Test Action Group)调试线缆,在调试窗口中观测相关信号。

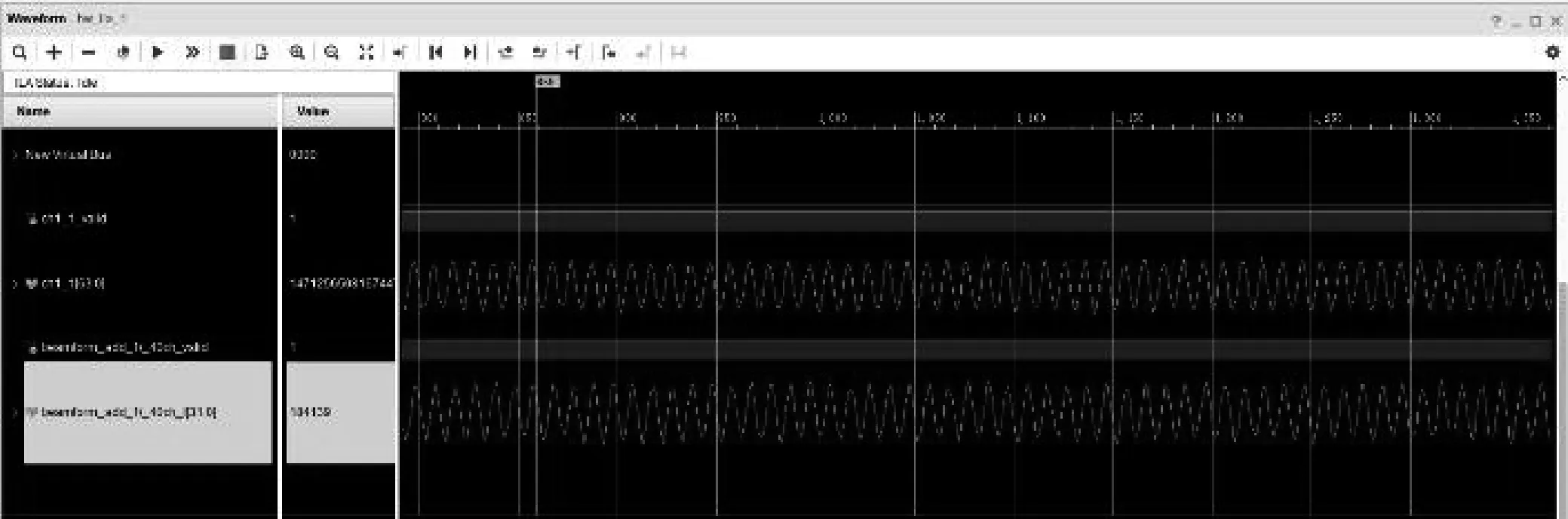

本系统部分信号的监测示意图如图11所示,包含正常工作所需要的一些时钟及复位信号。ADC采样结果和DDC之后的结果如图12所示,由于信号路数较多,而调试窗口位置有限,图中只展示了3个通道的采样信息。第1通道的采样数据为ch1_d_out_i,是一个中频正弦波,和预期结果一致。每个通道的采样数据在DDC处理之后形成I/Q两路基带数据,第1通道的基带数据为DDC_data1_i和DDC_data1_q。根据图中采样结果,对IO数据的信号频率进行计算,其数值与理论值一致,满足设计要求。

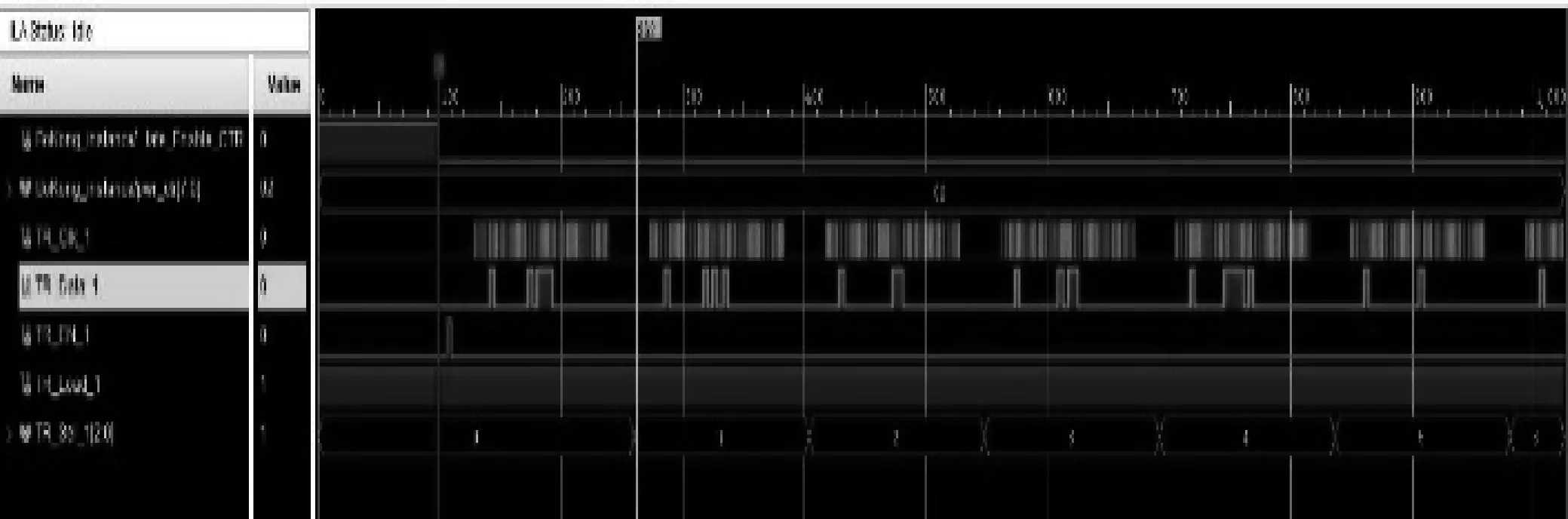

波束合成后的结果如图13所示,在第1通道的valid有效信号为高电平时,波束形成后第1通道的I路数据为40ch_I,也是一个正弦波,符合预期结果。波束控制模块发送示意图如图14所示,TR_CLK_1为通道控制时序,TR_Data_1为波控码,满足时序要求。试验表明,该系统的各个功能模块可以满足设计需求。

图11 本系统部分信号监测示意图Figure 11. Schematic diagram of partial signal monitoring in the proposed system

图12 采样与下变频示意图Figure 12. Waveforms of sampling and DDC

图13 波束合成后的波形示意图Figure 13. Waveforms of beamforming

图14 波束控制模块发送单元示意图Figure 14. Waveforms of beam control module

5 结束语

本文根据实际项目需求,设计了一种基于FPGA的多功能阵列信号处理系统。本系统具有实时的阵列信号处理能力,可完成对40个通道的数据采集,实现数字下变频和波束合成运算。同时,本系统可与多个外联设备进行互联,具有较强的通信控制和数据传输能力。本系统还可作为一种通用的信号处理控制平台,丰富的硬件资源使其具有一定的可扩展性,能直接用于其他项目的信号处理与控制系统中,具有一定的工程应用价值。