基于JESD204B协议的接收端电路设计*

2023-01-02孔玉礼陈婷婷万书芹

孔玉礼,陈婷婷,万书芹,邵 杰

(1.中国人民解放军海军七〇一工厂,北京 100000;2.中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

1 引言

随着高速率数据应用需求的不断增长,数据转换器的速率和动态范围进一步提升,串行传输成为转换器与逻辑设备之间进行数据通信的主要方式[1]。联合电子设备工程委员会参考PCIE、SRIO等串行总线传输协议的优势,制定并发布了JESD204B串行接口协议[2],可提供足够的带宽,并与转换器的高采样速率保持平衡[3]。目前,基于JESD204B协议的串行接口成为高速转换器接口电路的首选[4]。

国内对于转换器接口的研究已取得了一定的进展,但在设计应用以及指标实现方面相较于国际先进水平尚存在较大的提升空间。付东兵[5]等基于JESD204B协议设计了接收端的数据链路层电路,与赛灵思(Xilinx)的JESD204B v6.1发送端知识产权(IP)核完成了环回对接验证,但研究层次仅为电路综合阶段;袁晓伟[6]实现了接收端数字电路并成功应用于数模转换器芯片中,其单通道最高传输速率为10 Gbit/s,未能达到协议所支持的12.5 Gbit/s,且该接收端电路仅有一种链路工作模式。

本文在深入分析JESD204B协议的基础上,采用Verilog HDL语言设计了一款可适用于4通道、16 bit、2.5 GSa/S数模转换器的接口电路,并建立通用验证方法学(UVM)平台仿真验证电路功能的正确性。基于某65 nm互补金属氧化物半导体(CMOS)工艺对该接收端电路进行电路综合和版图设计,流片后的样片电路单通道最高传输速率为12.5 Gbit/s,可支持10种链路工作模式,适用于多种场合。

2 接收端电路的基本原理

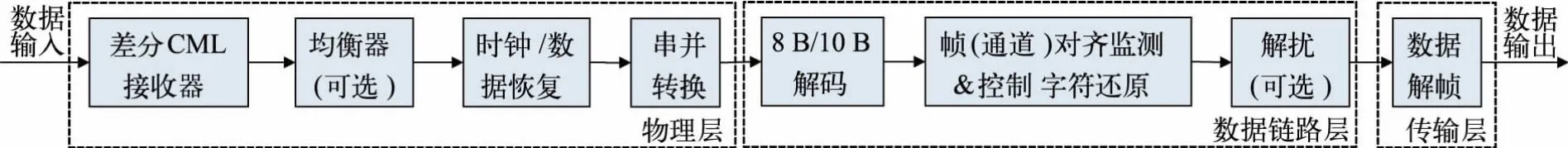

JESD204B协议分为应用层、物理层、数据链路层和传输层4个层级。首先,物理层将接收端电路接收到的数据流进行时钟/数据恢复(CDR)并反序列化;然后,将其传递到数据链路层,实现链路建立和数据处理[7];最后,经由传输层将通道上的帧数据映射为转换器采样数据输出[8],而应用层不在协议规范之内,电路的数据流向如图1所示。

图1 电路的数据流向

2.1 应用层

应用层的作用是配置接收端的链路参数,链路参数主要根据电路设计需求和内部结构进行合理选择。接收端电路采用应用层配置链路参数时,与之实现数据交互的发送端电路也需要配置与之完全相同的链路参数,从而保证传输数据的有效性。

2.2 物理层

物理层是数据进入接收端电路中经过的第一个层级,由电流模式逻辑(CML)接收器、均衡器、时钟/数据恢复和串并转换模块组成[9],采用模拟集成电路设计方法进行设计。JESD204B协议支持3种物理层规范,分别为LV-OIF-Sx15、LV-OIF-6G-SR和LV-OIF-11G-SR,目前,最常用的规范为LV-OIF-11G-SR,其最高数据传输速率可达12.5 Gbit/s,也是本文接收端电路中采用的物理层规范。

2.3 数据链路层

数据链路层主要实现发送端与接收端之间的链路建立、数据处理功能,同时接收端电路的数据链路层还需要实时监测链路的状态并做出错误统计,确保电路正常工作。

链路建立分为代码组同步(CGS)和初始通道同步(ILS)2个过程。在CGS期间,一旦接收端电路连续检测到固定数量的/K28.5/字符后将改变同步信号SYNC~信号的值,发送端检测到SYNC~信号的变化则按需求进入ILS阶段,此时收、发2端以初始通道同步序列(ILAS)完成信息交互。

链路建立完成后,接收端电路开始接收用户数据[10],进行8 B/10 B解码、控制字符还原、解扰,分别对应了发送端电路中的8 B/10 B编码、控制字符替换以及加扰的操作。此外,JESD204B协议规定了接收端能够检测系统中可能出现的错误并进行相应处理。

2.4 传输层

接收端电路传输层的作用是将通道上的帧格式数据按照链路工作模式映射为转换器原始采样数据。链路工作模式主要与参数F、L、M、S有关。F为每帧中8 B的数量,L为设备中的通道数量,M为设备中转换器的数量,S为单个转换器每个帧时钟周期的采样数量。映射过程中还要考虑转换器分辨率N和样本宽度N'的大小。

3 接收端电路设计

3.1 整体设计

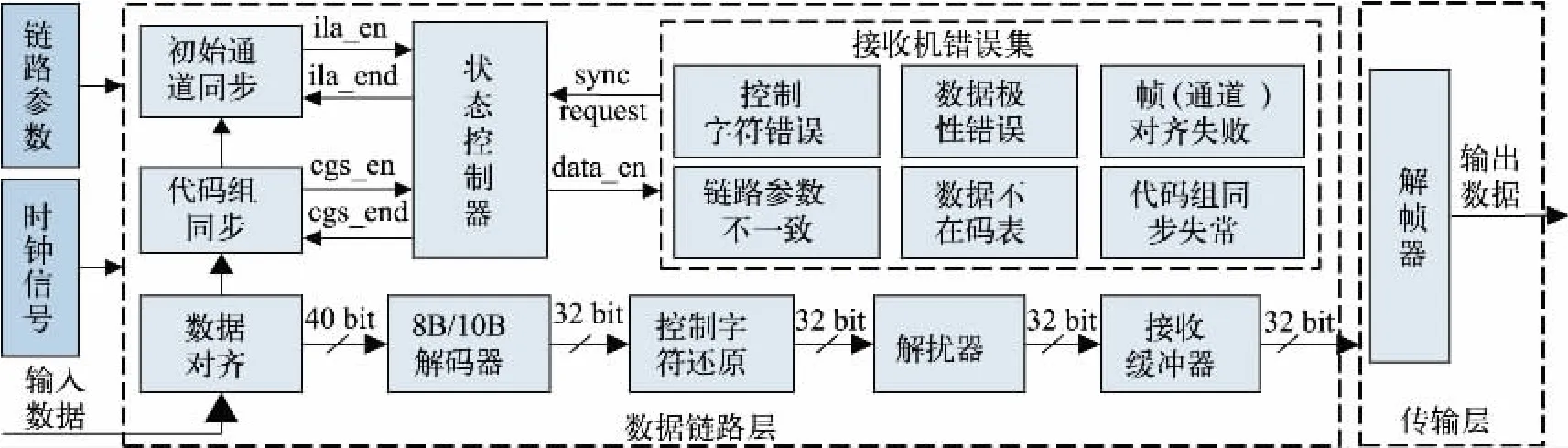

根据JESD204B协议和项目设计要求,对接收端电路功能进行详细的划分。接收端电路的整体架构如图2所示,物理层采用高精度的模拟电路实现,且应用层不属于协议规范,因此图2中主要划分的是数据链路层和传输层的各个功能模块。数据链路层功能复杂,数据先后流经数据对齐、8 B/10 B解码器、控制字符还原、解扰器、接收缓冲器电路,同时进行链路同步和错误统计,传输层电路仅包含一个解帧器模块,其输出即为接收端电路的最终输出信号。

图2 接收端电路的整体架构

JESD204B协议中所支持的单通道数据传输速率最高为12.5 Gbit/s,为了便于数字电路的处理并满足最高传输速率的要求,本设计在物理层串并转换电路中,将串行输入的数据转换成40 bit的并行数据输出,降低了数字电路的工作频率。在数据链路层和传输层,本设计以4路并行的方式处理接收到的40 bit数据,每路处理10 bit数据,降低了电路的设计复杂度。

3.2 应用层设计

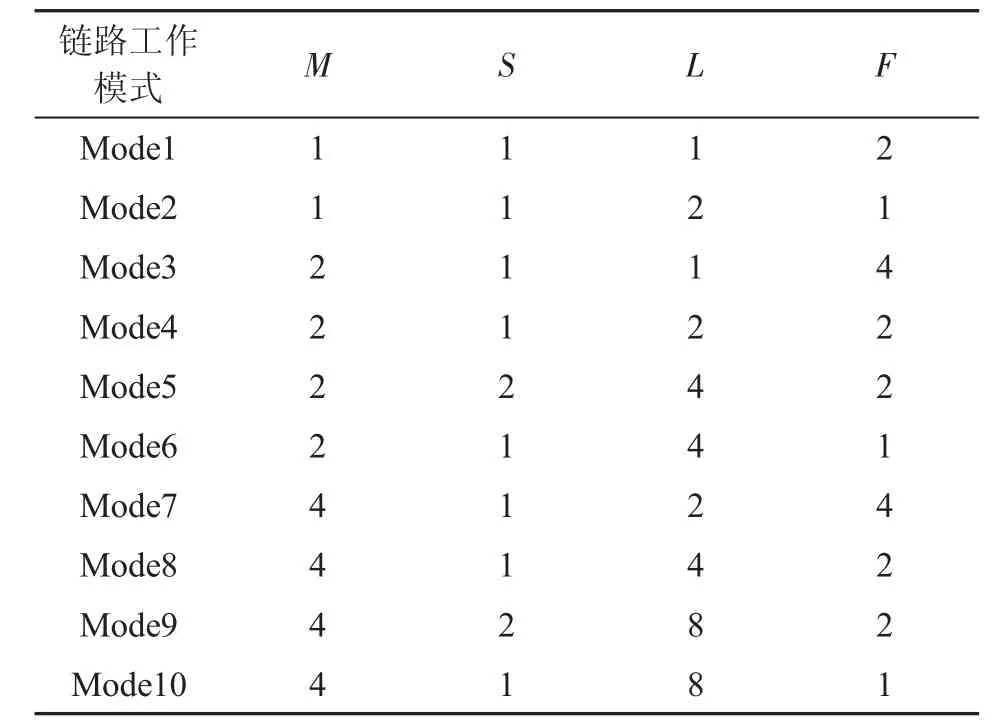

对于决定链路工作模式的参数,JESD204B协议给出了宽泛的范围。考虑到芯片的面积和功耗,选择合适的链路参数组合极为重要。由于接收端电路最终作为4通道、16 bit数模转化器接口电路,设备中包含的转换器数量不超过4个,转换器的分辨率N以及样本宽度N'取16。为了减少接收端电路与转换器模拟电路之间的串扰,每个转换器每帧发送的样本数S取整数,从而确定了链路中的通道数L,L的取值满足式(1),其中fFC为帧时钟的频率。根据已知参数M、S、N'和L,确定F的取值,见式(2)。最终,接收端电路确定了Mode1至Mode10共10种链路工作模式,链路工作模式如表1所示。

表1 链路工作模式

3.3 数据链路层设计

3.3.1 链路同步

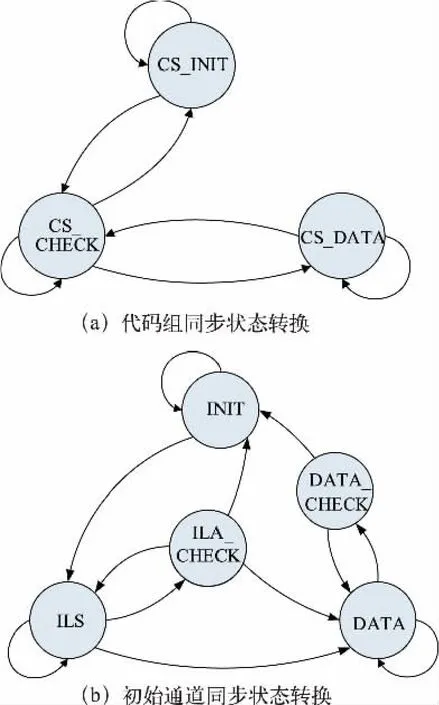

为了便于代码设计与维护,采用状态机实现链路同步模块中的代码组同步和初始通道同步。图3(a)为代码组同步状态转换图,代码组同步由3个状态构成。在CS_INIT状态下,当电路检测到4个连续的控制字符/K28.5/时,电路进入CS_CHECK状态。在CS_CHECK状态下,对8 B/10 B解码器产生的错误进行计数,若错误字节累计的数量超过3,则回到CS_INIT状态;若解码器解码结果完全正确,则跳转到CS_DATA状态。在CS_DATA状态下,只要检测到错误,状态机跳转回CS_CHECK状态。

图3(b)为初始通道同步状态转换图,初始通道同步由5个状态组成。接收端电路接收到第一个非/K28.5/字符,状态机从INIT进入ILS,此时收、发2端通过ILAS进行交互。通过计数器对ILAS中的多帧数量进行计数,当计数到4个多帧且接收到控制字符/K28.3/时,表明初始通道同步完成,开始接收用户数据。初始通道处于ILS或DATA状态时,若接收到控制字符/K28.5/,则会返回到DATA_CHECK甚至是INIT状态。

图3 链路同步模块状态转换

3.3.2 数据处理

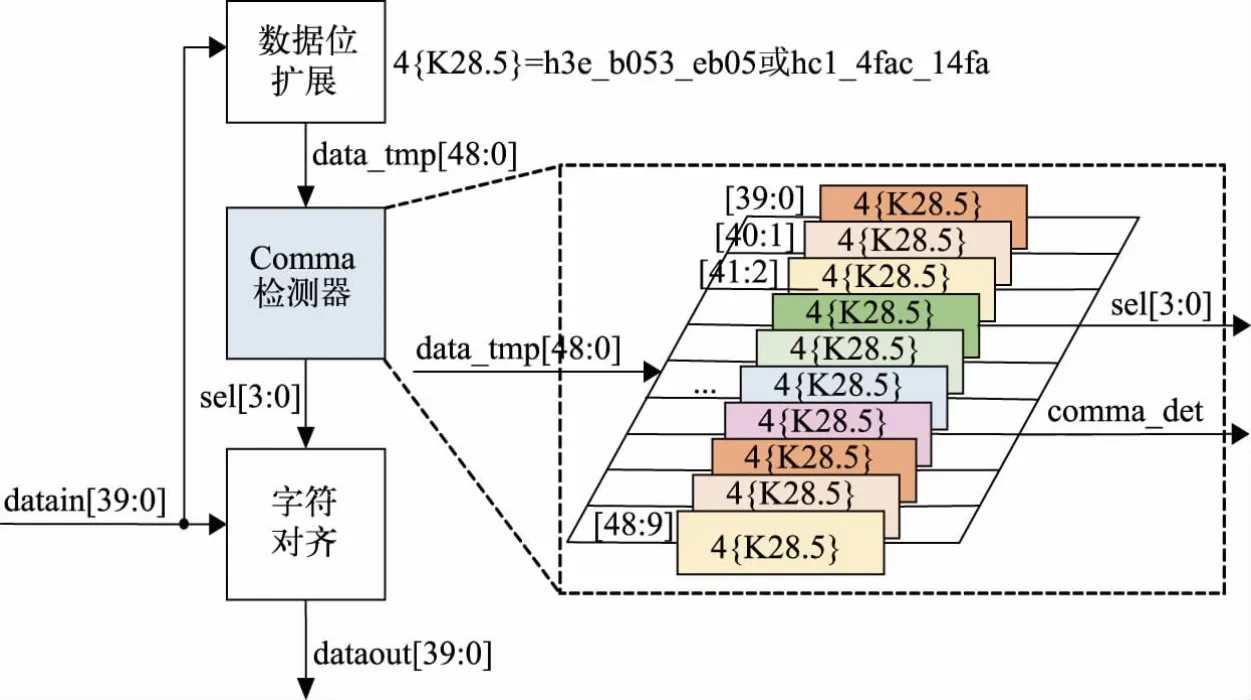

物理层输出的数据流到达数据链路层后,采用常见的异步FIFO电路消解物理层与数据链路层之间的时序差异,进入数据对齐电路,确定字符的边界。数据对齐电路如图4所示。

图4 数据对齐电路示意图

输入数据datain[39:0]首先进行数据位扩展,组合当前数据与上一个时钟周期数据的低9位,得到扩展后的数据data_tmp[48:0],接着数据进入Comma检测器,从最低位起依次取连续的40位字符与预期字符(40’h3e_b053_eb05或40’hc1_4fac_14fa)比较,得到字符的偏移量sel[3:0]及连续4个/K/字符的已检测标志comma_det,最终按照偏移量的值选择扩展后的数据输出。

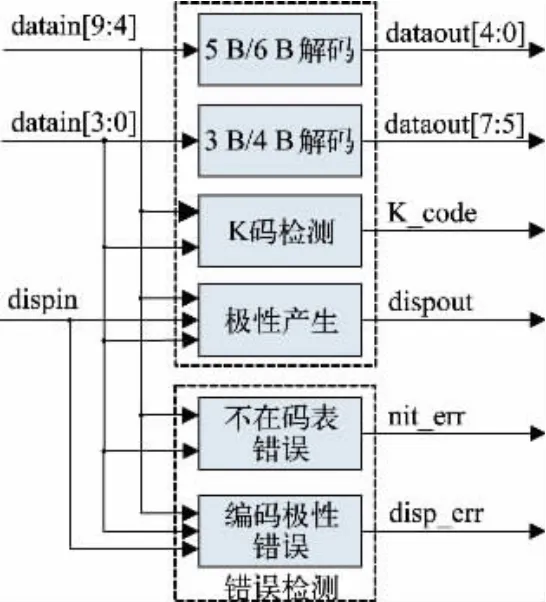

完成数据对齐后,采用4个并行的8 B/10 B解码器将40 bit数据解码为32 bit的数据,8 B/10 B解码原理如图5所示。对每个周期10 bit的数据进行5 B/6 B解码和3 B/4 B解码,并通过K码检测模块判断输入数据是否为控制字符,同时结合K码检测的输出K_code和极性产生的输出dispout,检测编码数据不在码表错误nit_err和编码极性错误disp_err,推导逻辑运算表达式表示解码结果及错误检测结果dataout[7:0]。

图5 8 B/10 B解码原理

解码完成的数据进入控制字符还原电路中,将电路是否启用加扰作为前提条件。如启用,则将检测到的控制字符/K28.3/替换为数据0X7C,/K28.7/替换为0XFC,反之,则直接将控制字符/K28.3/或/K28.7/替换为前一帧的帧尾。

解扰电路采用32 bit并行解扰的方式进行设计。在电路启用加扰功能时,由于ILAS中包含了用于链路参数校验的链路信息以及用于通道对齐的控制字符,因此,还需从链路同步模块中引入数据使能信号,接收端开始接收用户数据时方可解扰。加扰电路的具体实现方式参见文献[11]。

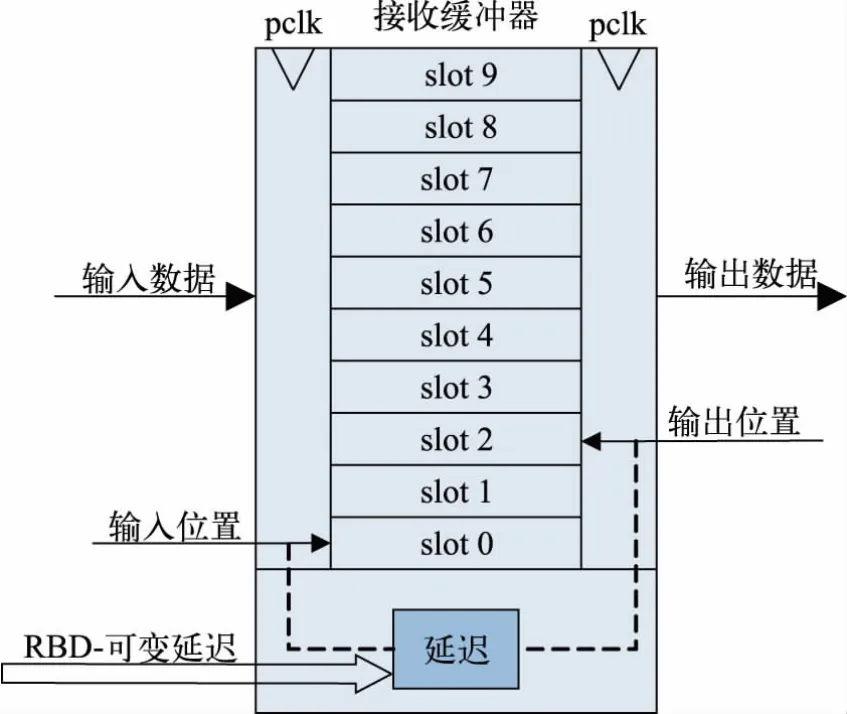

系统每次上电或是同步之后每个通道产生的可变延迟都是不同的,在JESD204B协议中加入了子类1和子类2工作模式,实现系统的确定性延迟功能。本文设计的接收端电路支持JESD204B协议所述的子类1工作模式,通过接收缓冲器缓冲数据,在以SYSREF为基准的本地多帧时钟边沿后的固定时刻释放数据,保证各通道数据对齐的同时系统的延迟不变。接收缓冲器如图6所示。

图6 接收缓冲器

接收缓冲器由10个位宽为32 bit的存储单元构成,数据从最底端的存储单元进入。每经过一个并行时钟(pclk)周期,当前存储单元中的数据进入下一个存储单元,新的数据进入当前存储单元。输出数据的位置由接收缓冲延迟(RBD)以及链路中的可变延迟决定,可变延迟等于理想情况下接收到数据的时刻与实际电路接收到数据的时刻之间的差值。

3.3.3 错误统计

本文设计的接收端电路能够检测到的错误包括控制字符错误、链路参数不一致、数据极性错误、数据不在码表、帧(通道)对齐失败以及代码组同步失常,上述错误的检测在数据处理模块电路中实现。

控制字符错误的检测在控制字符还原电路中实现,数据极性错误、数据不在码表的检测在8 B/10 B解码电路中实现。通过SPI寄存器配置错误阈值,当上述错误信号的累计数量超出设定阈值时,接、收端电路发起同步请求。

链路参数校验电路将发送端的链路参数信息缓存到寄存器中,再与接收端的链路信息进行比较,确认是否完全相等,帧(通道)对齐监测则通过计数器对帧/多帧中字节的位置进行计数,从而判断2次出现控制字符的位置是否一致,代码组同步状态机的状态回到初始状态说明代码组同步失常。因此,若电路出现链路参数校验不一致、帧(通道)对齐失败和代码组同步失常3种错误,不需要进行错误统计,接收端电路直接发起同步请求。

3.4 传输层设计

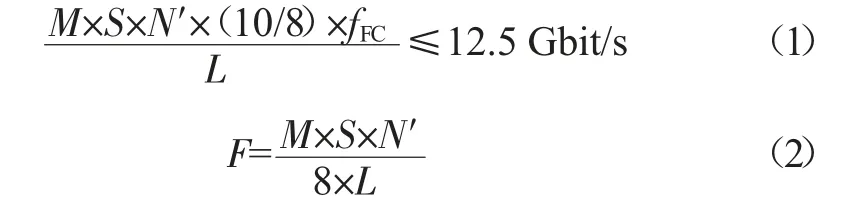

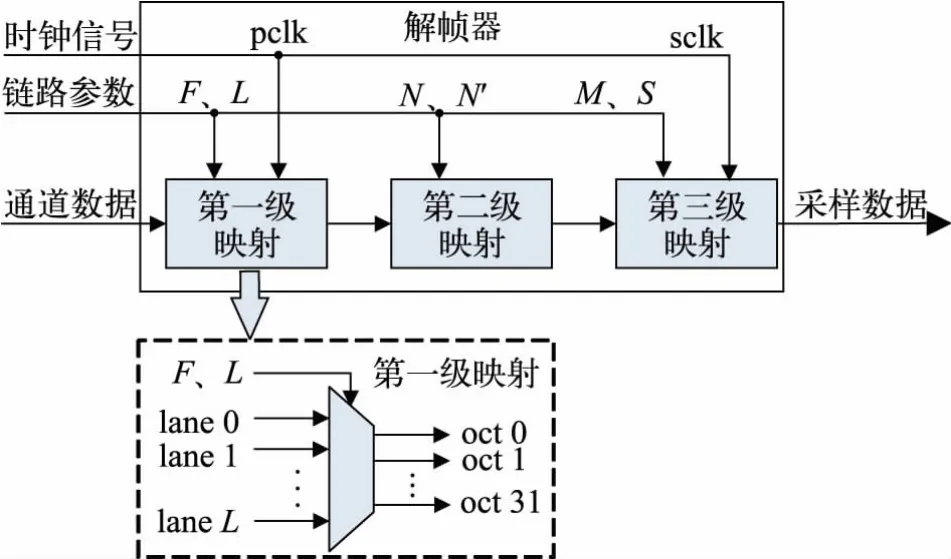

接收端电路集成了10种链路工作模式,本文采用3级映射结构将通道上的帧格式数据映射为转换器的采样数据,设计前归纳每一级映射过程中所需要的链路参数配置共通点,并在数据映射过程中满足通道的填充能力。传输层映射架构如图7所示。

图7 传输层映射架构

第一级映射以链路参数F和L为映射条件,将通道上的数据映射为32个字节。通道上每个pclk周期映射4L个字节,4与L的乘积等于32时,32个字节并行输出;4与L的乘积小于32时,则在通道上连续取32/(4×L)个时钟周期的字节,作为32个并行输出的字节。

第二级映射的本质是数据拼接,将第一级映射输出的字节拼接为样本数据。N=N'=16时,直接将32个并行字节拼接为16个样本数据。字节标号为偶数的作为样本数据的高8 bit,字节标号为奇数则作为样本数据的低8 bit。

第三级映射方式与第一级映射类似,区别在于第三级采用链路参数M和S作为映射条件,完成16个样本数据的映射。映射时用转换器时钟(sclk)对样本数据进行采样,每个时钟周期采样得到M×S个数据,经过16/(M×S)个时钟周期将样本数据完全映射到转换器中。

4 仿真与实现

4.1 UVM仿真

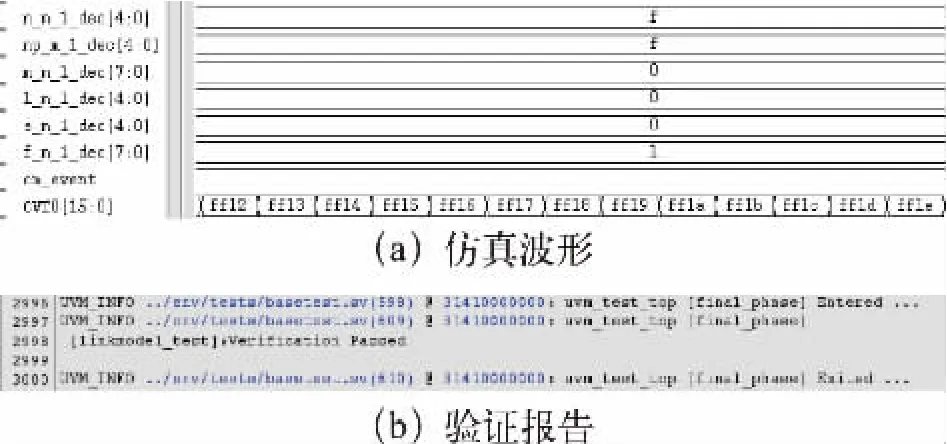

搭建UVM验证平台对设计的接收端电路进行系统级仿真验证,通过Verdi查看仿真波形和报告信息。模式1的仿真结果如图8所示。

图8 模式1仿真结果

图8(a)为电路工作在链路模式1时的仿真波形图,此时N=N'=16,M、S、F、L的取值分别为1、1、2、1,M的取值为1,表明只有一个转换器处于工作状态,因此输出信号CVT0有值且为连续递增的数值,与UVM验证平台给出的激励相同。图8(b)为当前模式下的验证报告信息,通过计分板比较信号CVT0的输出与输入的激励,信息栏输出Verification Passed字样,表明该模式下电路能够正常工作。

4.2 电路实现

使用Synopsys公司的核心工具Design Compiler,基于某65 nm CMOS工艺库,对设计的接收端电路进行逻辑综合。综合结果表明,在典型操作环境下该接收端电路可工作在312.5 MHz下,能够达到协议支持的12.5 Gbit/s的单通道数据传输速率,此时电路占用逻辑资源面积为152444.88μm2,总功耗为69.29 mW。在此基础上,对集成数模转换器芯片的数字上变频电路、SPI配置电路进行版图设计与优化,最终的数模转换器的数字电路版图尺寸约为4125μm×916μm。

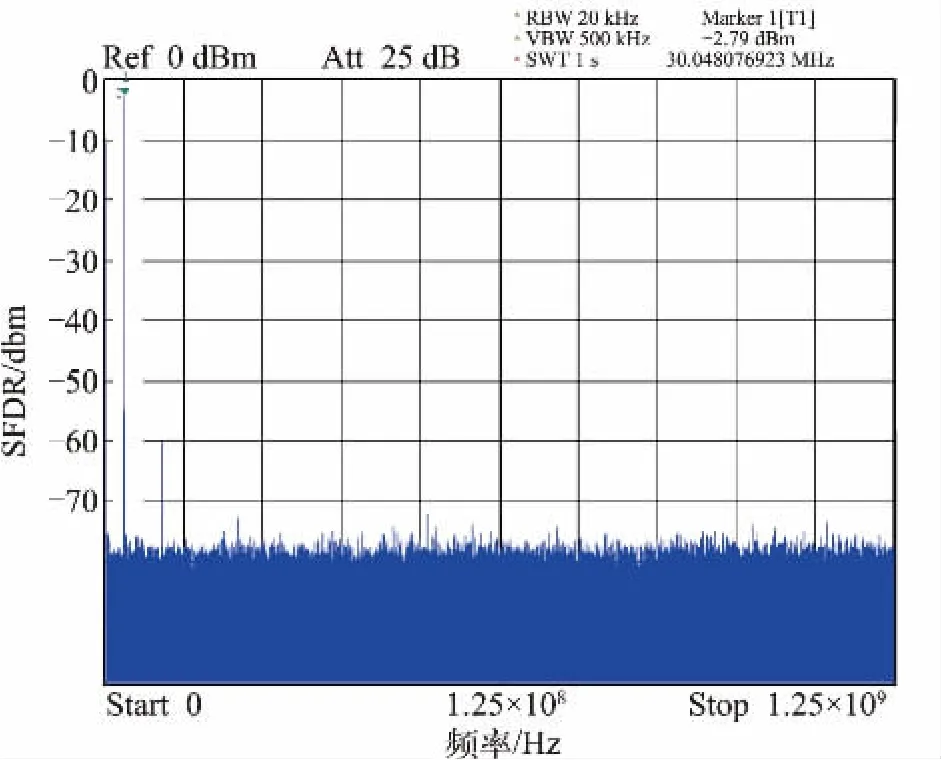

对流片封装后的数模转换器样片进行板级测试。通过上位机配置数模转换器工作于2倍插值下,JESD204B接收端接口电路选用链路模式6,单通道串行传输速率为12.5 Gbit/s,图9所示为上述配置下输出信号的频域特性。由图9可知,此时输出频率为30 MHz,测试带宽为1.25 GHz,无杂散动态范围(SFDR)测试值达到57.21 dBm。多次调整转换器样片参数,测试结果表明,本文设计的接收端电路满足预期要求。

图9 1.25 GHz输入下输出信号频域特性

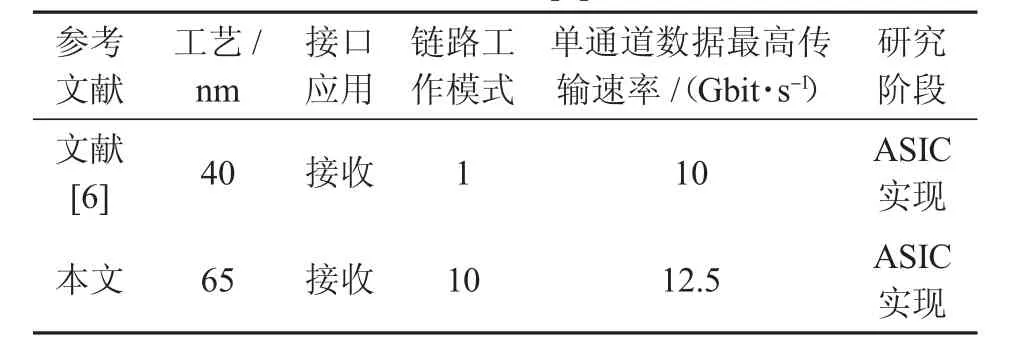

本文的接收端电路是基于特定应用需求的数模转换器而设计,与文献[6]的接口应用以及研究阶段相同。与文献[6]相比,本文设计的应用于数模转换器芯片中的JESD204B高速接口在链路工作模式和数据传输速率上具有优势,主要对比结果见表2。

表2 本设计与文献[6]的研究对比

5 结论

本文深入研究与分析了JESD204B协议的工作原理,对接收端电路功能进行了精确的划分。制定接收端的整体设计方案后,确定了应用层10种链路的工作模式;采用Verilog HDL语言实现数据链路层和传输层的RTL代码设计,搭建UVM验证平台进行系统级验证。基于某65 nm CMOS工艺进行逻辑综合和版图设计,并将设计的接收端电路应用于DAC芯片并流片,经测试该接口的单通道数据传输速率最高可达12.5 Gbit/s。