聚合物热解法制备高击穿场强CaCu3Ti4O12陶瓷的微观结构及介电性能

2022-12-27卢文敏张建花郭斯琪宋建成雷志鹏

卢文敏,张建花,郭斯琪,郝 嵘,宋建成,雷志鹏

(太原理工大学a. 电气与动力工程学院;b. 矿电气设备与智能控制山西省重点实验室;c. 矿用智能电器技术国家地方联合工程实验室,山西 太原 030024)

0 引言

2000年,M A SUBRAMANIAN 等[1]首次报道了CaCu3Ti4O12(CCTO)陶瓷,后来许多研究者发现该陶瓷材料具有高介电常数(ε)(>10 000),并在100~300 K 内表现出良好的温度稳定性[2],引起国内外研究人员的极大兴趣。CCTO 陶瓷还表现出非欧姆特性,使得这些陶瓷有望用于储能电容器和过压保护装置等应用[3]。电容器中储能密度(ω)的计算公式如式(1)所示[4]。

式(1)中:Eb为击穿场强;ε0和εr分别为真空介电常数和相对介电常数[5]。

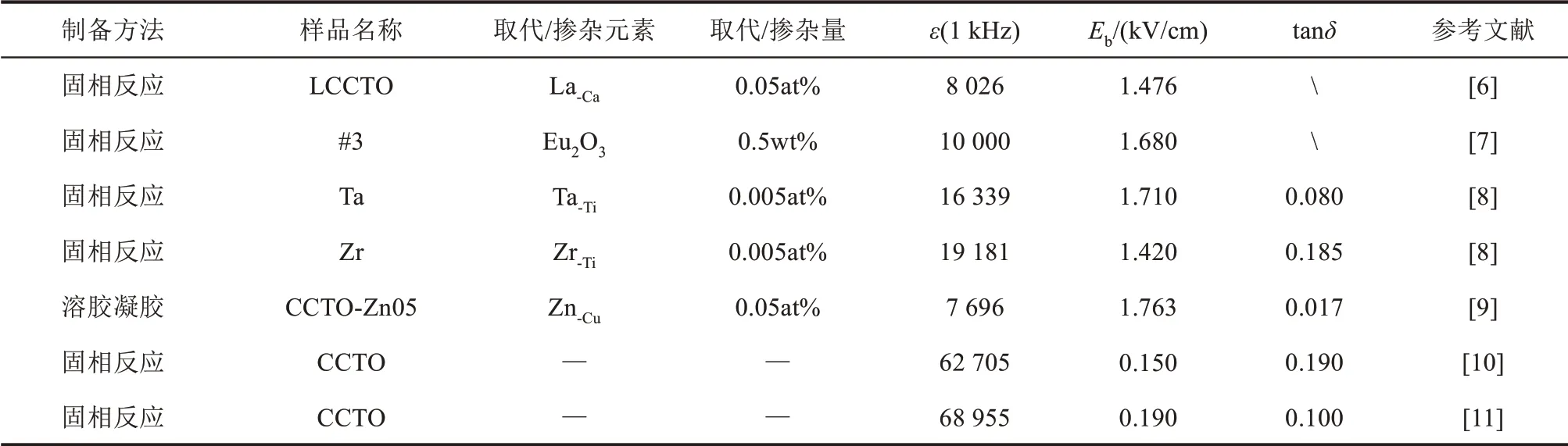

由式(1)可知,电容器的储能密度由介电常数ε和击穿场强(Eb)决定,且Eb对其影响更显著。通常制备的CCTO 具有较高的ε和较好的温度稳定性,然而,由于其Eb一般低于2 kV/cm,储能密度较小,限制了其在实际中的应用。表1 总结了CCTO 样品的Eb、ε和介质损耗因数(tanδ)。

表1 室温下CCTO陶瓷的制备方法和介电性能Tab.1 Preparation method and dielectric properties of CCTO ceramics at room temperature

通过了解CCTO 介电陶瓷Eb的研究进展,发现CCTO陶瓷较大的晶粒尺寸有利于提高ε,而较小的晶粒尺寸有利于改善Eb[5,12]。说明Eb的提高是以牺牲ε为代价,也就是说ε和Eb是两个不可同时优化的参数。由于低频tanδ的降低和Eb的提高都与晶界处的电性能相关[13],研究发现聚合物热解法可以很好地改善CCTO 的介电性能[14],而且制备陶瓷样品时的烧结温度对样品的微观结构和介电性能影响也很大。因此本研究选用聚合物热解法制备CCTO粉体,然后在不同温度下进行烧结得到CCTO 陶瓷样品,研究不同烧结温度对其微观结构和介电性能的影响。

1 实验

1.1 实验方法

用聚合物热解法制备CCTO粉体,以硝酸铜、硝酸钙、二钛酸二异丙酯为原料,丙烯酸水溶液作为聚合单体,过硫酸铵水溶液作为引发剂。首先,将二钛酸二异丙酯溶解在室温下恒定搅拌的丙烯酸水溶液中,再将硝酸钙和硝酸铜溶解在上述溶液中,直至获得澄清的溶液;随后加入5%的过硫酸铵水溶液,在80℃下加热搅拌2.5 h获得CCTO 凝胶前体。将凝胶前体置于90℃下保温5 h,最后在850℃下烧结4 h 获得CCTO 粉体。将CCTO 前驱体粉体在25 MPa下压制成直径为24 mm、厚度为15 mm的坯体,最后分别在1 040、1 060、1 080℃下烧结10 h,制成陶瓷样品。

1.2 表征

用X 射线衍射仪(XRD)表征样品在2θ范围为20°~80°的物相组成和晶体结构。采用扫描电子显微镜(SEM)观测样品的微观结构。在介电测量之前,首先将CCTO 样品的两个表面都抛光并涂敷银浆作为电容器电极,然后使用宽频介电和阻抗谱分析仪测试陶瓷样品的介电特性和阻抗,最后使用高压测量设备(Keithley 6517B 型)在室温下测量非线性DC电流密度-电场强度(J-E)特性。

2 结果与讨论

2.1 相结构和组成

为了研究不同烧结温度对CCTO陶瓷相结构的影响,分析了所有陶瓷样品的XRD图。不同烧结温度陶瓷样品的XRD 图谱如图1 所示,根据CCTO 标准PDF数据库(JCPDS文件编号75-2188),CCTO 样品的主要衍射峰均为空间群为Im3的纯立方钙钛矿相关结构[15]。由图1 可知,大部分样品中没有检测到任何杂相,可能是含量太少超出了XRD的检测极限。1040℃样品中存在TiO2杂相,可能是聚合反应不充分导致。通过MDI JADE软件计算了样品的晶格参数(a),均与标准CCTO 的晶格参数(7.391Å)相近。

图1 不同烧结温度CCTO陶瓷样品的X射线衍射图谱Fig.1 X-ray diffraction pattern of CCTO ceramic samples at different sintering temperatures

2.2 微观形貌

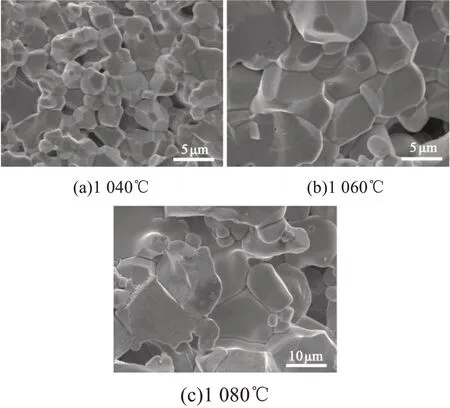

不同烧结温度CCTO 陶瓷的SEM 图像如图2所示。由图2 可知,CCTO 陶瓷样品的晶粒尺寸随着烧结温度的升高而增大,表明烧结条件对陶瓷样品的微观结构影响显著。用Nano Measurer 软件计算的晶粒尺寸结果和SEM 图的结果相符,1 040、1 060、1 080℃陶瓷样品的平均晶粒尺寸分别约为3.56、6.42、13.02 μm。其中1 060℃样品显示出正常的晶粒生长状态,晶粒均匀且致密。1 040℃样品晶粒尺寸较小,晶粒极不均匀,说明过低的烧结温度不利于晶粒充分生长。1 080℃样品表现出晶粒异常生长,孔洞较多,另外部分晶粒出现明显的熔融现象。结合XRD 的分析结果可知,1 040℃样品中有TiO2杂相,TiO2杂相在最终烧制成型的过程中会消耗富Cu 相,而晶界处CuO 在成相过程中会融为液相,有利于晶粒的生长[16-17],这可能是1 040℃样品晶粒尺寸较小的另一个原因。

图2 1 040、1 060、1 080℃烧结陶瓷样品的SEM图像Fig.2 SEM images of sintered ceramic samples at 1 040,1 060,1 080℃

2.3 复阻抗谱分析

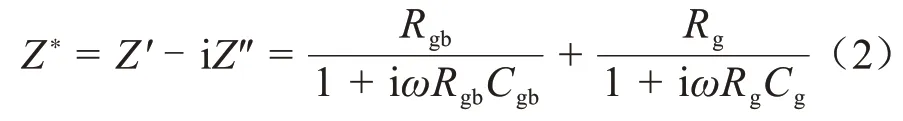

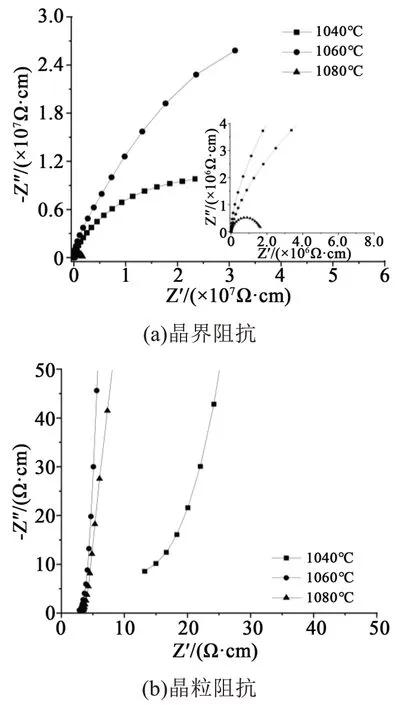

对所有样品进行复阻抗谱分析以进一步研究电异质微结构对CCTO陶瓷介电性能的影响。本实验CCTO 陶瓷样品的介电响应符合德拜响应模型,因此可使用阻抗谱圆弧拟合进行等效电路分析。根据IBLC 模型,两个并联的电阻-电容(R-C)的串联电路是解释CCTO陶瓷中晶粒和晶界异质性的有效方法[18-20]。复阻抗Z∗可以通过公式(2)[20]计算。

式(2)中:Rg和Cg分别代表晶粒电阻和晶粒电容;Rgb和Cgb代表晶界电阻和晶界电容;ω为角频率。一般情况下,由于晶粒和晶界之间存在较大的电不均匀性,晶粒阻抗半圆弧在高频下几乎不可见,而另一个则由于测试频率范围的限制而仅显示出部分阻抗半圆弧。因此,通常可以从阻抗谱的半圆弧直径估算Rgb,从Z轴的非零截距估算Rg。

图3为不同烧结温度陶瓷样品的阻抗谱图。从图3 中复阻抗的实部和虚部可得CCTO 样品的阻抗谱,可以观察到,CCTO 陶瓷的Rgb随着烧结温度的升高先增大后减小,说明适当的烧结温度可完善晶界的形成,而过高的烧结温度会导致晶界不稳定。1 060 和1 080℃陶瓷样品的Rg几乎相同,1 040℃样品的Rg较大,使其电介质极化较弱。

图3 不同烧结温度陶瓷样品的阻抗谱图Fig.3 Impedance spectra of ceramic samples with different sintering temperatures

2.4 势垒高度

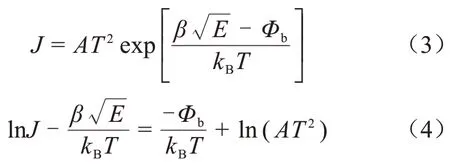

使用理查森-肖特基模型可以计算所有样品的势垒高度(Φb),热电子发射电流密度(J)与E的关系式如式(3)~(4)所示。

当lnJ-= lnJ0,得到式(5)。

式(3)~(5)中:A是理查森常数;Φb为势垒高度;β为前置因子;kB为玻尔兹曼常数;T为绝对温度。

图4 为室温下CCTO 样品的lnJ与E1/2关系图,可以观察到所有样品的lnJ与E1/2明显呈现的线性关系。通过图4 的线性关系计算出陶瓷样品的Φb,得到1 040、1 060、1 080℃样品的Φb分别约为0.95、1.12、0.67 eV,在没有直流(DC)偏置的情况下,Φb可以表示为式(6)[21]。

图4 室温下不同烧结温度陶瓷样品lnJ与E1/2的关系Fig.4 The relationship between lnJ and E1/2 of ceramic samples with different sintering temperatures at room temperature

式(6)中:εr是材料的相对介电常数;q是电子电荷;Ns和Nd分别是n型半导体晶粒中的表面电荷和电荷载体浓度。陶瓷样品的Φb随着烧结温度的升高先增大后减小,1 040℃样品的Φb小于1 060℃样品,表明过低的烧结温度不利于势垒形成。

2.5 活化能

Arrhenius方程[22]如式(7)所示。

式(6)中:σg和σgb分别是晶粒和晶界电导率;σ0是指前因子;Eg和Egb分别是晶粒和晶界活化能。

根据式(7)对lnσg/lnσgb与1 000/T进行拟合,结果如图5所示。

图5 晶粒和晶界抗阻抗的Arrhenius图Fig.5 Arrhenius plots of the grain and grain boundary resistance data

从图5 可以看出,CCTO 陶瓷的lnσg/lnσgb值与1 000/T具有良好的线性关系,说明在外电场作用下的电子传输遵循热发射模型[23]。通过图5 中拟合直线的斜率可以得到烧结温度为1 040、1 060、1 080℃的CCTO 陶瓷的Eg分别为0.10、0.08 和0.09 eV,Egb分别为0.54、0.87和0.51 eV。

2.6 介电性能

CCTO 陶瓷样品在室温下的压敏电阻非线性(J-E)特性如图6所示,当电流密度J=1 mA/cm2时,获得击穿场强(Eb)值。从图6 可以看出,在所有样品中都可以发现非线性行为,1 040、1 060、1 080℃样品的Eb分别约为8.06、11.45、0.47 kV/cm,这比先前报道的氧化物法制备的纯CCTO 陶瓷的Eb高近1个数量级[14,24]。文献[25]研究表明,CCTO 陶瓷的晶粒尺寸越小,Eb越高,结合SEM 结果发现,1 040℃和1 060℃样品的Eb较大,这主要是由于晶粒尺寸的减小。众所周知,CCTO 陶瓷Eb的增加不仅与其晶粒大小有关,还与J-E特性的起源与肖特基势垒高度有关,通过图4 和图5 可知1 060℃样品的Eb大于1 040℃样品主要是由于其较大的势垒高度引起的。此外,陶瓷样品的Eb与晶界电阻(Rgb)密切相关,因此过低和过高的烧结温度制备的CCTO陶瓷样品压敏性能较差。

图6 不同烧结温度陶瓷样品的非线性电气特性(J-E)Fig.6 The nonlinear electrical characteristics(J-E)of ceramic samples with different sintering temperatures

图7为不同烧结温度样品的ε频谱,大多数研究者发现较低的烧结温度有利于Eb的提高,但不利于ε的增大,且一般ε随晶粒尺寸的增大而增大。结合图2 和图7 发现本实验也恰好证明了此观点,这主要与烧结温度对晶粒尺寸的影响相关。1 040、1 060、1 080℃样品在1 kHz 时的ε值分别为2 281、9 110 和24 743。根据内层阻挡层电容器(IBLC)模型,大晶粒的CCTO陶瓷可以产生明显的电异质性,从而引起巨大的介电响应[26]。本研究中1 080℃样品的ε约为1 040℃样品的10 倍,这是由于温度过高、晶粒异常生长造成的。1 040℃样品与1 060℃样品在102~106Hz 内的频率稳定性比1 080℃样品更好,因此适合的烧结温度更利于得到具有高ε和良好频率稳定性的陶瓷样品。

图7 不同烧结温度陶瓷样品ε的频率相关性Fig.7 Frequency correlation of ε for ceramic samples with different sintering temperatures

通常,商业应用的高性能电介质tanδ值应低于0.05,因此tanδ也是CCTO 陶瓷材料的另一重要介电参数。不同烧结温度陶瓷样品的tanδ频谱如图8所示。从图8 可以看出,1 040、1 060、1 080℃样品的tanδ最小值分别为0.09、0.03、0.10,显然1 060℃样品的tanδ符合要求。CCTO 陶瓷的高tanδ值通常出现在低频和高频范围内[12],这分别与高直流电导率和介电弛豫现象有关[27]。结合图3和5可以发现,1 060℃陶瓷的低频tanδ明显降低与其Rgb和Egb的显著增强有关,较大的Rgb和Egb改善了1 060℃陶瓷的晶界介电特性。较大的低频tanδ值不适合实际应用,而本实验采用聚合物热解法在1 060℃下烧结制备的CCTO样品低频tanδ很低。因此聚合物热解法制备陶瓷样品的最佳烧结温度为1 060℃。

图8 不同烧结温度陶瓷样品tanδ的频率相关性Fig.8 Frequency correlation of tanδ for ceramic samples with different sintering temperatures

3 结论

(1)本实验采用聚合物热解法在1 060℃下烧结制备的CCTO 样品Eb值约为11.45 kV/cm,比固相反应法制备的样品Eb值大1个数量级,在室温下ε和tanδ分别约为9 110和0.03。

(2)CCTO 陶瓷样品的微观结构变化受烧结温度的影响显著,晶粒尺寸随着烧结温度的升高而增大,烧结温度较低不利于晶界的完善和势垒的形成,而烧结温度过高使得晶粒生长过快,晶粒大小极不均匀。

(3)适合的烧结温度使得晶粒均匀长大,有利于陶瓷样品ε的提高和频率稳定性的改善。此外,适合的烧结温度还可以增大陶瓷样品的Rgb,进而使得陶瓷样品的tanδ降低和Eb提高。