高速通信平台的国产化设计及测试

2022-11-22薛伟钊张会新郭瑞卿

薛伟钊,张会新,郭瑞卿,白 嘉,严 帅,郭 冲

(1.中北大学仪器与电子学院,山西太原 030051;2.西安电子科技大学电子工程学院,陕西西安 710071;3.北京宇航系统工程研究所,北京 100076)

0 引言

在国防、航天等领域发展的过程中,相关设备的国产化非常重要[1]。其核心处理器多为国外生产的FPGA(field programmable gate array),即现场可编程逻辑门阵列等芯片[2]。现在,国产芯片的性能有了显著的提高,开始应用到自主可控的模块和设备中[3]。由于图像等信息数据量较大,对高速传输方式提出了巨大挑战[4],传统方式是使用并行传输,但是该方式随着信号线数量增多、距离增长,串扰的问题越来越突出,高速串行数据传输的方式正在取代并行传输的方式[5]。光纤通信的传输效率较高,传输损耗最低,而高速串行通信要达到长距离传输,与光纤通信技术相结合是目前效果最好,应用最广泛的方式[6]。

1 总体方案设计

平台总体设计分为2部分,图1为单板自回环测试平台框图,由上位机、高速数据收发模块以及差分线组成。该部分主要是用来测试该平台的单板功能是否完整,是否达到使用的要求。

图1 单板自回环测试设计框图

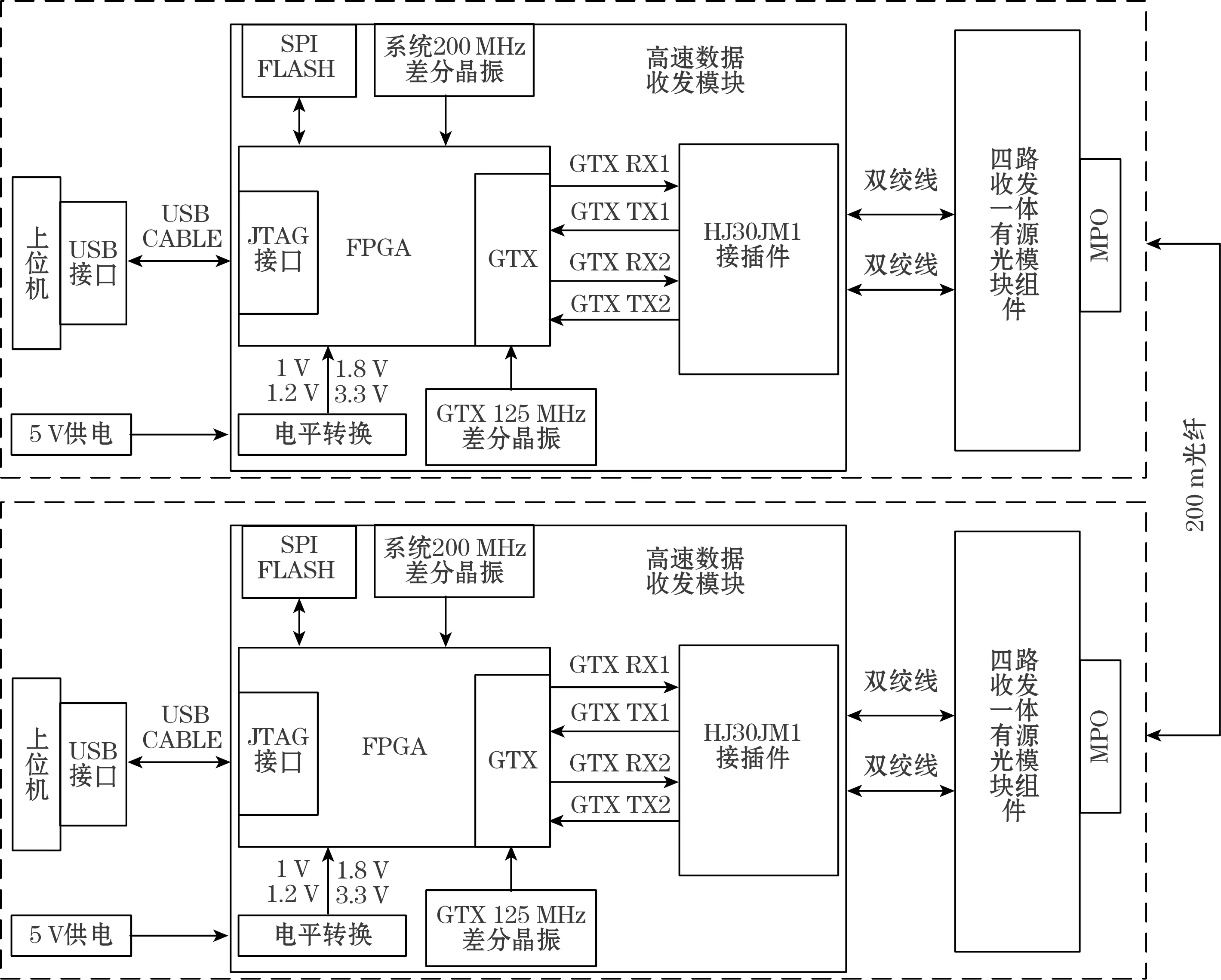

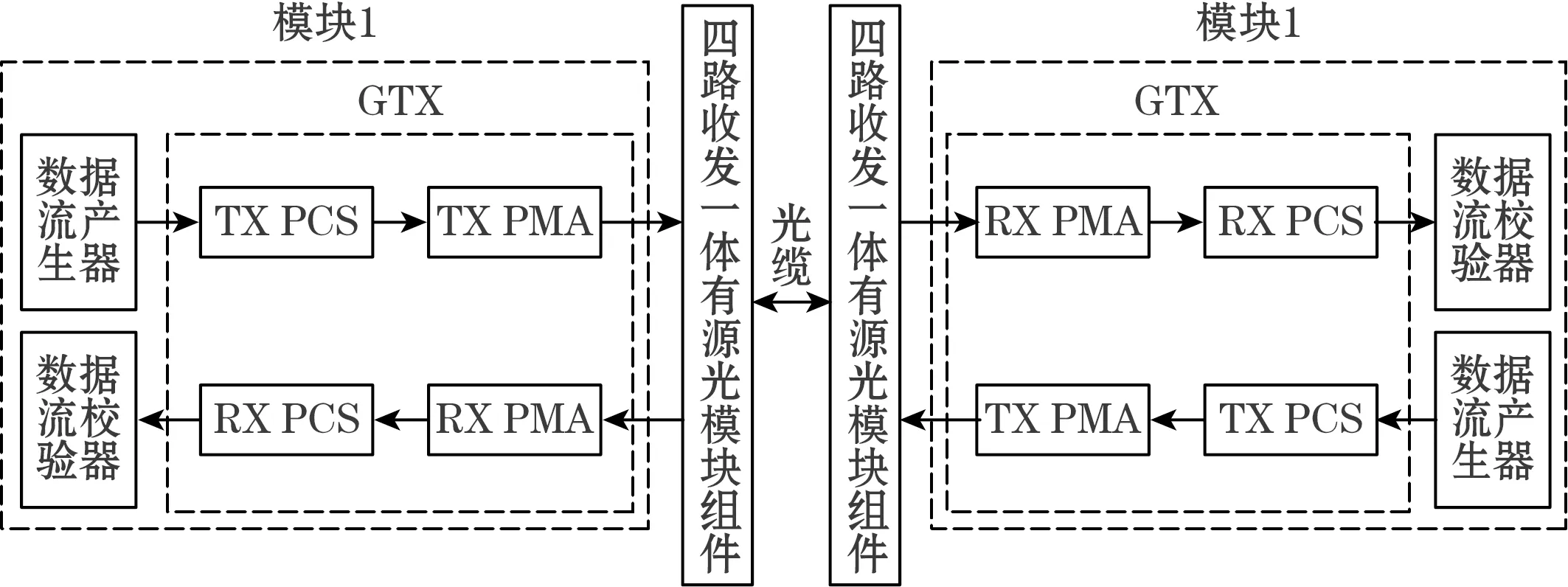

图2为双板交互测试的系统框图,包括2个上位机,2个高速数据收发模块,2个四路收发一体有源光缆组件以及200 m光纤7个模块组成。

图2 双板交互测试设计框图

上位机的主要功能是通过JTAG接口与其中一个高速数据收发模块相连接,通过Vivado软件中的IBERT来观测发送数据与接收数据是否相同,从而得出接收端误码的统计值[7]。每个高速数据收发模块分别与一个四路收发一体有源光缆组件通过HJ30JM1接插件相连接。四路收发一体有源光缆组件之间通过MPO口分别接在200 m光纤两端,形成一个双路收发回路的冗余设计,在验证高速光纤通信的同时,降低了偶然性与故障概率,增强了可靠性。

2 硬件电路设计

国产SMQTK325T系列FPGA作为本平台的控制核心,用到了其内部的高速数据收发模块,同时该核心还需要电源电路、时钟电路以及配置电路等,在这一部分都会详细介绍。同时国产四路收发一体有源光缆组件和光纤作为光电转换以及传输介质来保证通信平台的数据传输。

2.1 高速数据收发模块设计

基于传输系统要求达到1.25 Gbit/s速率和200 m传输的指标要求,考虑到已掌握成熟的KINTYEX-7系列FPGA的应用,因此选用可以原位替换XC7K325T的国产SMQ7K325T系列的FPGA作为控制核心,利用该FPGA内部的GTX作为数据的收发单元,实现数据的发送与接收。该FPGA有8路GTX收发模块,具有高性能高带宽的数据吞吐能力,该GTX收发器集低功耗、高效率与一体,-55~125 ℃条件下,可以支持500 Mbit/s~8 Gbit/s高速通信。

SMQ7K325T系列FPGA内部的高速串行收发器是GTX,也就是MGT(多吉比特收发器)中的一种,是集成在FPGA芯片内部的硬核资源,具有可以配置的优点,可以实现多位数据的串并转换与并串转换,与功能相似的OSERDESE2等部分相比,有着更加复杂的结构,同时还增加了适应高速串行传输的优化措施,例如,8B/10B编码,64B/66B编码等,因此可以有更快的传输速度[8-10]。一些常用的PCIE等都是以MGT为物理层实现的[11]。

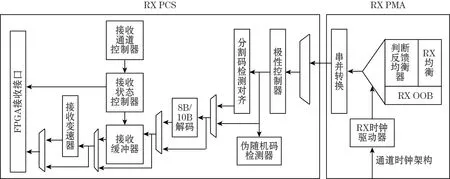

图3与图4分别为GTX收发器发送框图与接收框图,发送端与接收端都分为PMA(物理媒介适配层)和PCS(物理编码子层)2部分[12]。

图3 GTX收发器发送框图

图4 GTX收发器接收框图

从发送框图可以看出,FPGA逻辑产生的并行数据流,传递给发送端PCS模块进行8B/10B编码等处理后进入发送端PMA模块进行并串转换等处理,最后以串行的形式传递出去。

从接收框图可以看出,外部的高速串行数据流,在接收端PMA模块进行串并转换等处理后进入接收端PCS模块,在接收端PCS模块进行解码处理后,最后流入FPGA逻辑。

2.2 FPGA外围电路设计

本平台所使用的控制核心SMQ7K325T系列FPGA对外围的供电电路要求很高,所需的供电电压种类较多。为了提高使用的稳定性,同样选择了深圳市国微电子有限公司的电源芯片。

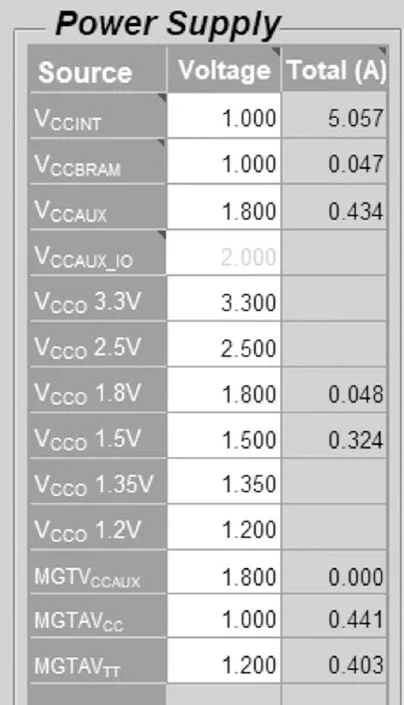

XPE(Xilinx power estimator)工具是面向Soc和FPGA设计的功耗估算器,利用该工具可以计算出各电压相对应的电流值,图5为计算后得到的结果。

图5 XPE计算结果

根据冗余设计以及芯片的实际情况,选择了两款国产电源芯片,分别是SM54810与SM54310。两款芯片的输出电压范围均是0.9~3.3 V可调,前者可以输出最大8 A的电流,使用一个提供1 V电压;后者可以输出最大3 A电流,使用3个,分别提供1.2、1.8、3.3 V电压[13]。其典型电路示意图如图6所示。

图6 SM54810/SM54310芯片典型电路

该系列芯片主要是根据电阻电容组成的补偿网络来调整输出电压的。如图6中,分压网络由R1和R2组成。按照式(1)来计算R1与R2的阻值,一般设置R1为10 kΩ。

(1)

表1为常用电压配置表。在本平台中,用到1 V、1.2 V、1.8 V以及3.3 V。

表1 常用电压配置表

根据R3及式(2)来设置开关频率,范围为280~700 kHz。R3为71.5~180 kΩ。

f=(100/R)×500

(2)

式中:f为芯片的开关频率,Hz;R为电阻阻值,Ω。

外围电路的设计中,还包含一个SPI FLASH,选用SM25QH128M,该芯片是128 Mbit的存储器,主要是用来配置FPGA,保证程序上电自启动,下电不丢失。

图7为该平台接口板的3D模型正反面。

图7 接口板3D模型图

2.3 四路收发一体有源光缆组件设计

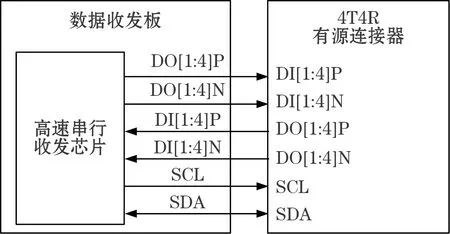

四路收发一体有源光缆组件是光电转换模块,一端为HJ30JY-36TJ改型电插头,内部集成了光电转换电路,另一端为12芯多模MPO光插头。具备I2C 通信监控功能,可监控模块工作温度、电压、发射光功率、接收光功率,并在温度、电压及接收无光时进行报警。该组件可以同时将4路CML电信号转换为4路850 nm光信号,将4路850 nm光信号转换为4路CML电信号,本平台主要使用其中2路设计了相关的电路。图8为电路示意图。

图8 四路收发一体有源光缆组件电路示意图

3 软件测试设计

本平台主要利用Vivado中的IBERT工具来完成平台的测试,同时利用四路收发一体有源光缆组件的IIC通信来实时显示该组件的温度功耗等信息。该部分主要介绍IBERT工具以及相关的测试结果。

3.1 IBERT工具介绍

IBERT工具所进行的测试就是对GTX进行硬件测试。它集成于Vivado中的一款集成误码率测试仪,是利用FPGA的内部资源评估GTX的通断和通信性能的工具,一般的误码率可以算到10-12级别[14]。该工具主要包含2个功能,DRP功能可以动态配置相关高速串行通信的接口,BERT的主要功能是初始化GTX的相关部分组件,产生数据源,进行相关的编码以及解码操作,计算出对应误码率[15]。图9为IBERT模块示意图。

图9 IBERT模块示意图

根据实际情况,本平台做了单板自回环测试及双板交互测试,测试框图如图10与图11所示。

在图10中,单板数据产生器产生特定的数据,数据流通过发送端PCS,发送端PMA,流过外部差分线后回到该单板的接收端PMA,接收端PCS回到数据校验器,其中数据产生器与数据校验器都是FPGA的内部逻辑,因此可以根据数据校验器收到的数据与数据产生器发出的数据相对比,来确定单板数据是否自回环,单板设计是否达到要求,此图省略了FPGA的外围电路等。

在图11中,双板交互测试一共有2路数据流,都是由本模块的数据产生器产生特定的数据流,数据流通过发送端PCS,发送端PMA,通过一对四路收发一体有源光缆组件后,流入另一模块的接收端PMA、接收端PCS后到达数据校验器,其中数据发生器与数据校验器都是FPGA的内部逻辑,由于2组数据流是完全一样的,所以可以互相校验数据流是否正确,以此来确定双板交互是否正确,是否达到需求。

图11 双板交互测试框图

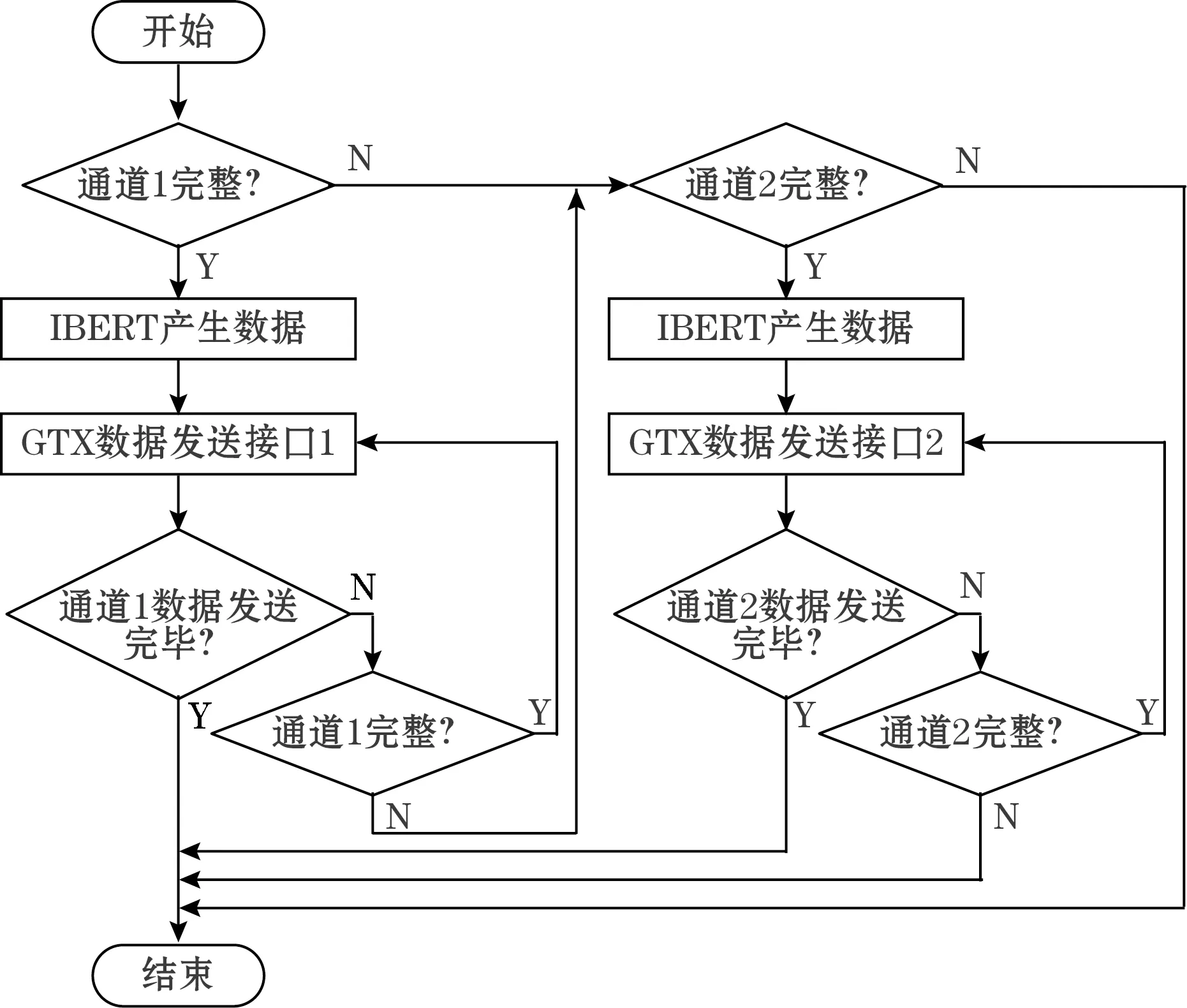

3.2 系统软件介绍

为了保证传输的可靠性,进行了双路通信的冗余设计。图12为软件设计数据发送流程图。在图12中,可以看出通道1与通道2为双冗余设计,当检测到通道1链路完整时,由IBERT产生数据,通过GTX数据发送接口1将产生的数据传递出去,数据发送完毕后,结束发送流程;如果检测到通道1链路不完整,或者在发送的过程中其他因素导致的通道1链路不完整,同时会检测通道2链路是否完整,若完整则会通过通道2链路发送数据,若通道2链路不完整或在发送的过程中其他因素导致链路不完整,才会结束数据发送,该设计提高了系统的可靠性。

图12 数据发送流程图

图13为数据接收流程图,通道1链路接收与通道2链路接为双冗余设计,当通道1链路接收到数据时,由通道1接收数据,并对数据进行暂存,根据数据情况统计误码率;当通道1链路没有接收到数据或者接收中断时,由通道2链路接收数据,完成与通道1链路相同的功能,若通道2也没有接收到数据,说明没有正确链接。以此跟发送端匹配达到双冗余设计的目的。

图13 数据接收流程图

根据对接收到数据的分析以及眼图信息观察后可以判断出数据的正确性,证明系统的设计正确,具体测试结论见3.3软件测试情况。

3.3 软件测试情况

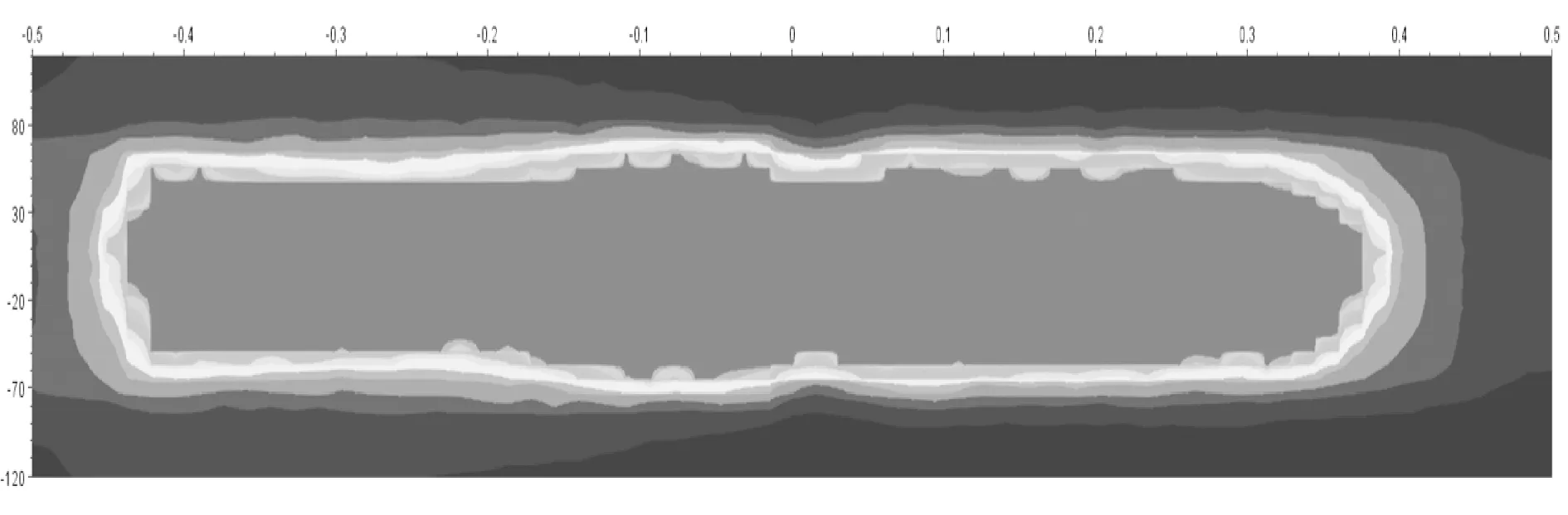

图14为单板自回环测试结果图,接收到的数据产生的“眼图”,“眼图”张开的面积越大,说明通信的质量越高。

图14 单板自回环测试结果“眼图”

图15为单板自回环测试误码率统计图。Status显示的该链路的通信速度为1.25 Gbit/s,Errous显示的误码率为0[16]。

图15 单板自回环测试误码率统计图

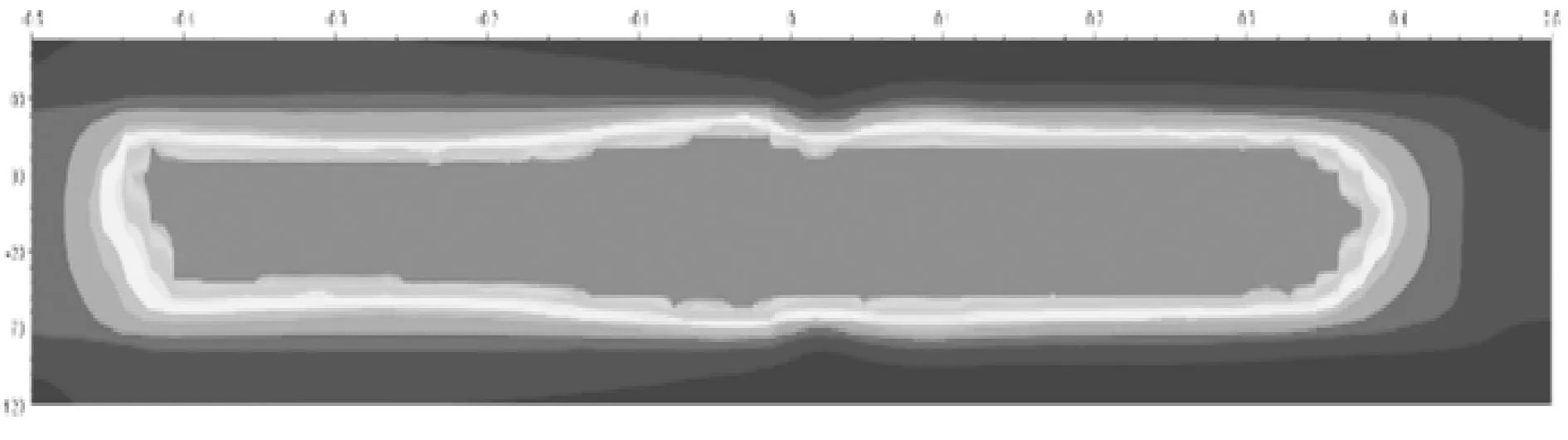

图16为双板交互测试结果图,同单板自回环结果图一样,通道0接收到的数据产生的“眼图”,说明信号质量比较好。

图16 双板交互测试结果“眼图”

图17为双板交互测试误码率统计图。两条链路的通信速度均为1.25 Gbit/s,Errous显示的两条链路的误码率均为0。

图17 双板交互测试误码率统计图

图18为四路收发一体有源光缆组件返回的温度、功耗等信息,从这些信息可以看出本平台的温度、功耗、光功率等信息是合理的,可以达到任务的要求。

图18 四路收发一体有源光缆组件信息

4 测试结果与分析

基于国产器件的高速光纤通信平台如图19、图20所示。图19是单板回环测试实物图,图20是双板交互测试实物图。

图19 单板回环测试实物图

图20 双板交互测试实物图

根据上文中提到的测试结果可以看出,无论是单板回环测试的结果中表现出的眼图、1.25 Gbit/s通信速度和0误码率的结果,还是双板交互测试结果中表现出的眼图,双链路1.25 Gbit/s通信速率与双链路0误码率的结果,都可以看出基于国产器件的高速光纤通信的设计是正确的,可以达到任务要求的指标。

5 结论

本平台使用了国产SMQ7K325T系列FPGA、国产SM54X10系列电源芯片、SPI FLASH,四路收发一体有源光模块组件以及相关的国产晶振、电容、电阻等器件完成了高速通信平台的国产化设计及测试,并利用IBERT对平台进行了全方位的测试,通过加入双冗余设计增强了系统的可靠性,保证了链路的稳定性与准确性。根据测试结果看以看出,本平台达到了任务要求的国产化、1.25 Gbit/s高速、远距离、零误码率、双冗余的测试要求。此次设计仅局限于满足当前任务的指标要求,仅是一个国产高速光纤通信的平台,之后可以尝试进一步提速以及配合其他器件、产品完成一些商用,工业级甚至是航空航天的任务。