基于Simulink与FPGA的收发单元控制协议设计

2022-11-02杨金霖张生春王文艳

杨金霖,张生春,王文艳

(1.西安电子工程研究所,陕西西安 710100;2.西安近代化学研究所,陕西西安 710065)

0 引言

现场可编程门阵列(FPGA)是一种与专用集成电路(ASIC)相对应的半定制的数字逻辑芯片,具有灵活性与高并行性,FPGA在数据接口、以太网、存储阵列、移动通信等领域[1-4]发挥重要作用。在毫米波雷达系统中,FPGA用于实现前端控制、数据接口以及信号处理等功能[5-6],例如GaN开关、SiGe多功能芯片[7]、AD/DA等核心器件都需要根据厂家定义的协议加以控制。灵活的控制方式带来了设计复用率低的问题。此外,在民用、工业等低数据量场合为了简化接口设计并提高传输速率,也常采用自定义协议高速同步串口作为数据传输接口。因此,应研究灵活简洁的控制协议建模与设计方法。

针对上述问题,本文研究了一种基于Simulink和FPGA的收发单元控制协议建模与设计方法,并实现了自定义的高速同步串口发射模块和UART模块,结合FPGA对实例进行了验证,为简化各种复杂、自定义控制协议的设计难度提供了技术参考。

1 控制协议与总体设计

射频前端与控制器的控制协议包含了20个字节的控制指令,包括:1个字节帧头、1个字节工作模式选择、8个字节分别对应8个射频通道控制(1 bit使能码、6 bit相位码)、1个字节的校验、1个字节的帧尾,其余字节为保留字节,留待后续升级使用。

控制接口协议上使用了包括2根线(SCK与SDO)的自定义高速同步串口[8],如图1所示,系统时钟设为10 MHz,LOAD为输入的控制字节数据锁存信号,上升沿有效。LOAD_O为指令发送使能信号,在锁存完成后下一个时钟周期变为高电平,同时使能总线时钟SCK,SDO开始输出20个8 bit指令值,首先按照先低位后高位的顺序输出第1个字节,之后是第2个字节的低位到高位,以此循环,每个字节前设1个时钟周期的低电平,每个字节完成后设2个时钟周期的高电平,第1个字节和最后1个字节为规定的帧头帧尾标志。发送模块在SCK上升沿将数据依次传递至总线上,被控模块在下降沿对总线采样。

图1 收发组件控制器总线时序

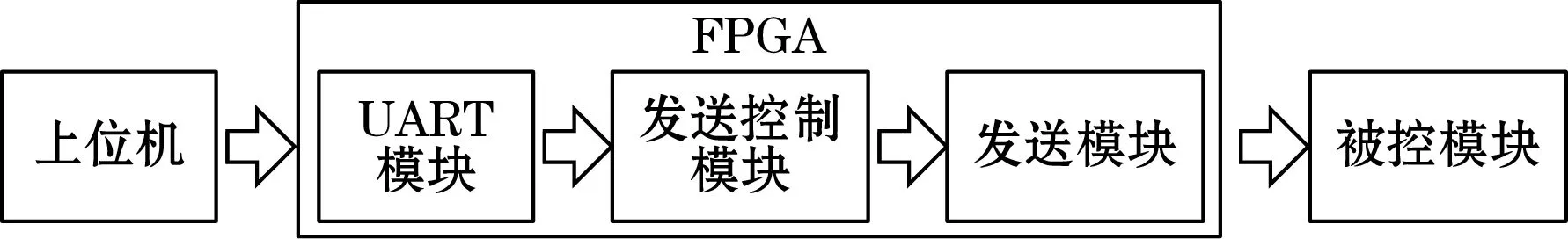

图2为控制器总体设计框图,UART模块实现FPGA与上位机之间的通信,发送控制模块进行接口协议转换产生指令字节以及发送模块所需的控制信号,发送模块将指令按照接口协议传输至被控模块中对相控阵收发单元进行控制。

图2 收发单元控制器总体设计框图

2 控制协议设计

2.1 模块建模

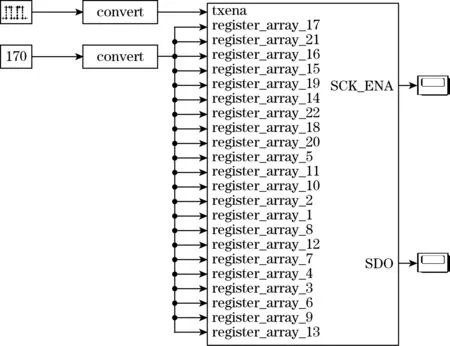

在Simulink环境中,同步串口模块定义了22个8 bit的数组(2个为备份)作为指令数据的输入端口[9],还包括1路锁存信号txena、1路数据总线SDO和1路时钟使能信号SCK_ENA[10],顶层模块如图3所示。

图3 同步串口Simulink仿真电路图

模块由3个并发执行的有限状态机模型LOAD、LOAD_OK和TX组成,如图4所示,“LOAD”为边沿检测器,触发时检测输入信号txena的上升沿并将内部信号loadtx设为1,检测到txena下降沿后loadtx设为0。“LOAD_OK”为指令锁存器,将输入指令锁存在内部寄存器中并产生产生发送使能信号。

图4 同步串口发送模块有限状态机模型

“TX”为模块核心,在s0状态初始化位计数器和寄存器计数器,在锁存完成后转移至s1状态,使能时钟总线SCK_ENA并在SDO上传输起始位,之后进入s2状态,通过不断递减位计数器从低位到高位依次输出当前寄存器的值,当位计数器减少为1时,转移至s3状态,传输当前寄存器的最高位并将寄存器计数器减1以准备传输下一个寄存器的值,之后进入s4、s5状态传输停止位,此时一个控制字节传输完毕。s5状态后为条件判断语句,当寄存器计数器不为0时,说明此时还有指令没有传输,回到s1状态进行下一次起始位的传输,当所有数据传输完毕后,回到s0关闭时钟总线并复位计数器,等待下一次发送使能。

2.2 Simulink环境下时序仿真

Simulink中的数据默认为双精度类型,需要对状态机模型定点化便于数字硬件实现,定点化后的数据类型见表1。

表1 模型数据类型表

根据图3,使用基于采样模式的Pulse Generator模块产生锁存脉冲,使用Data Type Conversion模块将仿真环境的数据类型进行转化以匹配定点化后的串口模型,使用Constant模块作为指令字节,逻辑分析仪得到的仿真结果见图5。

图5 同步串口时序仿真结果

3 HDL代码生成与验证

在Simulink中使用HDL coder生成模型对应的FPGA模块。如图6所示,在Vivado软件中将其与接收模块连接进行环回验证,仿真波形见图7,传输完毕后,接收模块正确的接收到了指令数据[11]。

图6 环回验证原理框图

图7 模块环回验证输出波形

将代码下载至Artix-7 FPGA开发板进行进一步验证,编写了上位机软件实现了控制器与PC的通信,通过FPGA中集成的嵌入式逻辑分析仪观察了相关信号[12-13],如图8所示,UART模块收到完整指令帧且校验通过后拉高rxflag信号,同时串行总线上按照规定协议正确传输了数据。

图8 硬件实现的输出波形

4 结束语

本文基于Simulink设计了收发单元控制器中自定义控制协议并进行了验证,这种控制协议设计方法具有通用性强、设计精准的优点,为后续设计各种复杂、自定义控制协议提供了技术参考。