宇航用VIRTEX5系列FPGA的动态刷新方法及实现

2022-09-08张俊杰孙哲煜周浩林海兵顾得友

张俊杰,孙哲煜,周浩,林海兵,顾得友

上海航天电子技术研究所,上海,201109

0 引言

空间辐射环境中存在各种高能射线粒子,如质子、α粒子、电子、重离子等[1],这些高能粒子照射到CMOS器件上会产生单粒子效应。目前,Xilinx公司的SRAM型FPGA已广泛应用于各类宇航任务。当宇宙射线中的重离子元素在SRAM单元附近沉积足够的电荷后,SRAM数据位会出现单比特错误,发生单粒子翻转[2]。而且,由于SRAM型FPGA的逻辑配置存储在SRAM配置区中,若其中存在误码,则会导致整个电路的布局和功能受到影响。存储配置区在SRAM型FPGA中占据了90%以上的数据位,因此很难提前预防或检测。

SRAM型FPGA对单粒子效应较为敏感,其翻转阈值小于3MeV,在轨容易产生单粒子翻转,因此整星及星上单机在设计时应充分考虑在轨使用的可靠性问题,并根据应用采取相应的加固设计措施[3]。本文给出了一种低成本的抗辐照解决方案,采用定时刷新及三模冗余的方法纠正产生的误码,并通过RTL代码仿真以及测试平台进行了验证,提高了单机设计的可靠性。

1 原理分析

FPGA作为的一种半定制集成电路,包含了大量可灵活配置的硬件资源,既克服了专用ASIC电路无法重新配置的缺点,又突破了可编程器件门电路的资源限制,适用于快速搭建各类高速数字电路。按照所采用的工艺类型划分,FPGA芯片的类型主要有SRAM型、反熔丝型和Flash型三大类。

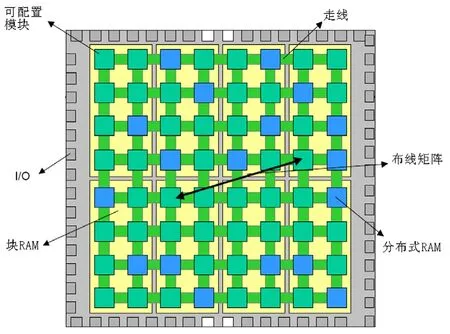

如图1所示,SRAM型的 FPGA主要由可配置逻辑模块(CLB)、输入输出模块(IOB)以及内部连线等资源组成。每个CLB模块又由多个查找表、输入输出模块以及多路复用器等构成,可实现布尔逻辑功能,各CLB模块之间可通过内部连接线资源自由连接。输入输出模块(IOB)为FPGA芯片与外部器件的接口模块,能够实现对输入输出信号的驱动和匹配要求。FPGA矩阵还包括Block RAM模块、分布式RAM和DCM时钟管理模块等。

图1 SRAM 型FPGA 结构

SRAM型FPGA是通过读取片内存储配置区中的程序来配置电路结构的。通过模式配置,用户可以采取不同的编程模式。配置区RAM单元对单粒子事件较为敏感,因此会影响其控制的逻辑资源以及布局布线。根据FPGA的组成结构,单粒子翻转影响的模块一般可分为Block RAM、可配置逻辑模块(CLB)、时钟管理单元、内部连线和IOB模块,具体的翻转截面主要由对各类资源的消耗情况决定[4]。

目前针对SRAM型FPGA的单粒子翻转问题,主要有回读重载以及定时刷新两种防护措施[5]。回读重载即对SRAM型FPGA中的配置数据进行回读,并与外置存储器中的数据进行比对,当其累计错误量超过一定门限值则对SRAM型FPGA进行重载。在重载恢复期间单机功能将暂时停止,因此该方式将影响部分功能。定时刷新通过周期性地对FPGA配置空间进行逐帧重写来纠正配置中的错误,该技术可在不中止系统功能的情况下纠正存储配置区中的单粒子错误。综上所述,本文将采用三模冗余以及定时刷新的方式来降低单粒子翻转错误。

2 系统方案设计

2.1 总体设计

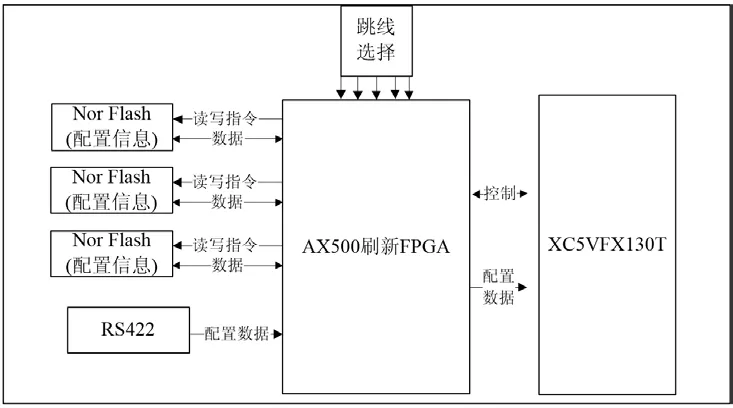

SRAM型FPGA的刷新方式主要有两种:一种是通过反熔丝FPGA进行回读刷新控制;另一种是通过专用的ASIC芯片进行回读刷新控制,但其支持的外围存储器件较为有限[6]。基于通用性设计及灵活性考虑,本文采用方式一进行抗SEU设计,该方案可以兼容多种XILINX VIRTEX系列FPGA,可通过跳线进行FPGA选型配置。本文所提出的抗SEU方案主要由Nor FLASH、刷新芯片(AX500)和XC5VFX130T构成,其结构如图2所示。其中XC5VFX130T芯片主要实现高速数字信号处理,AX500反熔丝芯片主要完成对V5 FPGA的配置、监控及刷新功能,Nor Flash用于存放配置程序。

图2 系统硬件结构

由图1可知,系统工作时,反熔丝FPGA首先会读取三片Nor FLASH中存储的配置文件,采用表决通过的数据作为正确配置信息对XILINX V5系列FPGA进行加载,然后通过SelectMap接口实现对Virtex5 FPGA的定时刷新。

2.2 软件设计

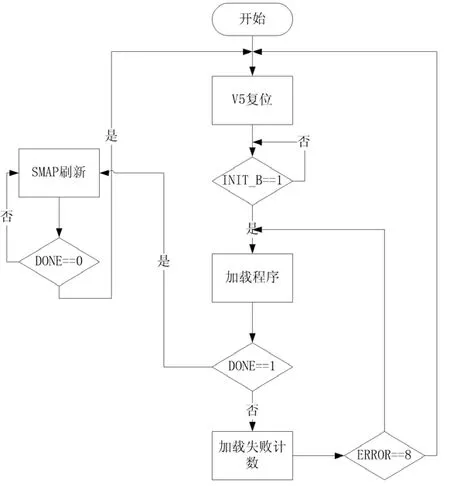

对XILINX V5系列FPGA的刷新控制主要由AX500反熔丝FPGA完成,本文设计的FPGA刷新模块的工作流程如图6所示,主要分为以下3部分。

图6 系统工作流程

(1)FPGA初始化。Xilinx FPGA上电稳定期间,设计将PROG_B信号拉低3ms对被加载的FPGA配置进行初始化复位,在复位过程中INIT_B信号将保持低电平。等待TPOR时间后若INIT_B拉高则表示FPGA配置区内存已清除,可以执行下一步流程;若INIT_B一直为低,则不断检测该信号,直至拉高为止。

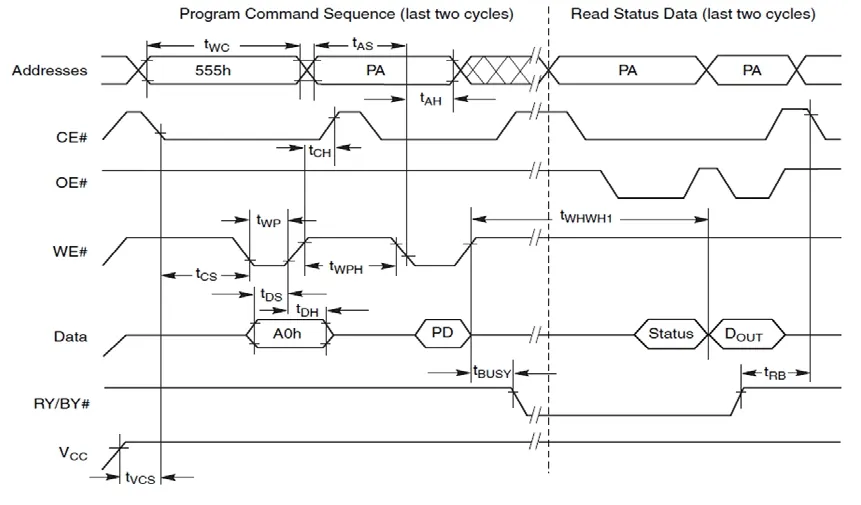

(2)配置FPGA。初始化结束后,开始配置FPGA,设置FPGA管脚M2~M0为110,FPGA将在INIT_B拉高期间设置pin脚,设置加载模式为SelectMap方式。随后反熔丝FPGA将按指定时序从Nor Flash中读取配置数据进行表决,将表决通过的配置数据沿CCLK送至SelectMap接口数据线上。然后模块将持续监测DONE信号查看是否加载成功,若超过预设的配置时间仍未拉高,则产生PROG_B低电平脉冲对Xilinx FPGA进行重载,重载8次仍不成功则回到初始化状态对FPGA进行复位。反熔丝FPGA与Nor Flash接口信号主要由Address[22:0]、CE#、OE#、WE#、Data[15:0]、RY/BY#等信号构成,接口时序图如图3所示[7]。

图3 NorFlash 读时序图

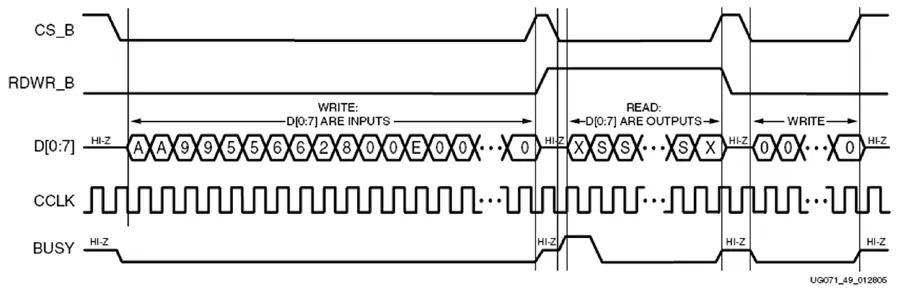

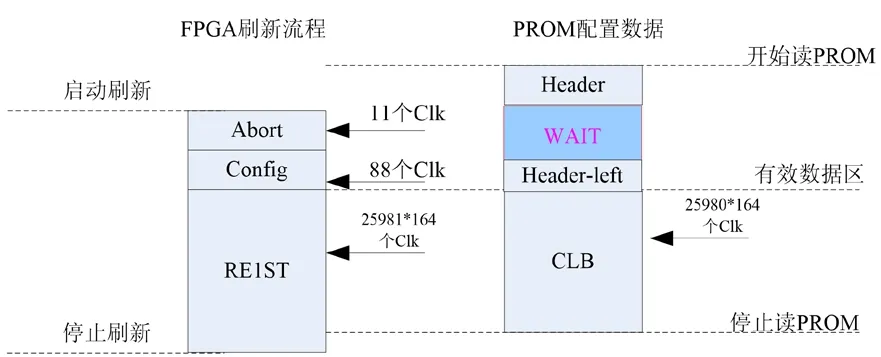

(3)定时刷新。当监测到DONE信号拉高后,则说明Xilinx FPGA加载成功。随后按10MHz的工作频率执行定时刷新操作并对写读FAR寄存器进行SEFI检测,检测到单粒子翻转则进行FPGA重载。根据用户手册,XC5VFX130 FPGA的配置数据共有1065221字(25981帧*41字/帧)。如图4所示,刷新FPGA与待加载FPGA接口信号主要由PROG_B、INIT_B、DATA[0:7]、CCLK、DONE、RDWR_B、CS_B等信号构成。

图4 FPGA 刷新时序图

图5 FPGA 刷新流程图

3 应用验证

本文提出了一种基于反熔丝FPGA的单粒子防护方案,为了测试该方案是否满足设计要求,本节使用Modelsim对设计的RTL电路进行了仿真,并进行了应用验证[8]。

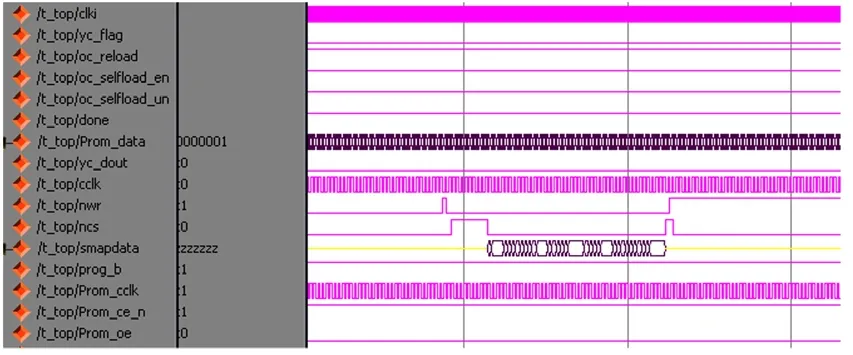

图7所示为刷新控制模块的仿真验证波形,从图中可以看出,控制模块将读取的配置数据通过SelectMap接口对FPGA进行定时刷新,刷新时序符合FPGA芯片手册的要求[9]。随后通过模拟故障注入的方式对单粒子翻转进行了模拟,禁止刷新功能,并且经JTAG调试接口对XILINX FPGA加载错误的bit文件;注入错误的配置文件后单机遥测存在异常,打开刷新功能后单机功能恢复正常。上述验证方案表明本文设计的系统功能能够及时纠正单粒子错误。

图7 定时刷新时序图

4 结语

本文以航天任务为背景,分析了XILINX Virtex系列FPGA芯片的机理,并根据实际需求提出了一种三模冗余及定时刷新相结合的抗SEU方案[10]。经过仿真及验证结果表明,本文所提出的抗SEU方案可有效解决SRAM型FPGA芯片在空间环境下的翻转问题,提高了FPGA在宇航领域应用的可靠性。