基于三模冗余和三级错误拦截的四节点翻转容忍锁存器设计

2022-09-05宁亚飞

宁亚飞

(安徽理工大学计算机科学与工程学院,安徽 淮南 232001)

0 引言

目前,CMOS 技术已缩小到深纳米级,实现了集成电路和系统的高集成度、低开销和高性能。然而,随着晶体管特征尺寸的大幅度减小,CMOS器件对软错误的敏感性也在显著增加,这将导致数据损坏、执行失败,在最坏情况下甚至会出现系统崩溃。当质子和中子等辐射粒子与集成电路的敏感节点碰撞时,会产生额外的电荷,导致错误的瞬态脉冲或节点翻转,这被称为软错误[1-2]。软错误包括单节点翻转(Single Node Upset,SNU)、双节点翻转(Double Node Upsets,DNUs)、三节点翻转(Triple Node Upsets,TNUs)、四 节 点翻 转(Qua⁃druple Node Upsets,QNUs)。软错误会影响处在恶劣辐射环境中的纳米级CMOS 电路和系统的可靠性。因此,需要对纳米级电路进行有效的加固处理。本研究提出一种基于三模冗余和三级错误拦截的四节点翻转容忍锁存器设计(TTEQNUTL)。该锁存器由3 个单节点翻转自恢复模块(分别为SNUSR1、SNUSR2、SNUSR3)、1 个三级错误拦截模块和7 个传输门组成。每个SNUSR 模块均包含两个普通C 单元和两个钟控C 单元,四个C 单元可形成一个环形结构。由于每个SNUSR 模块都具有SNU 自恢复能力,错误拦截模块可用三级方式对错误进行拦截。因此,本研究提出的锁存器可实现QNUs 容忍。

1 锁存器的电路结构和工作原理

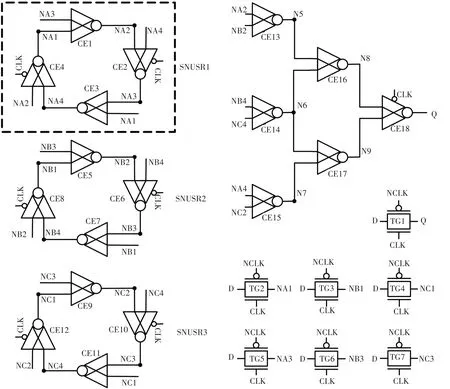

本研究提出的锁存器结构如图1所示。该锁存器由18个C 单元(其中7个是钟控C 单元)和7个传输门组成,D和Q分别代表着输入和输出,CLK和NCLK分别为系统的时钟信号和负系统的时钟信号。

图1 TTEQNUTL锁存器结构示意图

当CLK=1、NCLK=0时,锁存器处于透明期,7个传输门打开,7个钟控C单元关断,输入数据传入到节点Q、NA1、NA3、NB1、NB3、NC1和NC3。

当CLK=0、NCLK=1时,锁存器处于锁存期,7个传输门关断,7个钟控C单元打开。

2 容错原理

本研究所提出的TTEQNUTL 锁存器能够实现对SNU、DNUs、TNUs 和QNUs 的完全容忍。本研究只分析锁存器在锁存期内的容错原理。在透明模式下,即使高能粒子撞击内部节点造成翻转,输入信号也能快速对逻辑值进行刷新。下面分别对SNU、DNUs、TNUs和QNUs进行容错分析。

2.1 SNU容忍

由于锁存器是由C 单元组成,C 单元可容忍其中一个输入的变化,且输出不会受到影响。因此,当其中某个节点发生翻转时,将不会对其他节点产生影响,剩余节点仍保持正确的逻辑值,并能把发生翻转的节点恢复成正确的逻辑值,实现了SNU自恢复,也即实现SNU容忍。

2.2 DNUs容忍

锁存器发生DNUs容忍时,有以下3种情况。

2.2.1 发生翻转的2 个节点位于三级错误拦截模块中,则SNUSR 模块中的节点不发生翻转。例如,N5、N6 节点发生翻转,此时会引起N8 节点翻转,剩余节点则保持正确的逻辑值。NA2、NB2节点通过CE13 将N5 节点恢复为正确的逻辑值,NB4、NC4 节 点可通 过CE14 将N6 恢复为 正确的逻辑值,N5、N6 节点会将N8 节点恢复为正确的逻辑值。

2.2.2 每个SNUSR 模块中最多有1 个节点发生翻转。例如,NA1、N5 节点发生翻转时并不会引起其他节点翻转。由于SNUSR 模块具有SNU 自恢复性,因此NA1 节点可自恢复过来,NA2、NB2 节点通过CE13将N5节点恢复过来。

2.2.3 每个SNUSR 模块中最多有2 个节点发生翻转。例如,NA1、NA3 节点发生翻转时,此时会引起NA2、NA4 节点发生翻转。由于SNUSR2 和SNUSR3 模块中的节点不受影响,通过C 单元的阻塞作用,N5、N6 和N7 节点将保持正确的逻辑值,Q节点也保持正确的逻辑值。综上所述,锁存器可实现DNUs容忍。

2.3 TNUs容忍

锁存器发生TNUs容忍时,有以下4种情况。

2.3.1 发生翻转的3 个节点位于三级错误拦截模块中,SNUSR 模块中的节点不发生翻转。例如,当N5、N8 和Q 节点发生翻转时,此时将不会引起其他节点翻转。由于3 个SNUSR 模块中的节点不受影响,可通过CE13、CE16 和CE18 依次将N5、N8和Q节点恢复为正确的逻辑值。

2.3.2 每个SNUSR 模块中最多有1 个节点发生翻转。例如,NA1、N5和Q节点发生翻转时,并不会引起其他节点翻转。NA1、N5 和Q 节点可通过CE4、CE13和CE18恢复过来。

2.3.3 每个SNUSR 模块中最多有2 个节点发生翻转。例如,NA1、NA3 和N5 节点发生翻转时,此时会引起NA2、NA4 节点发生翻转。由于SNUSR2 和SNUSR3 模块中的节点不受影响,N6、N7 节点保持正确的逻辑值,因而N8、N9 节点保持正确的逻辑值,Q节点也保持正确的逻辑值。

2.3.4 每个SNUSR 模块中最多有3 个节点发生翻转。当NA1、NA3 和NA4 节点发生翻转时,会引起NA2 节点发生翻转。由于SNUSR2 和SNUSR3模块中的节点不受影响,在C 单元的阻塞作用下,N5、N6和N7节点将保持正确的逻辑值,Q节点也能保持正确的逻辑值。综上所述,锁存器可以实现TNUs容忍。

2.4 QNUs容忍

锁存器发生QNUs容忍时,有以下5种情况。

2.4.1 发生翻转的4 个节点位于三级错误拦截模块中,SNUSR 模块中的节点不发生翻转。当N5、N6、N8 和Q 节点发生翻转时,并不会引起其他节点翻转。由于3 个SNUSR 模块中的节点不受影响,N5、N6 和N8 节点分别通过CE13、CE14 和CE16恢复过来,Q 节点可通过CE18 节点恢复为正确的逻辑值。

2.4.2 每个SNUSR 模块中最多有1 个节点发生翻转。例如,NA1、N5、N8 和Q 节点发生翻转,此时并不会引起其他节点翻转。由于SNUSR 模块具有SNU 自恢复性,所以NA1 节点可自恢复到正确的逻辑值,N5 和N8 节点则通过CE13 和CE16 恢复过来,Q 节点可通过CE18 节点恢复为正确的逻辑值。

2.4.3 每个SNUSR 模块中最多有2 个节点发生翻转。例如,当NA1、NA3、N5 和N8 节点发生翻转时,此时会引起NA2、NA4 节点也发生翻转。由于SNUSR2和SNUSR3模块中的节点不受影响,N6、N7 节点保持正确的逻辑值,N9 节点也保持正确的逻辑值,在C单元的阻塞作用下,Q节点也将保持其原有的逻辑值不变。

2.4.4 一个SNUSR 模块中最多有3 个节点发生翻转。当NA1、NA3、NA4 和N5 节点发生翻转时,会引起NA2 节点发生翻转。由于SNUSR2 和SNUSR3 模块中的节点不受影响,通过C 单元的阻塞作用,N6、N7 节点将保持正确的逻辑值,N8、N9节点也保持正确的逻辑值,因此Q 节点将保持其正确的逻辑值。

2.4.5 一个SNUSR 模块中最多有4 个节点发生翻转。当NA1、NA2、NA3 和NA4 节点发生翻转时,并不会引起其他节点翻转。由于C 单元的阻塞作用,N5、N6 和N7 节点将保持正确的逻辑值,因此Q 节点也保持正确的逻辑值。综上所述,锁存器可实现QNUs容忍。

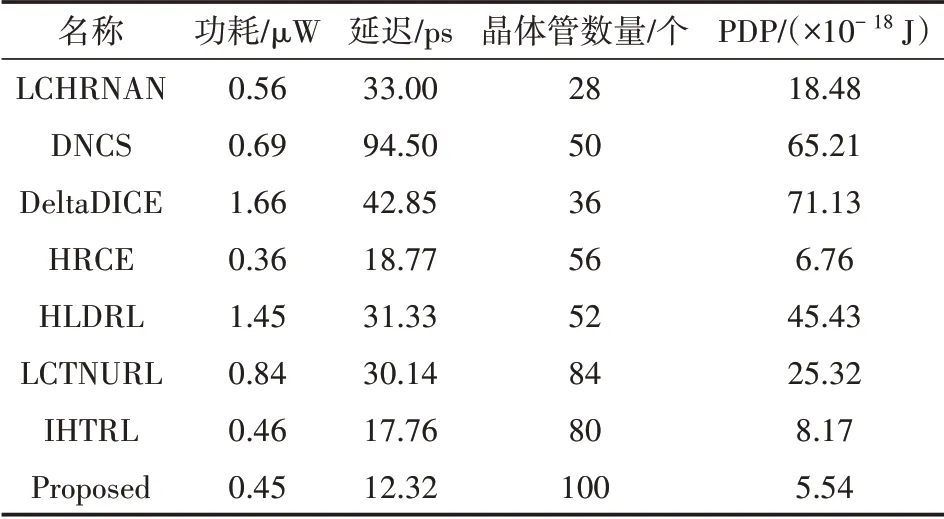

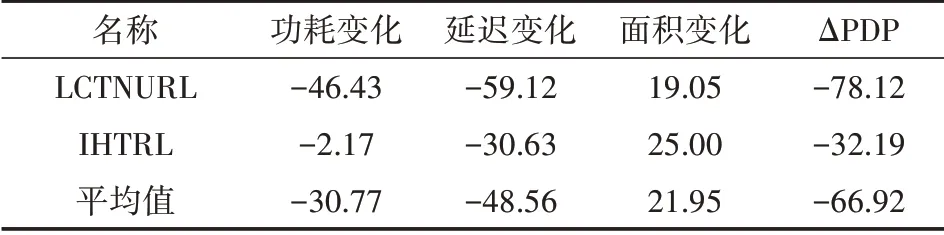

3 开销比较

本研究对基于三模冗余和三级错误拦截的四节点翻转容忍的锁存器与LCHRNAN 锁存器[3]、DNCS 锁 存 器[4]、DeltaDICE 锁 存 器[5]、HRCE 锁 存器[6]、HLDRL 锁 存 器[7]、LCTNURL 锁 存 器[8]和IHTRL 锁存器[9]进行对比,具体包括面积、延迟和功耗等方面的比较。比较结果见表1和表2。

表1 开销对比

表2 与TNUs自恢复锁存器开销相对变化 单位:%

由表1 的第2 列可以看出,本研究所提出的锁存器的功耗仅次于HRCE 锁存器,从第3 列和第5列可以看出,该锁存器有着最小的延迟和PDP。

4 结语

本研究提出了一种基于三模冗余和三级错误拦截的四节点翻转容忍锁存器,该锁存器能够实现SNU,DNUs,TNUs 和QNUs 的完全容忍,与两个锁存器(LCTNURL,IHTRL)平均值相比,提出的锁存器功耗降低了30.77%,延迟降低了48.56%,PDP 降低了66.92%。