基于FPGA的角跟踪接收机误差信号平滑算法的实现

2022-08-09王玉凡高玉龙吴兆平王恺宇

王玉凡,高玉龙,吴兆平,王恺宇

(中国空间技术研究院西安分院,西安 710000)

0 前言

角跟踪接收机目前广泛应用于我国中继卫星和各类低轨用户星,主要功能是接收星间链路天线馈源输出的两路和、差信号,将星间链路天线在自跟踪过程中偏离天线电轴的角位置误差转换成能够控制天线运动的误差信号,在星间天线对准情况下,误差信号抖动大小决定天线跟踪精度。在低信噪比情况下,随着星间链路信息速率越来越大,角跟踪接收机输出误差信号抖动变大,当信息速率达到300Mbps时,误差信号抖动无法满足自跟踪系统使用要求。本文提出一种16点加权滑动窗平滑算法,对角跟踪接收机误差信号进行平滑处理,并在FPGA硬件平台上实现,通过系统自跟踪试验,能够满足工程使用要求。

1 误差信号提取原理

角跟踪接收机为适应从不同调制方式(例如BPSK或QPSK)和码速率(例如100 kbps~300 Mbps)信号中提取角误差信号,采取小部分带宽法[1]。基本原理框图如图1所示,通过两个带通滤波器(BPF2和BPF3)完成对输入信号小部分带宽的提取。提取信号经过包络检波器检波,包络检波器输出包络信号给数字信号处理单元,完成方位差、俯仰差误差信号的分离,并转换成电压电平输出。在星间链路两端天线对准时,由于受系统噪声影响,角跟踪接收机输出方位差、俯仰差电压在0V附近波动,对方位差、俯仰差电压进行三倍均方根统计,统计结果定义为误差信号抖动。

图1 角跟踪接收机原理框图Fig.1 Schematic diagram of angle tracking receiver

2 算法仿真分析

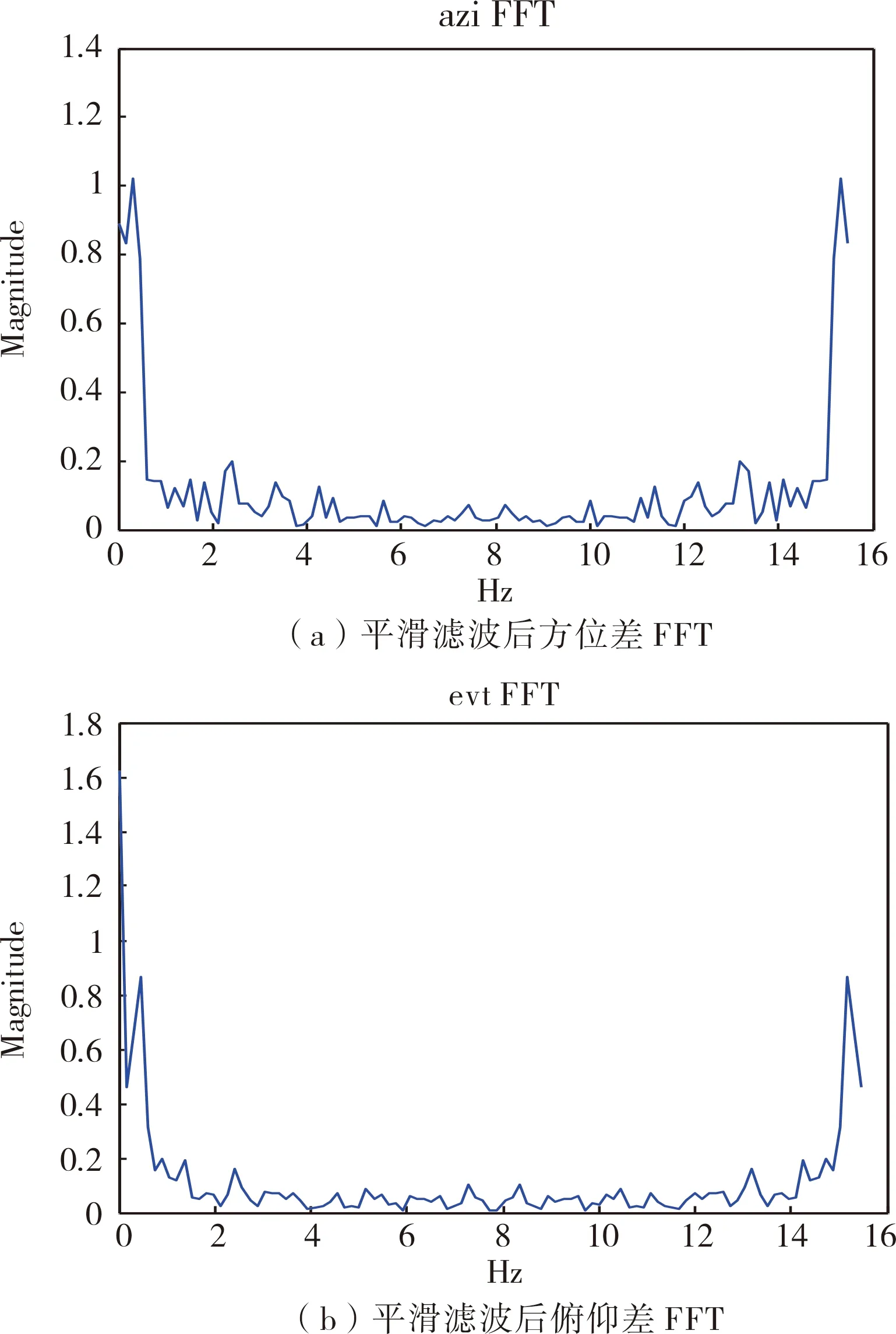

角跟踪接收机中误差信号解调时间为64 ms,即每64 ms输出一次误差信号电压值,通过测试设备对输出数据进行采集存储,然后进行频谱分析。使用Matlab工具对方位误差电压和俯仰误差电压数据进行频谱分析,结果如图 2所示。从图2中可以看出方位差、俯仰差电压中噪声比较均匀分布在整个采样频率中,而实际上方位差、俯仰差电压应为低频信号甚至是直流信号。因此选取的平滑算法必须呈现低通特性,滤除高频噪声,保留低频有用信号。

图2 方位、俯仰差电压FFT计算结果Fig.2 Calculation results of error signal voltage FFT

采用16点平滑窗算法,基本实现原理是输出的误差信号为当前解调出来的误差信号与前面15个时刻输出误差信号进行累加,然后取平均得到角跟踪接收机误差信号输出值。平滑窗输入输出基本表达式如下:

y(n)=(x(n)+x(n-1)+…

+x(n-15))/16

(1)

其中y(n)为当前n时刻平滑窗输出的值,x(n),x(n-1)...x(n-15) 为平滑窗输入值,式(1)进行Z域变换可得如下表达式:

Y(Z)=(X(Z)+Z-1X(Z)+…Z-15X(Z))/16

(2)

(3)

表1 方位差、俯仰差平滑前后误差抖动比较Tab.1 Error jitter before and after smoothing

图3 时域和频域曲线Fig.3 Time domain and frequency domain diagrams of h(n)

图4 平滑滤波后方位差、俯仰差FFTFig.4 FFT calculation results of azi and evt after smoothing filtering

3 FPGA算法实现

通过以上分析,在方位差电压和俯仰差电压输出端增加平滑窗进行平滑处理,能很好降低方位差电压和俯仰差电压抖动。在硬件平台处理器FPGA上对平滑窗算法进行实现,从式(1)中可以看出需要进行15次加法运算和1次除法运算。为节省FPGA资源,实际实现过程采用1次加法运算、1次减法运算以及1次截位操作完成平滑窗功能[7]。具体模块实现步骤如下:

1)设置计数器A,每次新来一个方位差电压值和俯仰差电压值,计数器A加1;

2)生成一个16字节数据长的移位寄存器,完成16个数据的移位存储操作,每新来一个数据,移位寄存器进行一次移位操作,功能框图如图 5所示;

图5 平滑窗实现框图Fig.5 Smooth algorithm implementation diagram

3)每新来一个数据,累加器SUM与输入数据进行累加,累加值寄存在SUM中;

4)计数器A等于16时,累加器SUM累加值赋值给寄存器B,同时寄存器B进行低位截取,舍弃低4位,对高位输出,完成除16运算;

5)计数器A>16时,计数器停止计数,累加器SUM与新数据累加,然后减去移位寄存器输出的(n-16)数据,得到的值赋给寄存器B,B进行低位截取,舍弃低4位,对高位输出,完成除16运算。

采用VHDL语言在FPGA上对上述平滑窗实现,使用modelsim仿真工具进行仿真。仿真时设定azi_fir_in为方位差输入数据,evt_fir_in为俯仰差输入数据,azi_evt_fir_in_valid为输入数据有效时刻,azi_fir_out为方位差平滑输出数据,evt_fir_out为俯仰差平滑输出数据,azi_evt_fir_out_valid为输出数据有效时刻,仿真结果如图 6所示,从图6中可以看出FPGA平滑窗代码实现正确。

图6 FPGA平滑窗仿真图Fig.6 FPGA smooth window simulation

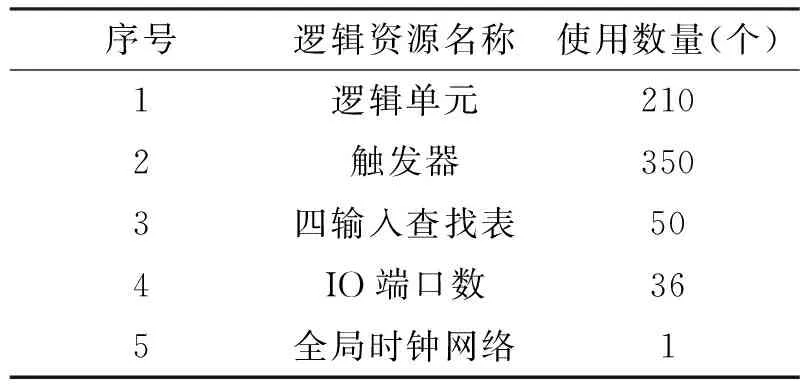

实现过程采用桶形数据移位的方式替代除法运算,有效的降低了FPGA资源,通过Xilinx ise 开发工具对两种实现方式资源占用率进行比对,如表2、表3所列,桶形数据移位方式input LUTs 资源相对除法运算方式资源降低84.2%。

表2 桶形数据移位方式资源占用量Tab.2 Bucket data shift resource usage

表3 除法运算方式资源占用量Tab.3 Division method resource usage

4 结论

本文结合工程实际中方位差、俯仰差抖动大的问题,首先对方位差、俯仰差进行频谱分析,得到方位差、俯仰差中的噪声频谱量,然后构建平滑窗的传输函数,最后使用桶形数据移位方式在FPGA硬件上以较小的资源占用率实现该算法。经过试验验证该方法能够有效的解决方位差、俯仰差抖动在低信噪比、高码速率情况下输出超差的问题,使方位差、俯仰差误差信号抖动输出值降低约77%,显著提高系统性能。目前该方法随我国二代中继卫星成功在轨应用。