重复短路应力下p-GaN HEMT 器件的阈值电压退化机制*

2022-07-07潘超武

伍 振,周 琦,潘超武,杨 宁,张 波

(电子科技大学电子薄膜与集成器件国家重点实验室,成都 610054)

1 引言

p-GaN HEMT (P-Doped Gallium Nitride High Electron Mobility Transistor)是实现增强型GaN 功率器件的主流结构之一,p 型掺杂的GaN 所形成的p-GaN 帽层能提高栅下的能带,将AlGaN/GaN 界面处的2DEG(Two-Dimensional Electron Gas)量子阱提升到费米能级EF以上,从而实现增强型特性[1]。p-GaN HEMT 由于性能、可靠性和成本之间具有良好的平衡,已成为主流的商用GaN 功率器件,并且在快充、激光雷达等领域已获得应用与认可,同时也在数据中心服务器电源、5G 移动通信电源、新能源汽车等新兴领域具有巨大应用潜力。

当p-GaN HEMT 器件应用在高压、高频开关电路中时,不可避免地会遭遇短路事件,国内外已报道了GaN 功率器件短路相关的可靠性研究[2-5],但这些研究大多聚焦于单次及多次短路过程中的波形变化,不同应力条件(VGS、VDD等)对器件短路耐受性的影响以及器件的最终失效模式,而针对器件在短路应力后的退化物理机制以及器件恢复特性的动力学问题还缺乏深入的研究。当器件在实际应用中遭受短路事件时并不完全是破坏性的,器件电学性能的变化会影响高频、高功率电路系统的性能,比如阈值电压VTH的正向漂移会增大器件的开关损耗和导通损耗,导致电路系统的转换效率下降,这就需要设计复杂度更高的驱动电路去补偿VTH衰退带来的影响。

本文利用TCAD 和理论分析首先阐明了短路电流及短路峰值电流下降的机理;通过分阶段监测重复短路应力后的转移和输出特性曲线,发现VTH的漂移量与漏极电流IDsat的退化量依赖于短路次数和短路应力大小(VGS),结合Metal/p-GaN/AlGaN/GaN 异质栅能带理论与器件的动态恢复特性,揭示了AlGaN 势垒层陷阱和p-GaN/AlGaN 界面陷阱引起的VTH可恢复性退化机理;此外,在苛刻短路应力条件(VGS=6 V,VDD=60 V) 下,由于栅下高电场激发热电子轰击p-GaN/AlGaN 界面,进而产生了界面缺陷,导致VTH和IDsat的永久退化。

2 实验平台与待测器件

2.1 短路测试平台

短路测试平台采用ITC57250 短路测试系统,图1为简化后的短路测试原理图。其工作特点如下:函数发生器给被测器件(Device Under Test, DUT)的栅极驱动器提供逻辑信号VPulse,栅极驱动器控制短路时间tSC和栅源电压VGS的大小;外加栅电阻RG能够影响开关过程中的充放电电流进而影响开关速度,采用较大的RG可以有效降低开关速度,从而有效防止开关过程中的VGS过冲事件,最终避免器件的栅极击穿问题;漏源电压VDS与短路电流ID分别用高压差分探头与Pearson 电流传感器探测;LStray为杂散电感,CDC为高压储能电容组,用以稳定VDS以及提供短路电流ID。

图1 ITC57250 短路测试系统测试简化电路

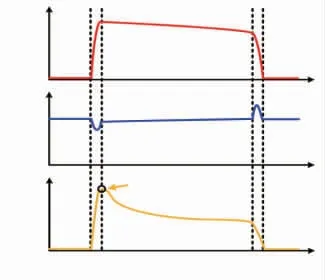

本文采用业界常用的硬开关型短路应力方案,即在施加漏极高压的情况下将栅极打开和关闭,典型的p-GaN HEMT 器件硬开关型短路波形如图2 所示,当VDS与VGS同时存在时,器件既承受很高的VDS,又承受较高的ID,最终实现一次短路测试。

图2 典型的p-GaN HEMT 器件硬开关型短路波形

2.2 待测器件

本文选用EPC(Efficient Power Conversion)公司的商用p-GaN HEMT 功率器件为待测器件,图3(a)为器件的横截面示意图。器件的关键电学参数如下:阈值电压约为1.3 V,导通电阻约为25 mΩ,脉冲电流为37 A,额定电压为100 V,栅压摆幅为-4~6 V。由于该器件的栅金属与p-GaN 帽层为肖特基接触(Schottky Contact),故其栅堆叠(Metal/p-GaN/AlGaN/GaN)一般等效为由2 个背靠背的Metal/p-GaN 形成的肖特基二极管D1 和p-GaN/AlGaN/GaN 形成的P-I-N 二极管D2串联组成[6],具体的等效模型如图3(b)所示。

图3 100 V p-GaN HEMT 器件

2.3 测试方案

在本研究中需要分阶段表征p-GaN HEMT 器件在经短路应力后的关键电学特性(转移特性、输出特性等),为了研究器件在多次短路应力过程中的电学特性退化,防止器件发生硬性短路失效或烧毁,本文采用了缓解器件失效的短路应力方案(如图4 所示),将tSC固定为10 μs,短路脉冲间隔固定为5 s,总的短路应力次数为100 次。将器件在短路应力前记为fresh状态并测量fresh 状态下的电学特性,在100 次总的短路应力次数之间,测量第一次、第10 次、第30 次、第60 次以及第100 次短路应力后的电学特性,并记录电学特性的变化;当100 次短路应力后的电学特性测完后将器件静置,这时器件将进入恢复阶段。

图4 短路应力与电学特性测试方案

此外,为了更加及时、精确地测量器件的电学性能,利用Keysight B1505A 功率器件分析仪进行电学特性测试。由于ITC57250 与Keysight B1505A 均为插拔式的测试端口,故器件从短路应力结束后到电学特性测试结束后的时间间隔将小于60 s,这对电学特性变化的监测至关重要。

3 结果与讨论

3.1 短路波形

对所有测试作必要说明:RG固定为30 Ω,器件的壳温TCASE固定为25 ℃,若无特殊说明,均参考以上数值。

本文针对DUT1 采用VGS=6 V、VDD=60 V 的重复短路应力方案,图5 为该器件的实际短路波形。从图5可以看出在10 μs 的短路时间内,VGS从6.3 V 持续减小至4.2 V,这是因为在整个短路期间,器件结构内部将会产生大量功耗,从而导致AlGaN/GaN 异质结界面附近的沟道温度TJ急剧上升,图6 是基于Sentaurus-TCAD 仿真的内部温度分布图。其中栅极区域正下方TJ的上升将会辅助栅下的电子越过AlGaN势垒,导致IG增大,从而导致RG的压降增大,最终器件的VGS呈现下降趋势。此外,电子迁移率强烈依赖于TJ,其关系式可简化为μn(TJ)∝TJ-K,K 为温度系数,一般文献中取为1~2.15[7],由于短路期间整个横向方向上的沟道温度上升,电子迁移率将大大下降。沟道电流I 可简化为:

图5 DUT1 的重复短路波形

图6 器件在短路期间(tSC=1 μs)的内部温度分布(VGS=5 V,VDD=55 V)

式中q 为电子电荷量,n 为电子浓度,μn(TJ)为电子迁移率,E 为电场强度。

由于VDD固定为60 V,故忽略E 的大小变化。根据式(1)可知,在单个短路应力期间,VGS下降导致2DEG 沟道中的n 下降,TJ的上升导致电子迁移率下降,最终使得ID急剧下降;例如在第一次短路的过程中,ID可从59 A 降至25 A,下降了58%。此外,随着短路次数的增加,短路尖峰电流IDpeak呈现下降的趋势,从第1 次短路的59 A 降至第100 次短路的49 A,这主要与VTH的右漂相关;因为对于器件的短路事件而言,器件是在较高的VDS和ID共存的饱和区中工作[8],VTH的右漂将会导致过驱动电压VGS-VTH减小,从而导致饱和区中的饱和漏电流减小,最终导致IDpeak减小。

3.2 阈值漂移与电流衰退

图7(a)为DUT1 在fresh 状态下的转移特性曲线以及DUT1 在经过1 次、10 次、30 次、60 次以及100次短路应力后的转移特性曲线对比图,定义VDS=1 V、ID=1 mA 时对应的VGS为VTH,可以发现随着短路应力次数的增加,VTH从1.48 V 持续右漂至2.13 V 并且有趋于饱和的趋势,最大漂移量为+0.65 V。图7(b)为DUT1 在重复短路应力前后的输出特性曲线(VGS=5 V),器件的IDsat随着短路次数的增加而单调减小至27.88 A。VTH持续右漂与IDsat持续下降的现象是相关联的,因为VTH是影响饱和漏电流大小的主要因素之一,VTH右漂将导致IDsat下降[9]。

图7 DUT1 在重复短路应力前后的关键电学特性

为了研究器件VTH右漂和IDsat衰退的物理机制,本文增加了VGS为4 V、5 V 以及6 V,VDD为60 V 的短路应力条件,为了区分不同短路应力条件对p-GaN HEMT 器件退化的影响,每一个应力条件对应一颗器件。图8(a)为DUT1、DUT2 以及DUT3 在重复短路应力后的VTH漂移量,其中第0 个Cycle 对应器件的fresh 状态;图8(b)则对比了各个器件在重复短路应力后的归一化饱和漏电流,即应力之后的饱和漏电流值ID-SC除以fresh 状态下的饱和漏电流值ID-Initial,其中饱和漏电流均从所测的输出特性曲线(VGS=5 V 和VDS=2 V)中提取。从图8(a)可知,当短路应力VGS越大时,VTH的漂移量就越多,其中VGS=6 V 时,VTH的最大退化量为+0.65 V;VGS=4 V 时,VTH最大退化量为+0.31 V。与之对应的是图8(b),饱和漏电流会随着VGS的增大而加剧退化,当VGS=6 V 时,归一化的饱和漏电流ID-SC/ID-Initial为0.76;而VGS=4 V 时,归一化的饱和漏电流ID-SC/ID-Initial为0.91,ID-SC/ID-Initial越小,说明饱和漏电流退化越严重。

图8 DUT1、DUT2 和DUT3 分别在VGS 为6 V、5 V、4 V,VDD=60 V 重复短路应力前后的电学特性变化

如前所述,引起器件饱和漏电流衰退的主要原因之一是VTH右漂,而器件的栅下区域主导着VTH的变化。本文从p-GaN HEMT 器件的Metal/p-GaN/AlGaN/GaN 栅结构能带理论出发并结合重复短路应力条件,提出如图9 所示的能带模型。图9(a)为器件在无短路应力条件下的栅极结构能带图,由于VGS=0 V,故AlGaN/GaN 界面附近的2DEG 量子阱在费米能级EF以上,栅极区域正下方的沟道中并未积累电子,器件处于关断状态;其中由Metal/p-GaN 组成的肖特基结会在靠近p-GaN 一侧形成空间电荷区(Space Charge Region,SCR)。

图9 p-GaN HEMT 栅极区域的能带以及电荷的动态转移

器件处于短路应力下(例如VGS=4 V,VDD=60 V)的栅极结构能带如图9(b)所示。由于VGS=4 V,大于该器件的VTH,电子准费米能级EFn往上移动并靠近导带底EC,栅区域下方的AlGaN/GaN 界面附近的2DEG 量子阱将处于电子准费米能级EFn以下,栅下的沟道中积累电子,器件处于开启状态。由于VGS>VTH>0 V,AlGaN层的电子势垒高度将降低,从而导致栅下的电子势垒降低,大量沟道电子在热辅助的作用下将溢出2DEG量子阱从而进入AlGaN 势垒层;由于EFn上升将使得AlGaN 层的部分陷阱能级以及p-GaN/AlGaN 界面的部分界面陷阱能级低于EFn,而这些陷阱能级将会被溢出到AlGaN 势垒层的电子所完全填充,即AlGaN 层陷阱以及p-GaN/AlGaN 界面陷阱将俘获电子,如图9(b)的过程①所示,这将形成负的空间电荷区,对2DEG 沟道中的电子形成耗尽作用,导致VTH右漂。此外,未被陷阱俘获的电子将进入p-GaN 层的中性区并朝着栅金属方向自由扩散,如图9(b)的过程②所示,考虑到p-GaN 层中的电子扩散长度Ln至少为220 nm[10]和p-GaN 层中实际空穴浓度量级为1×1017cm-3[11],而EPC2051 器件的p-GaN 厚度仅为60~70 nm,故电子在p-GaN 中性区中发生复合的概率很小,且极易被靠近金属一侧的p-GaN 耗尽区中的电场加速至栅金属中,即为图9(b)中的过程③。在短路过程中,由于从2DEG 量子阱溢出到AlGaN 势垒层的电子特别多并且是一个持续过程,故经历过程③的电子将越来越多,这与短路过程中IG越来越大是一致的。

3.3 恢复特性及其机理

为了进一步研究陷阱相关的物理机制,本文选取了2 颗新的器件,重点研究器件的恢复特性,测试方案为:首先测试初始状态下的关键电学特性,随后将各个器件连续短路100 次后,测试各器件在短路应力后以及静置恢复5 min、30 min、1 h、2 h、5 h、19 h、19 h 后高温烘烤(10 min,160 ℃)、144 h、360 h 后的关键电学特性,其中恢复时间(Recovery time)均是相对于应力后的电学特性测试结束后的时间点而言。

首先采用较弱的应力条件,即VGS=4 V,VDD=60 V,该应力条件对应DUT4;图10(a)为DUT4 在100 次短路应力后的阈值电压恢复量,图10(b)反映了DUT4在100 次应力后的归一化饱和漏电流恢复特性,其中100 次应力后的测试数据点对应恢复时间为零的数据点,即△VTH=+0.4 V 和ID-SC/ID-Initial=0.92。通过图10(a)(b)可以发现,在100 次应力之后到静置2 h 这段时间内,阈值电压与饱和漏电流均在持续恢复;而静置2 h到5 h 再到19 h 这段时间内,器件的VTH几乎没有恢复,△VTH稳定在+0.2 V,ID-SC/ID-Initial稳定在0.95 左右。从图9(b)可知,VTH右漂主要是由于AlGaN 势垒层陷阱与p-GaN/AlGaN 界面陷阱俘获电子引起的,而这些陷阱有着不同的能级位置,能级位置的不同将使得陷阱释放电子的时间不同,最终影响VTH的恢复快慢;在100 次应力之后到静置2 h 这段时间内,VTH在较短的时间内有持续的恢复量,这很可能与AlGaN 层和p-GaN/AlGaN 界面的浅能级陷阱有关,比如从p-GaN层扩散到AlGaN 势垒层的Mg 杂质[12];而深能级陷阱俘获电子后很难将电子释放出,会导致VTH长时间难以恢复。器件在静置2~19 h 这段时间内几乎不会恢复,故本研究将静置19 h 后的DUT4 进行高温烘烤,烘烤仪器为陶瓷加热夹具,以160 ℃的温度将DUT4烘烤10 min,烘烤结束后让器件加速散热,最后进行电学特性测试,即图10(a)中ΔVTH=+0.07 V 与图10(b)中ID-SC/ID-Initial=0.99(左边点)所对应的点;当高温烘烤DUT4 后,其阈值电压与饱和漏电流几乎完全恢复,这与AlGaN 势垒层和p-GaN/AlGaN 界面的深能级陷阱有关,被深能级陷阱所俘获的电子将会从高温烘烤中获取足够的能量,从而提前被深能级陷阱释放掉,最终加快了VTH的恢复。

图10 DUT4 在连续100 次应力后的动态恢复过程

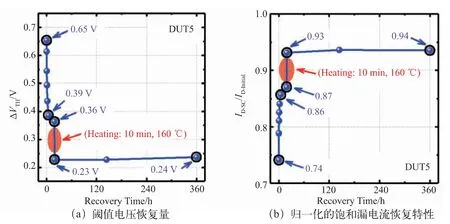

其次采用了苛刻的应力条件,即VGS=6 V,VDD=60 V,该应力条件对应DUT5;图11(a)为DUT5在100 次短路应力后的阈值电压恢复量,图11(b)反映了DUT5 在100 次应力后的归一化饱和漏电流恢复特性。可以发现在100 次应力之后到静置5 h 这段时间内,VTH与ID-SC/ID-Initial都在持续恢复;而静置5 h 再到19 h 这段时间内,VTH与ID-SC/ID-Initial几乎没有恢复。当DUT5 在静置19 h 后,采用与DUT4 同样的高温烘烤方案对DUT5 进行高温烘烤并记录烘烤后的测试点,即图11(a) 中ΔVTH=+0.23 V 与图11(b)中ID-SC/ID-Initial=0.93 所对应的点,高温烘烤的确加快了VTH与ID-SC/ID-Initial的恢复,但并未恢复到初始状态,故让DUT5 继续静置恢复。当DUT5 静置360 h 后,VTH仍没有恢复到初始状态,比初始状态下的VTH高0.24 V,ID-SC/ID-Initial也只有0.94。

图11 DUT5 在连续100 次应力后的动态恢复过程

由于在瞬态开关过程中,高注入电流和高电场会导致大量高能载流子(热电子)的产生,常见的硬开关事件会诱发热电子的产生[13],短路事件比硬开关事件更为严重,短路应力条件具有更高的注入电流、更强的电场以及更长的应力时间,本研究认为在短路过程中产生热电子的概率较高。当器件处于苛刻的短路应力条件下时(VGS=6 V,VDD=60 V),其异质栅能带如图12 所示;由于VDD电压几乎全降在器件的栅边缘到漏电极之间,将在器件的栅边缘附近产生极高的尖峰电场[14]。当大量的电子从源极漂移到漏极时,由于栅边缘附近存在极高的尖峰电场,途经栅极区域正下方的电子很容易被该处的强场加速成为热电子,部分热电子将轰击p-GaN/AlGaN 界面,造成永久性的缺陷(例如Ga 空位[15],表现为负电特性),如图12 的过程②所示,热电子诱导的p-GaN/AlGaN 界面新缺陷将对栅下2DEG 沟道中的电子形成永久性的耗尽作用,进而导致DUT5 的VTH不可恢复,最终导致IDsat永久退化。

图12 p-GaN HEMT 在苛刻短路应力条件下的异质栅能带

4 结论

本文基于重复短路应力条件下器件阈值电压与导通电流的退化特性及其动态恢复特性,结合Metal/p-GaN/AlGaN/GaN 异质栅能带理论,发现并分析了p-GaN HEMT 器件阈值电压VTH的可恢复性退化与永久性退化的机理。当器件处于较弱的短路应力下时,能级位于EFn以下的AlGaN 势垒层陷阱与p-GaN/AlGaN 界面陷阱将被溢出2DEG 量子阱的电子所填充,造成VTH的可恢复性退化。然而,器件处于苛刻的短路应力下时(VGS=6 V,VDD=60 V),沟道电子数量倍增和AlGaN 电子势垒进一步下降将导致电子溢出更为严重,部分电子被栅边缘的尖峰电场加速成为热电子进而轰击p-GaN/AlGaN界面,形成界面缺陷(比如Ga 空位),造成VTH的永久退化(ΔVTH=+0.24 V),最终导致IDsat不可恢复。本文对评估当前主流的p-GaN HEMT 器件的安全工作能力具有参考价值,对进一步提高器件的可靠性具有指导意义。