用于电荷域ADC 的大摆幅电荷传输电路设计

2022-07-07庞立鹏潘福跃苏小波

庞立鹏,潘福跃,苏小波

(中科芯集成电路有限公司,江苏无锡 214072)

1 引言

流水线模数转换器(Analog-to-Digital Converter,ADC)广泛应用于需要高采样率和高分辨率的无线通信领域[1]。近年来,随着便携式终端产品的飞速发展,不仅要求ADC 具有高采样率和高分辨率,对其功耗也提出了较高的要求。基于开关电容电路的流水线ADC 分辨率达14 位,采样率超500 MS/s[2-3],但是其依赖于高增益带宽运算放大器,因此功耗较高。基于升压电荷转移(Boost-Charge Transfer,BCT)技术的电荷域流水线ADC 是一种不使用高增益和超宽带宽运算放大器的ADC[4-7],因此能够在实现高采样率和高精度的同时具备较低的功耗。要实现高速和高精度的电荷域流水线ADC,最核心的问题就是电荷信号的存储传输、比较量化以及加减运算等关键步骤在现有的CMOS 工艺条件下能够高效并精确地实现,因此必须开发一种适用于普通CMOS 工艺的高精度电荷信号传输电路。文献[5]中采用了一种具有代表性的电荷信号传输电路,但是由于信号传输管源漏电压差的限制,其传输信号摆幅受到较大的限制。

本文提出了一种基于普通CMOS 工艺的高精度大摆幅电荷传输电路,采用栅压自举技术,在实现高精度电荷传输控制的同时,具备较高的模拟输入摆幅。基于该电荷传输电路,采用0.18 μm CMOS 工艺设计了一款低功耗14 位200 MS/s 电荷域流水线ADC,并进行了流片和相应的测试分析。

2 栅压自举电荷传输电路设计

2.1 现有电荷传输电路

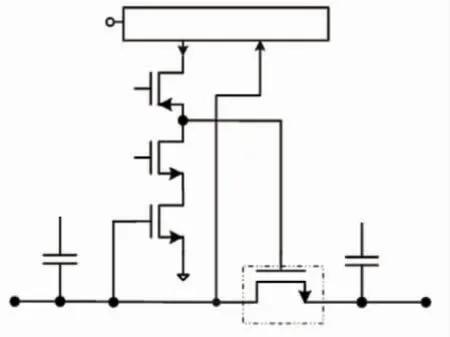

现有高效电荷传输电路实现方式如图1(a)所示,电荷信号传输MOSFET 管S 的栅极电压VG被连接到由MOSFET 管M1、M2 和M3 构成的运算放大器1 的输出端,运算放大器1 的输出端电荷传输之前,S 管处于关断状态,待传输电荷被存储在电容C1上。其工作电压波形如图1(b)所示,在t0时刻控制信号时钟Ck1和Ck1n的电压发生跳变,S 管漏端电压VNi突变到一个低电位,而源端电压VNo突变到高电位,运算放大器将会响应该变化并驱动S 管导通;在t1时刻,当VNi上升到VR时,VG逐渐降低到截止电压Vth,S 管重新关断,电荷传输过程结束,其中VR由共源共栅运算放大器的静态工作点确定。

当电荷传输结束时,MOSFET 管S 的源和漏两端保持了一个压差VDS,为保证电荷传输过程的安全可靠,VDS通常被设置在电源电压VDD的20%左右。在1.8 V 电源电压条件下,VDS为0.35~0.4 V,这就明显降低了电荷域ADC 流水线子级电路能处理的输入模拟信号摆幅范围。

2.2 栅压自举电荷传输电路设计

图1 的信号传输电路中,主要与输入信号摆幅相关的信号节点为电荷传输管MOSFET 管S 的栅、漏、源和衬底4 端。由于在实际电路中,源端和漏端分别属于前后相连的2 个子级电路,因此源端的电容是漏端电容的2N 倍(N 为源端所在子级电路的位数),导致电荷传输时漏端电压下降幅度是源端的2N 倍,因此电路的有效信号摆幅VA主要表现为漏端电压下降幅度,即:

图1 现有增强型电荷传输电路结构和工作电压波形

其中VCK1n为控制信号时钟CK1n的高电平电压。在低电压条件下,VDS没有优化空间;VCK1n电压为芯片的全局性基准电压,实际电路中其最大值受S 管栅端电压限制,较难达到理论最大值VDD。因此,要增大信号摆幅,必须克服VDD对VCK1n电压的限制。

为克服VDD对摆幅的限制,本文提出了一种采用栅压自举技术的电荷信号传输电路,其电路结构如图2 所示。采用栅压自举技术(即图2 中的栅自举增压电路),在电荷传输时将S 管栅端电压抬高一个VDD电压,这样VCK1n的上限可以提高到VDD,从而增加BCT的信号摆幅。

图2 栅压自举电荷传输电路结构

当进行电荷传输时,栅压自举增压电路处于增压状态,电荷传输MOSFET 管的栅极为高电平VDD+VNi,处于导通状态;当电荷传输结束后,栅压自举增压电路处于充电状态,S 管的栅极接地,处于关断状态。

通过采用栅压自举技术,VCK1n被提高到V′CK1n,达到理论上的上限VDD,由此BCT 电路的信号摆幅V′A增加了V′CK1n-VCK1n。

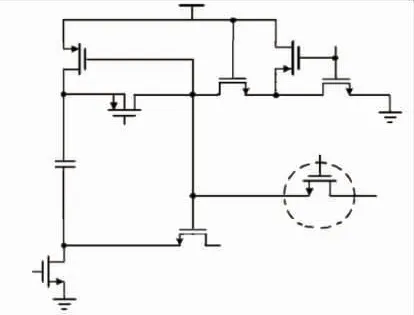

本文设计的栅压自举增压电路的结构如图3 所示。当时钟Ck1为高电平时,MOS 管Mb2、Mb6、Mb4和Mb1 导通,Mb7 截止,电容Cb1开始充电至两端电压接近电源电压VDD,并存储VDD×Cb1的电量,栅压自举增压电路处于充电状态;当时钟Ck1由高变低时,MOS 管Mb2、Mb6 截止,而Mb7 和Mb4 导通,电源开始对结点的对地寄生电容充电,使结点电压Vboost升高,从而使Mb1 截止,Mb5 和Mb3 导通,输入信号通过Mb3 抬升电容Cb1下极板电压直到其值等于输入电压VNi;由于电容Cb1上存储的电荷在时钟Ck变化过程中没有放电回路,存储在其上的电荷保持不变,电容Cbl上极板的电压就会同步上升,直到其值等于VDD+VNi,实现了栅压自举功能,栅压自举增压电路处于增压状态。

图3 栅压自举增压电路结构

3 14 位200 MS/s 电荷域流水线ADC 的设计和测试结果

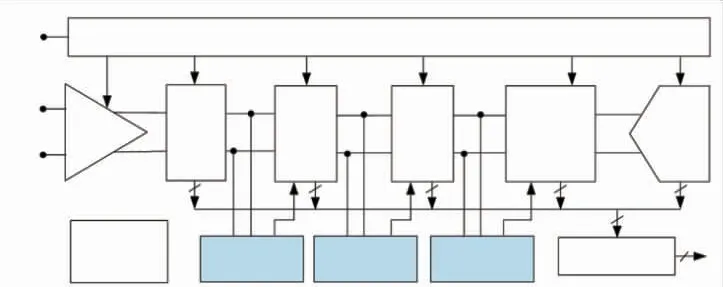

基于第2 节提出的栅压自举电荷信号传输电路,本文设计了一款14 位200 MS/s 电荷域流水线ADC,其架构如图4 所示。14 位电荷域流水线ADC 包括1个高速低失真采样保持电路、3 个2.5 位电荷域子级、5个连续的1.5 位电荷域子级和1 个3 位Flash 级。输入的差分模拟电压信号Vin和Vip分别通过采样保持电路进行采样并转换为电荷域信号Qin和Qip;通过8 个电荷域子级和最终Flash 级对Qin和Qip进行逐级处理。数字校正逻辑从所有子级获得22 位量化输出,并生成最终的14 位输出码。在14 位电荷域流水线ADC中,采用不交叠的两项时钟控制共模电荷补偿电路。在前4 级流水线之间分别采用了前馈电荷补偿技术来实时补偿因输入电荷共模电平所造成的电荷误差。

图4 14 位电荷域ADC 结构

该ADC 采用1.8 V IP6M 0.18 μm CMOS 工艺设计和流片,电路模块布局如图5 所示。核心部分包括采样保持电路和电荷域流水线子级;占空比调节/控制电路和数字编码电路在版图底部,共模电荷控制/前馈电路在顶部,带隙基准和缓冲放大器在右侧,电路尺寸约为2.2 mm×1.4 mm。

图5 14 位200 MS/s ADC 芯片布局

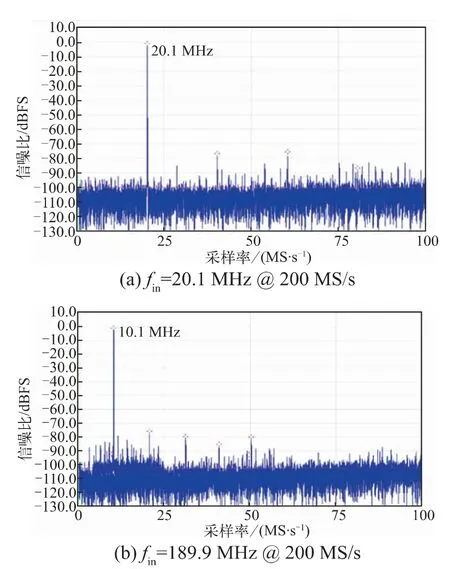

在200 MS/s 采样速率下,输入频率为20.1 MHz和189.9 MHz 时所测得的频谱如图6 所示。

图6 本论文提出的ADC 频谱

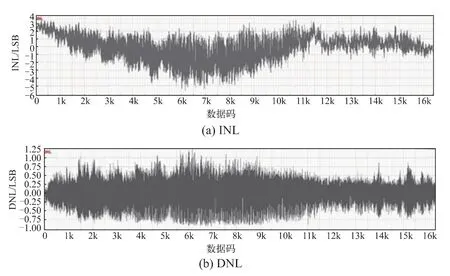

输入频率为20.1 MHz 时,信噪比(Signal-Noise Ratio,SNR) 为 64.5 dBFS, 无 杂 散 动 态 范 围(Spurious-Free Dynamic Range,SFDR)为76.3 dBc,信噪失真比(Signal-to-Noise and Distortion Ratio,SNDR)为65.8 dBFS;输入频率为189.9 MHz 时,SNR 为61.7 dBFS,SFDR 为72.6 dBc,SNDR 为61.3 dBFS。ADC 非线性测试结果如图7 所示,其最大积分非线性误差(Integral Nonlinearity,INL)为+3.43~-5.52 LSB,最大微分非线性误差(Differential Nonlinearity,DNL)为+1.23~-0.83 LSB。

图7 本论文提出的ADC INL 和DNL 测试结果

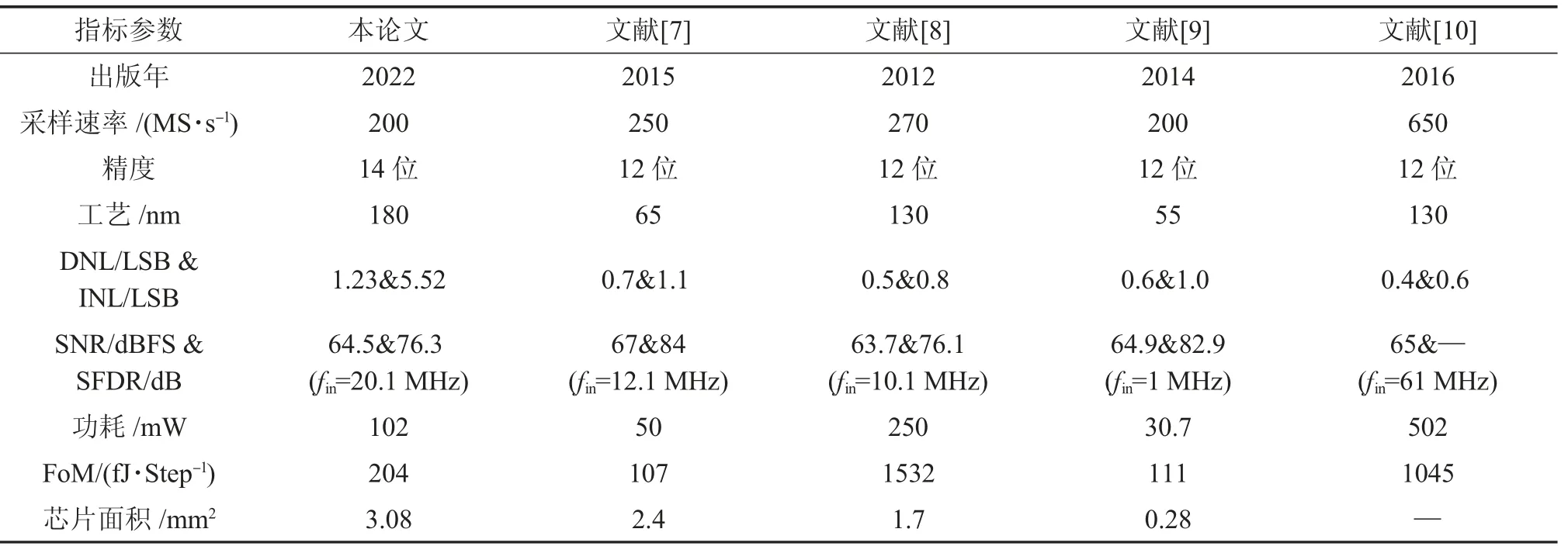

本文实现的ADC 样品测量结果与近年来报道的高速ADC[6-9]性能对比如表1 所示。基于所提出的共模电荷补偿电路的14 位200 MS/s 电荷域ADC的品质因数(FoM)为204fJ/Step,优于文献[8,10]中ADC 的FoM。

表1 性能对比

4 结论

本文在现有电荷传输电路的基础上,采用栅压自举技术,在实现高精度电荷传输控制的同时具备较高的模拟输入摆幅。基于该技术,采用0.18 μm CMOS工艺设计并实现了一款14 位200 MS/s 电荷域流水线ADC。在189.9 MHz 信号输入和200 MS/s 采样率下,该ADC 实现了61.7 dBFS 的SNR 和72.6 dBc 的SFDR。ADC 内核功耗仅为102 mW,面积为3.08 mm2。实验结果表明,本文提出的共模电荷补偿技术能够较好地抑制输入共模电荷变化对ADC 性能带来的影响,实现高速和低功耗流水线ADC。