一种SSD 的设计与测试方法研究及实现

2022-07-07张梅娟侯庆庆

沈 庆,张梅娟,侯庆庆,张 磊

(中国电子科技集团公司第五十八研究所,江苏无锡 214072)

1 引言

21 世纪以来,传统机械硬盘作为目前的主流存储设备,由于其本身结构和存储方式的局限,已成为制约计算机整体性能的瓶颈。与传统机械硬盘相比,固态硬盘(Solid State Disk,SSD)有着读写速度快、读延迟小、无噪音等天然优势[1-5],使其逐渐代替机械硬盘。

SSD 主要的存储介质为NAND Flash,其控制器将复杂的NAND Flash 接口转化为通用标准接口,处理器仅需通过总线接口就可以对NAND Flash 进行相应的读写操作。为提高硬盘存储容量和数据存储速度,文献[6-7]采用多个控制器来操作多片NAND Flash存储芯片,读写速率和存储容量得到了提高,但其缺点在于控制器之间数据同步问题比较明显,控制器的性能不够理想。因此,本文利用单个控制器,使用总线数据扩展技术,并行控制多片NAND Flash 芯片;在架构方面,利用多通道并行策略和闪存阵列管理技术,提高数据传输效率;在ECC 数据校验方面,采用基于多维TPC 编解码方案,进一步提高其纠错能力。

由于SSD 与传统机械硬盘的存储介质与存储原理不同,使得SSD 的设计方法与测试方法也与传统机械硬盘有所不同,传统用于测试机械硬盘的硬盘测试工具,如HD Tune、MHDD 等软件,已不能很好地适用于测试SSD。为了验证本文所设计的SSD 控制方案在实际应用中的价值,利用专业测试软件及各种测试环境对其进行了性能测试。

2 硬件设计

2.1 SSD 性能指标

设计电路为一款集成NAND Flash 的SATA 控制器,采用塑封SiP 结构,电路内部包含SATA 固态硬盘控制器、4 片NAND Flash、1 片SPI Flash。SATA 固态硬盘控制器支持SATA 接口,48 位地址,兼容ATA/ATAPI-8 标准,具体的硬件参数及性能指标见表1。

表1 电路主要功能与性能指标

2.2 SATA 控制器架构

SATA 固态硬盘控制器包括系统处理单元(SPU)、存储管理单元(SMU)、通道管理单元(CCU),SATA 固态硬盘控制器系统结构如图1 所示。

图1 SATA 控制器系统结构框图

SPU 负责与主机通信,且与SMU 模块进行命令与数据交互,主要包含1 个32 位CPU,处理SATA 协议的系统应用,搭载SPI、JTAG、UART 低速外设。其中,SPI 外接4 MB 的SPI Flash 用于存储固件程序,可外接SPI NOR Flash,速率可达10 MB/s;JTAG 有2路,用于测试、下载或调试程序等功能;UART 有2 路,支持固件信息的打印和调试。

SMU 主要负责控制器与NAND Flash 间的地址映射管理;采用混合映射方法,将页(Page)、块(Block)的地址进行映射,主要负责主机读写数据时各个映射表的建立,以及硬盘异常掉电时各个映射表的恢复。

CCU 包含一个8 位CPU,其指令周期固定为2 个时钟周期,寄存器访问空间为256 B;CCU 通过DMA与SMU 进行数据交互,CCU 包含纠错单元和加扰单元,并且拥有4 个通道,每个通道最多可包含8 块片选,用于控制外部Flash,完成与NAND Flash 的交互。

2.3 NAND Flash 接口定义

NAND Flash 主要用于存放数据,综合考虑容量与性能,SATA 接口可以灵活配置NAND Flash 类型以及数量。如图2 所示,NAND Flash 采用8 位宽或16 位宽的总线,使用命令、地址、数据总线复用策略,完成命令与地址的写入以及数据的传输。NAND Flash 芯片有CLE、ALE、CE、RE、WE、WP、R/B、I/O 8 个控制信号,负责执行相关协议,达到与NAND Flash 交互的目的。

图2 NAND Flash 的外部接口

3 Flash 阵列与ECC 校验

3.1 闪存阵列管理技术

单片NAND Flash 颗粒的容量有限,读写速度也受到限制,因此无法满足大容量存储、高速读写的要求,为了在最大程度上提升整体容量和性能,需要重新设计原来单片NAND Flash 颗粒的控制器。闪存阵列管理技术主要通过优化闪存阵列结构来提高数据平行性,从而提高SSD 的读写性能。具体方法是将整个NAND Flash 存储空间划分为多个Die,各个Die 之间利用时分复用共享一条I/O 总线,NAND Flash 控制器在操作过程中采用流水线的方式,在不同时刻对不同Die 进行片选并编程,提高总线的利用率[8]。

一种大容量Flash 阵列的构建方式如图3 所示,Flash 阵列由行和列构成,同一行上的所有Flash Die共用控制信号线,控制信号线主要包括地址锁存信号ALE、命令锁存信号CLE、读使能信号RE、写使能信号WE 等。该Flash 阵列的构建特点是共用控制信号与片选信号,减少引脚数量。每次片选有效,将选中所有的Flash 进行操作,每次传输的数据都能均分到阵列的每一片NAND Flash 上面,能实现大数据量的快速读写操作,通过扩展各片NAND Flash 位宽,达到高速数据传输的效果,适用于大量数据的高速读写需求。

图3 Flash 阵列并行存储结构

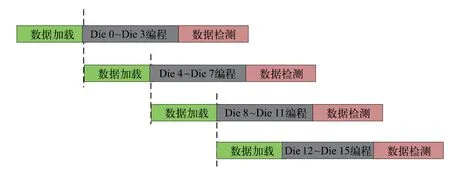

类似计算机中的流水线操作原理,NAND Flash 在时间片上实现微观意义上的并行处理,NAND Flash 的写入操作可以分为加载操作、Die 编程操作、数据检测操作等。在通道内部使用流水线操作,当一片NAND Flash 进行编程时,其他芯片执行读写操作,在时间上实现通道内数据总线的复用,可缩短NAND Flash 阵列的等效操作时间。

图4为Flash 流水线操作示意图,在任一时间片上总有若干操作在同时进行,即在时间上实现了复用,整体的持续数据写入速率就等于NAND Flash 芯片的数据加载速率。同时,通道内每增加一个片选信号和busy 信号,容量即可成倍增加,使用流水线操作后,通道内数据线得到充分使用,从而实现读写性能的大幅度提升。

图4 Flash 流水线操作示意图

3.2 ECC 数据校验技术

传统用于SSD 控制器的ECC 方案大都采用BCH码以及LDPC 码[9],同时配合硬解码算法以及不超过3位的软解码算法。尽管大多数SSD 控制器采用了BCH 码以及LDPC 码,但是前者存在纠错能力弱的问题,后者在硬件解码过程中会产生较高的功耗,同时在高速应用方面表现较差。

3.2.1 基于TPC 的编码方案

受上述启发,本文将研究多维的Turbo 乘积码(TPC)在SSD 控制器中的应用。多维TPC 具有更优的汉明距离、较低的误码平底,其解码算法具有较高的内在并行度[10]。本文设计的数据校验方法能够配置成2D/3D TPC,其结构分别如图5、图6 所示。

图5 2D TPC 结构

图6 3D TPC 结构

对于2D TPC,未编码消息为一个(Kx,Ky)方阵,其编码过程如下:

1)对每一行消息进行编码,共产生Ky个子码字;

2)对生成码字方阵的每一列进行二次编码,共生成nx个子码字。

对于3D TPC,其编码过程如下:

1)未编码的消息将会被列成一个(Kx,Ky,Kz)的立方体,包括Kz个(Kx,Ky)平面,在编码过程中,首先对每个码字平面采用2D TPC 的编码方法,当所有码字平面都编码完成后,生成一个(nx,ny,Kz)的立方体,该立方体在z 方向共有(nx,ny)个二进制序列。

2)对每个z 方向上的二进制序列进行编码,最终形成一个(nx,ny,nz)的子码字立方体。对于本文采用的2D/3D TPC 编码方案,采用将部分信息比特设置0 的方法来达到对多种码率的支持,多维TPC 每个维度上的编码候选方案为BCH 码和汉明码等。

对于上文中所描述的TPC 编码,将第一次编码称为外码编码,而剩余维度的编码称为内码编码。为了进一步提升解码性能,对抗存储系统中的突发错误,在内码的编码过程中还将融入合适的数据交织机制,从而将突发错误打散到各个子码字中,使得每个子码字中的错误数目比较平均,避免错误集中在一个或几个子码字中。

3.2.2 基于TPC 的解码方案

TPC 的解码算法一般是基于迭代的解码算法,外码的解码结果传递给下一个维度的内码,其解码结果再传递给下一个维度的内码,依次类推,直到最后的解码反馈给外码,这样一次迭代完成。在一次迭代过程中,传统的方法需要将维度内部的所有子码字都解码一次,这样会带来较大的计算复杂度,进而带来较大的解码损耗。

对于本文所采用的解码算法,在一次迭代中,只有外码的子码字会被解码。基于解码结果,首先定位有错误的子码字位置,对于所有其他维度的内码而言,只解码与错误位置相关联的子码字,这样在一定程度上降低了计算复杂度;然后生成列表,该列表包含可能的错误向量,对于每个错误向量,翻转对应解码进行输出,并将其传递到下一个维度对应的解码运算中。

对应的解码算法如图7 所示,第一个维度的软解码涉及到所有子码字,同时将确定没有能够正确解码的子码字,第二和第三个维度只涉及到这些没有正确解码的子码字。这样可以从算法上降低解码技术复杂度,从而降低最终解码器的硬件功耗。

图7 3D TPC 的软解码算法基本架构

4 SSD 测试方案与结果分析

4.1 测试平台的设计

测试平台的构建主要包括热流罩、主机、直流电压源、TXBENCH 测试软件、Bridge 转接桥和SATA 数据线等,具体介绍见表2。

表2 SSD 测试工具及作用

4.2 固件加载

在性能测试前,需对固件进行测试及验证工作,具体步骤如下。

1)认盘:将硬盘写保护接口打开,然后将硬盘通过SATA 接口或Bridge 接口接入主机;使用固件烧写软件识别硬盘。

2)烧写固件:在Public Setting 界面,按照要求进行固件信息的选择,烧写相应版本固件。

3) 格式化硬盘:烧写固件完成后断电重启,对SSD 进行格式化操作。

4.3 测试方案

实验环境下的温度控制通过热流罩实现,热流罩可以提供-60~225 ℃的温度且可靠性高。测试主要目的是在不同温度下测试SSD 读写速率,具体测试流程如下。

1)SSD 插入SATA 接口,不使用Bridge 转接桥,给SSD 供直流电,启动主机。

2)常温下测试板卡的读写速率,测试结束后断开电源和SATA 线。

3)热流罩设置-55 ℃低温,到达指定温度且持续1 min 后,连接SATA 线给SSD 板卡供电;运行测试软件,记录读写速率;测试结束断开SATA 线和电源。

4)温度调整到25 ℃,持续1 min 后,温度调整到125 ℃,到达125 ℃后持续1 min,连接SATA 数据线,给SSD 板卡供电;运行测试软件,记录读写速率。

4.4 测试结果与对比

4.4.1 测试结果

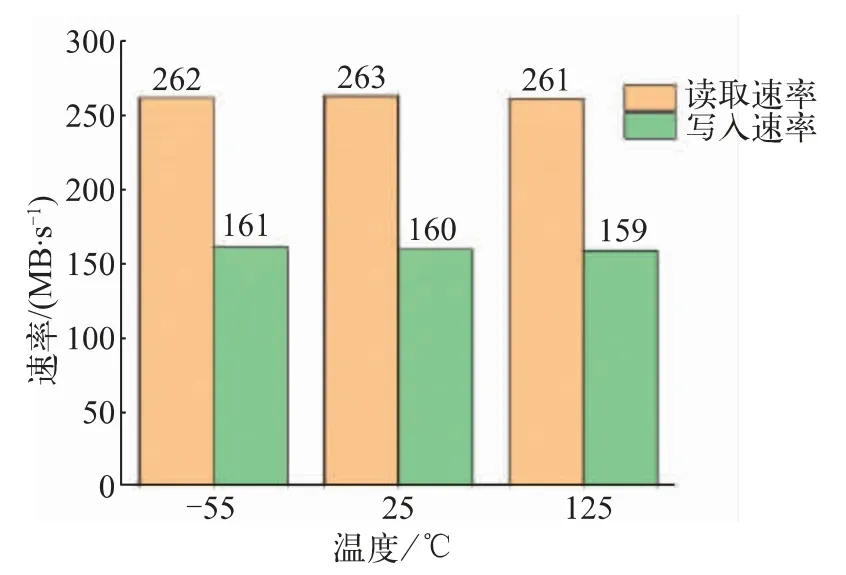

在不同温度下测试NAND Flash 芯片,多次测试结果平均值如图8 所示。

图8 SSD 读写速率

从图8 可知,本款SSD 在常温(25 ℃)、低温(-55 ℃)、高温(125 ℃)情况下时,读取速率均在260 MB/s 左右,写入速率在160 MB/s 左右,可见本款SSD 在读取速率上较稳定,环境适应性强,总体上满足了对读取和写入速率的设计要求。

4.4.2 性能对比

将本设计方案读写测试结果与其他文献NAND Flash 控制器设计方案结果进行对比,结果如表3 所示。

表3 不同方案读写性能对比

文献[6]采用多片NAND Flash 并行结构扩展数据位,双数据缓冲区,读取速率较高但写入速率有限。文献[7]使用流水线技术,在通道内实现数据总线复用,但是仅包含2 个通道,且每个通道内只包含1 个Die,因此整体读写速率较低。本设计方案采用多片NAND Flash 并行的阵列管理技术,多级流水线操作,包含最多4 个通道,每个通道可最多支持8 个Die,因此整体读写速率均有一定的提高。

5 结论

总体设计上,本文使用单个控制器,利用总线数据扩展技术,进而并行控制多片NAND Flash。在架构方面,利用多通道并行策略和闪存阵列管理技术提升数据传输效率;在ECC 数据校验方面,采用基于TPC编解码方案提高其纠错能力,有效保证数据可靠性;在固态硬盘读写测试方面,使用现有SSD 专业测试软件以及各种测试环境对其进行性能测试,试验结果表明,本款SSD 整体性能满足设计要求,具有一定的实用价值。