联动薄膜电容式压力敏感芯片研制

2022-07-02揣荣岩杨宇新

张 冰,揣荣岩,杨宇新,张 贺,李 新

(沈阳工业大学信息科学与工程学院,辽宁沈阳 110870)

0 引言

随着信息技术和物联网技术的快速发展,对微型传感器的需求不断增加[1],相较于压阻式压力传感器,MEMS电容式压力传感器具有灵敏度高、功耗低、温度特性好等优势[2-4],因此在电子、航空航天、生物医疗等领域得以广泛应用[5-6]。这些领域的待测压力值通常都比较小,均在一个大气压(101.325 kPa) 以下,要对如此微小的压力实现准确测量,不仅需要保证传感器具有很高的灵敏度,还对其线性度和线性范围有着很高的要求。

MEMS电容式压力传感器通常采用平行板电容器结构,主要由可动极板,固定极板和介质层组成,可以工作在非接触模式和接触模式下[7-8]。工作在非接触模式下的电容式压力传感器,可动极板受力发生形变使得2个极板间有效间隙发生改变,但可动极板与固定极板始终保持一定距离,这种非接触式的电容式压力传感器的灵敏度不高,且线性范围小,具有严重的非线性[9]。而接触式电容压力传感器,在工作范围内,允许可动极板与固定极板上的绝缘层接触,通过接触面积的改变来实现对压力的测量,由接触面积引起电容值的变化要远大于由极板间隙对电容值的影响,因此相较于非接触电容式压力传感器,接触电容式压力传感器具有更高的灵敏度和更好的线性[7-10]。但受结构尺寸的影响,接触电容式传感器随加载压力产生线性形变对应的压力范围比较小,存在线性度与灵敏度矛盾突出的缺点,限制了其应用与开发。

在接触式电容压力敏感结构基础上,为提高电容式压力传感器的性能,研究人员提出了一些新型结构,如双凹槽结构的接触式压力传感结构[11],基于缓冲块的电容传感结构[12]和底部电极凸球冠形状的接触电容压力传感结构[13],但这些结构复杂,工艺难度大,很难实现批量化生产。

为此,针对目前MEMS电容式压力敏感结构中存在的一些问题,本文对联动薄膜电容式压力敏感结构[14](capacitive pressure sensitive structure with linkage film,CPSSLF)进行研究和实验试制,在结构中利用可动的下极板来替代接触电容式压力敏感结构中不可动的下极板,同时采用带有残余压应力的感压上极板,有效扩大线性响应范围并提高线性度,并且通过将7个压力敏感结构并联的方式,解决压力传感器灵敏度和线性度之间的矛盾。

1 结构设计和理论分析

1.1 结构和工作原理

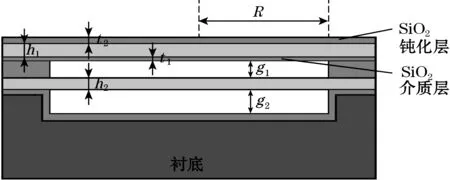

图1为联动薄膜电容式压力敏感结构示意图,主要由衬底、一对可动的电极板、密封腔体、介质层和钝化层构成。当有压力作用于上极板时,上极板因受力发生弯曲形变,随着压力的增大,上极板会与下极板上的介质层接触,当压力继续增大时,由于下极板也是可动的感压结构,极板间的接触实现力的传递,使得下极板也发生弯曲形变,并随着上极板的运动而运动,从而调节上极板的形变状态,形成联动的效果,如图1(b)所示。这种联动薄膜电容式压力敏感结构可使电容值的增长速率变得稳定,因此可以扩大传感器的线性工作区域范围,提高线性度。

(a)无压力作用时,CPSSLF示意图

由图1可知,整个感压上极板是一个由3层薄膜复合而成的多层膜结构,其中钝化层位于上电极的上方,用于对整个结构进行保护,以此来提高传感芯片的可靠性能;介质层位于上电极的下方,以确保在接触模式下2个电极板始终绝缘。当加工这种多层膜时,由于生长环境和后处理工艺的影响,导致薄膜中不可避免地会存在残余应力[15],而残余应力不仅会使得薄膜的机械性能发生改变,薄膜弯曲程度变化,还会导致压力敏感结构的输出存在差异。相较于无应力的感压上极板,当感压上极板中存在压缩的残余应力时,具有更好的线性响应,可进一步扩大线性工作范围[16]。

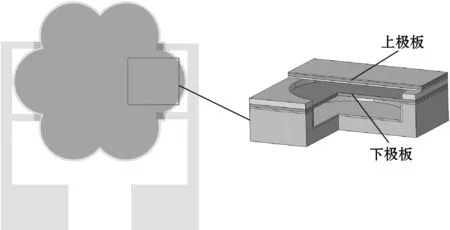

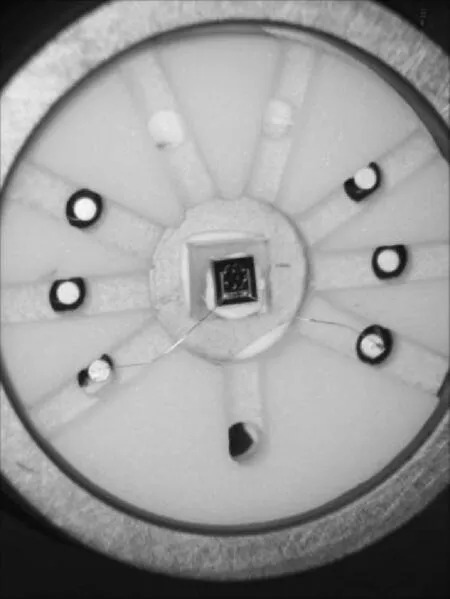

为提高灵敏度,实际试制的压力敏感芯片采用图2中的设计,为7个半径为110 μm的基本单元并联在同一块芯片区域内。

图2 联动薄膜电容式压力敏感芯片示意图

1.2 理论分析

对于图1所示的压力敏感结构,总电容(C)由可动极板构成的腔体电容(Ccavity)、腔体外围的边缘电容(Cedge)和寄生电容(Cpara)并联而成。寄生电容主要由上下极板边缘之外分布的电场引起的电容,由于两平行极板的间距远远小于极板直径,极板间电容值要远大于寄生电容值,因此寄生电容可以忽略。则电容满足下式:

C=Ccavity+Cedge

(1)

根据高斯数值积分,可以得到当感压上极板受到压力作用时,2个电极之间的电容Ccavity如式(2)所示[14]:

(2)

式中:ε0为真空介电常数;εa为真空的相对介电常数;εi为介质层的相对介电常数;g1为上腔体高度;t1为介质层厚度;w1(r)为位于上极板半径为r的圆周(0 由于在极板边缘存在支撑结构,边缘电容对加载压力为非敏感电容,在整个受力过程中始终保持恒定,因此: (3) 式中:A为边缘极板间覆盖的有效面积;d为边缘极板间间距,d=g1+t1。 (4) 对于非接触模式下的感压上极板,这里采用简化计算方法,将三层薄膜的杨氏模量和泊松比等效为一种材料的特性,因此可以得到存在残余内应力的上极板中心处的挠度为[16]: (5) D由式(6)求得: (6) 式中:E为杨氏模量;v为泊松比。 基于有限元方法对图1所示的压力敏感结构进行分析,所使用的材料及结构参数如表1所示。图3为-80 MPa预应力和无内应力的感压上极板中心处位移与加载压力的关系。由图3可以看出,在相同压力下,-80 MPa预应力的感压上极板中心处的位移要大于无内应力的感压上极板中心处的位移,说明相较于无内应力的感压上极板,存在压应力的感压上极板会变得更软,受到相同压力时的位移更大,因此可以与下极板更早接触。由图3可知,当-80 MPa预应力的感压上极板的位移等于腔体高度(0.6 μm)时,2个极板开始接触,此时对感压上极板所施加的压力为10 kPa,即接触压力为10 kPa,而无内应力的感压上极板的接触压力为30 kPa。 表1 CPSSLF的结构参数 μm 图3 CPSSLF的感压上极板无内应力和存在预应力时,上极板中心处位移与压力的关系 图4为CPSSLF的感压上极板无内应力和存在-80MPa预应力时,输出电容与压力之间的关系,从图4可以看出,相较于无内应力的压力敏感结构,-80MPa预应力的压力敏感结构的输出电容会更早进入线性,可以提前近20kPa,并且线性区的压力范围没有减小。虽然,无内应力的压力敏感结构,通过减小上极板的厚度,也可以实现上、下2个极板早接触,但是,这种方法会使得线性压力工作范围大大减小,无法满足设计要求。 图4 CPSSLF的感压上极板无内应力和存在预应力时,输出电容与压力的关系 所设计的联动薄膜电容式压力敏感结构采用SOI材料(SOI A和SOI B),并利用干法刻蚀和硅硅直接键合技术相结合的方法进行制备。主要工艺步骤如下: (1)在双面抛光的单晶硅衬底上干法刻蚀形成凹槽,深度为5 μm,并热氧化一层1 μm厚的SiO2绝缘层,如图5(a)所示; (2)首先对衬底和SOI A 依次进行常规的标准清洗和兆声清洗以去除有机物、颗粒等杂质,然后通过键合设备(EVG 510),在真空条件下(真空度约为7.5×10-4mbar,1 bar=100 kPa)将SOI A顶层硅一侧与衬底硅进行预键合,之后在氧气氛围下进行高温键合(温度为1 100 ℃,时间2 h),从而形成封闭真空的下腔体,如图5(b)所示; (3)采用化学机械抛光对键合片的正面进行减薄,至原SOI的衬底硅剩余20 μm,然后通过湿法腐蚀将原SOI A的衬底硅去除干净,再干法刻蚀出腔体结构,如图5(c)所示; (4)对SOI B硅片进行热氧化,在SOI B硅片顶层硅表面形成一层0.3 μm厚的氧化膜来作为绝缘介质层,如图5(d)所示; (5)与第一次键合工艺相似,在清洗SOI B与键合片之后,通过键合设备在真空中将倒置的SOI B 与键合片进行预键合,然后进行高温键合,完成第二次键合工艺,实现上腔体的真空密封,如图5(e)所示; (6)将原SOI B的衬底硅和氧化层去除干净,仅留下原SOI B的顶层硅薄膜作为上极板,如图5(f)所示; (7)分别刻蚀出上极板和下极板的形状,如图5(g)所示; (8)利用等离子体增强化学气相淀积(PECVD)沉积一层500 nm厚的二氧化硅薄膜作为钝化层,该步骤中沉积温度为400 ℃,等离子体的射频功率为350 W,反应气体的气体流量控制在约60~70 mL/min,然后进行退火(条件为1 150 ℃下退火60 min),最终沉积得到所需残余应力的二氧化硅薄膜。再利用光刻技术对钝化层进行光刻形成引线孔,蒸铝并光刻形成金属布线,即可完成芯片制作,如图5(h)所示。 图5 主要工艺步骤 所试制的压力敏感芯片样品如图6所示,该芯片由7个如图1所示的基本单元并联构成。图6(a)为封装后的样品芯片,图6(b)为划片后压力敏感芯片,尺寸为1.3 mm×1.4 mm,在显微镜下可以观察到光的干涉图像(即牛顿环),如图6(c)所示,表明该样品在一个标准大气压下完全密封,并且处于接触模式。 (a)芯片封装 在室温条件下,对压力敏感芯片样品进行测量。测试设备如图7所示,主要包括:密封腔、真空泵、数字压力控制器和电容测试仪。将封装好的压力敏感芯片样品放置于密封腔内,电容测试仪(KEITHLEY3330 LCZ METER)与密封腔上的接线柱相连,打开真空泵对腔体缓慢抽气,通过数字压力控制器(CPC 6000)控制腔内压力,将一定大小的压力加载到压力敏感芯片的样品上开始测量。 图7 压力敏感芯片测试试验台 量程为80 kPa的压力敏感芯片测试结果如图8所示,当压力从0.01 kPa增加到80 kPa时,电容从13.89 pF增加到20.01 pF。 图8中输出电容与压力的关系曲线可划分为4个区域(非接触区、过渡区、线性区和饱和区)。当压力在0~10 kPa之间时,上极板不与下极板发生接触,此时输出电容存在严重的非线性,芯片处于非接触区;当压力为10 kPa时,上极板与下极板绝缘接触,之后便进入短暂的过渡区(10~20 kPa),此区域是向线性响应转变的过程,输出电容仍为非线性;当压力继续增加时,输出电容开始线性增长,进入线性区,但是即使是在线性区,当选取的压力范围不同时,非线性度也会不同,当压力在20~64 kPa范围内时,电容-压力曲线接近线性,非线性度为3.1%,灵敏度为0.057 pF/kPa;当压力大于64 kPa时,随着压力的继续增大,由于2个极板的接触面积的增加速率会受到尺寸的限制,电容的增长速率逐渐减缓,非线性度不断增加,芯片进入饱和区。通过控制压力源将压力从0.01 kPa增加到80 kPa,然后又从80 kPa减小到0.01 kPa,以此来测量压力敏感芯片的迟滞,测量得到的迟滞约为2.6%。 图8 测量得到的输出电容和压力的关系 由图8可知,压力敏感芯片的测量初始电容为13.89 pF,高于图4中仿真的初始电容0.59 pF,这是由于图4中的电容-压力曲线是单个压力敏感结构的腔体电容与压力的关系,而实际测量的压力敏感芯片的电容(Cchip)是由7个腔体电容(Ccavity)和边缘电容(Cedge)并联构成,即: Cchip=7Ccavity+Cedge (7) 当考虑以上因素并结合感压上极板中存在的残余应力进行仿真分析时,仿真结果就可以与实验结果较好的匹配,如图9所示,仿真与实际的满量程误差小于3%。 图9 有限元仿真得到的电容-压力特性曲线和测试得到的电容-压力曲线对比 对于本文提出并制作的联动薄膜电容式压力敏感芯片,通过采用带有残余压应力的感压上膜片,使得压力敏感结构具有更大的线性工作范围和更好的线性输出。通过将7个压力敏感结构并联的方式,改善压力传感器灵敏度和线性度之间的矛盾,实现了性能的综合提升。采用SOI硅片结合硅硅直接键合的技术进行实验制作,制作工艺简单。样品测试结果表明,在20~64 kPa 的线性工作区间下,灵敏度为0.057 pF/kPa,非线性度为3.1%。

2 工艺设计

3 测试

4 讨论

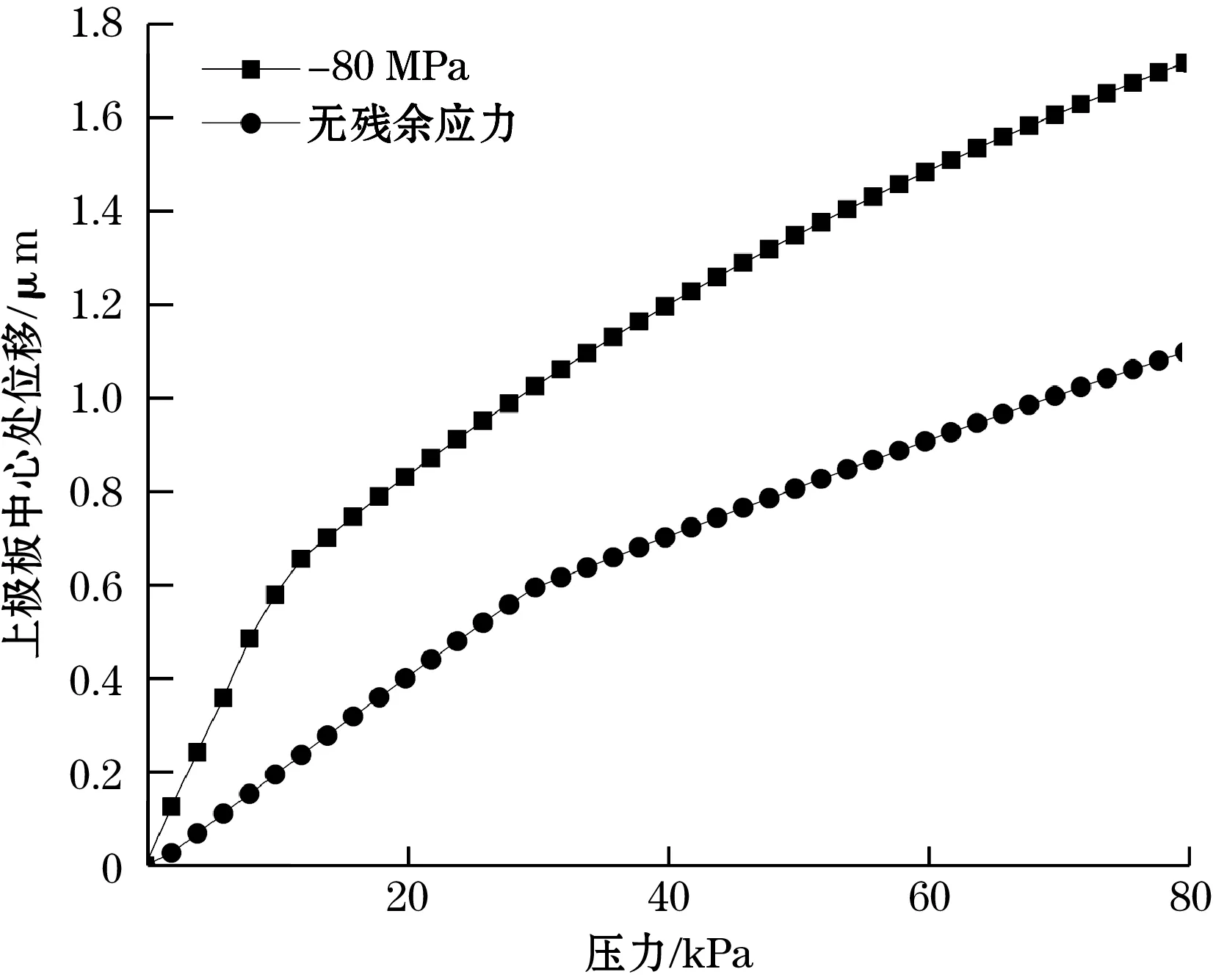

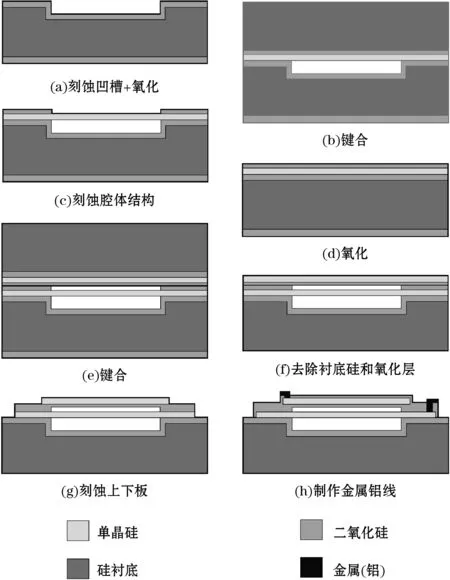

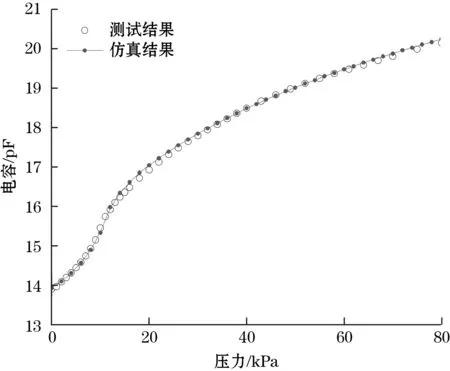

5 结论