基于FPGA 的参数可调多功能移位寄存器设计与实现

2022-06-23吴静瑜肖顺文雷小英陈韵文

吴静瑜,肖顺文,雷小英,郑 瑞,陈韵文

(西华师范大学 电子信息工程学院,四川 南充 637009)

0 引言

数字系统中,移位寄存器是常用的重要器件之一。除了作为移位寄存器外,还可用它来组成脉冲发生器、数据转换器、计数器和累加器等[1]。在数字电子电路设计过程中,固定参数的移位寄存器在使用上受到了一定限制,对参数可调的需求越来越高。FPGA 器件是专用集成电路中的1 种半定制电路,能有效地解决原有器件门电路数较少的问题,可重复编程,且在数字电路设计领域中应用广泛[2]。本文设计了基于FPGA 的参数可调的多功能移位寄存器,实现多参数多种移位方式的移位功能。

1 系统电路结构及工作原理

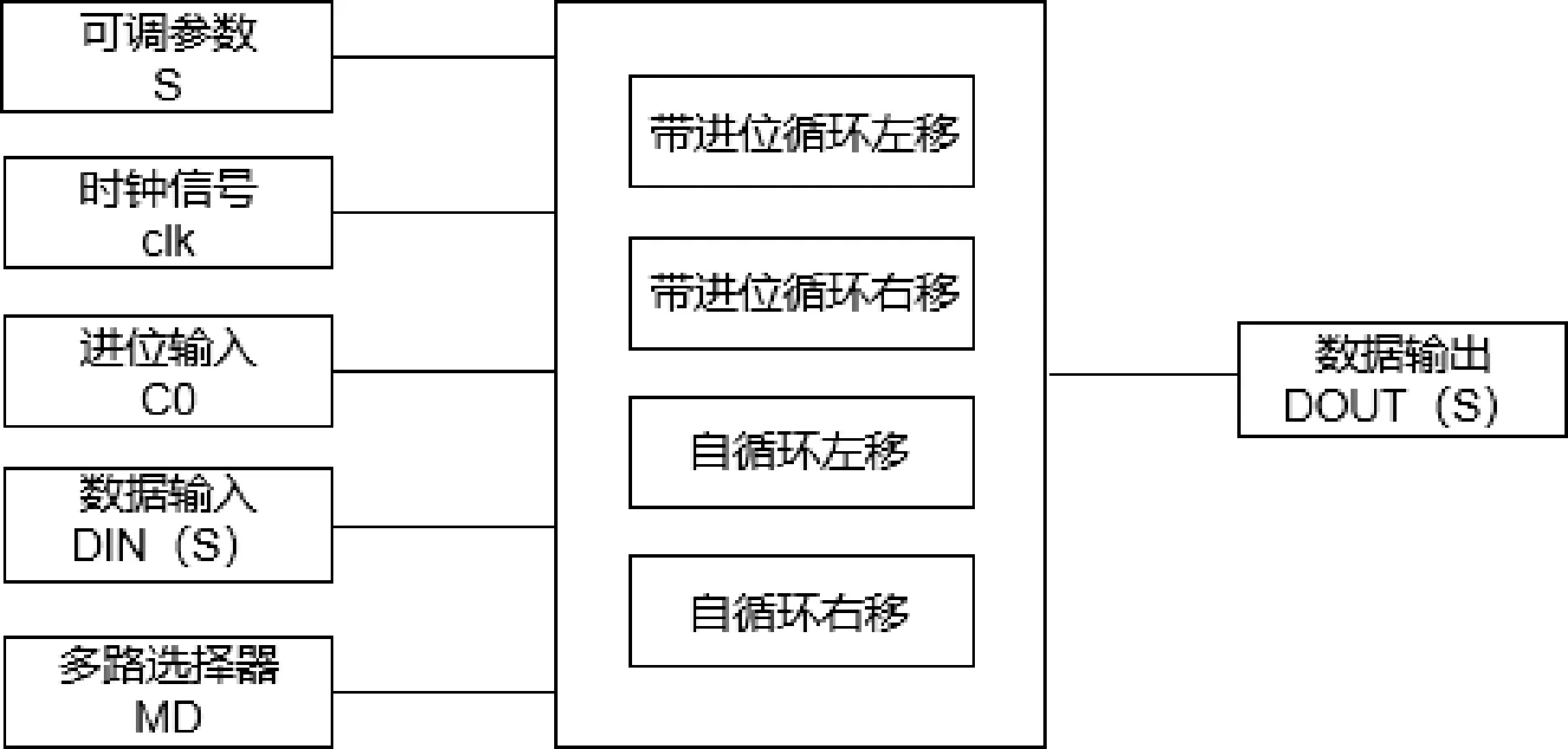

整个系统主要由多路选择器模块、参数可调带进位循环左移移位寄存器、参数可调带进位循环右移移位寄存器、参数可调自循环左移移位寄存器、参数可调自循环右移移位寄存器和输入输出模块构成,系统电路结构的设计,如图1 所示[3]。通过设置可调参数S的数字来确定4 个移位寄存器的数据输入Din 和数据输出DOUT 的位数[4]。多路选择器根据电路的需要可选择当前移位寄存器为带进位循环左移移位寄存器、带进位循环右移移位寄存器、自循环左移移位寄存器、自循环右移移位寄存器等四种之一。整个电路实现可调参数移位寄存器的多种移位功能。

图1 系统电路结构

2 系统模块设计

本文设计的参数可调多功能移位寄存器是用来实现对不同参数的移位寄存器进行带进位循环左移、带进位循环右移、自循环左移、自循环右移等功能。

2.1 多路选择器

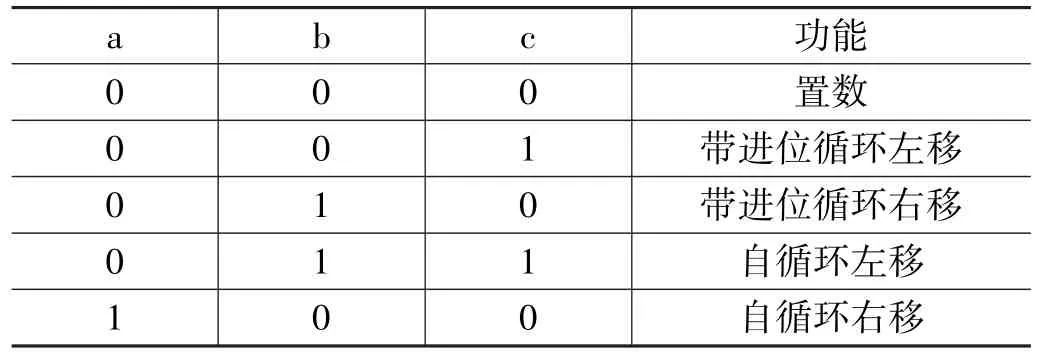

所设计的参数可调移位寄存器采纳并入串出的方式,具有带进位循环左移、带进位循环右移、自循环左移、自循环右移4 种功能。因此还需使用多路选择器来实现功能的切换。这里用一个八选一多路选择器来实现该功能[5]。设a,b,c 为八选一多路选择器的输入信号,多路选择器的值与对应功能,如表1 所示。

表1 多路选择器的值与对应功能

2.2 参数可调多功能移位寄存器

系统设计选择的移位方式是不同的,以下是各功能移位寄存器的具体实现[6]。

2.2.1 带进位循环左移移位寄存器

带进位循环左移,通过进位输入端输入待进位的数据C0,把输入数据的各个二进制位向左移动S 位,再将进位数据C0 依次移到右端空出的位上,在每个时钟上升沿到来时,进行重复操作。其中,REGn 为内部信号,用它暂存输入的数据,无方向性;CY 是进位输入。先把输入的数据DIN 传递给REGn,再通过MD 选择不同的移位方式进行移位。该操作完成后,将移位之后的数再通过REGn 传递到DOUT 并输出。代码如下:

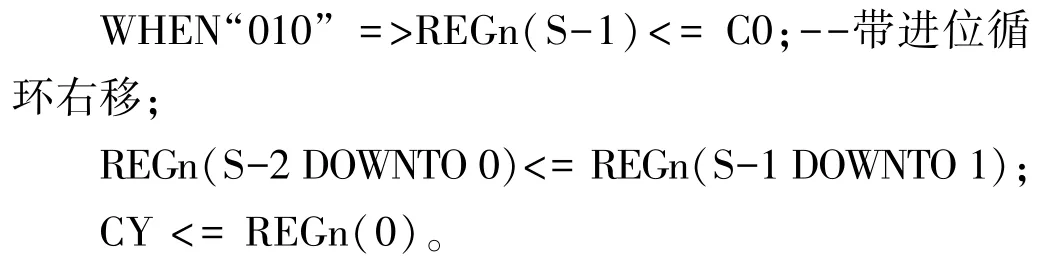

2.2.2 带进位循环右移移位寄存器

带进位循环右移,就是通过进位输入端输入待进位的数据C0,把输入数据的各个二进制位向右移动S位,再将进位数据C0 依次移到左端空出的位上,在每个时钟上升沿到来时,进行重复操作。代码如下:

2.2.3 自循环左移移位寄存器

自循环左移,就是把输入数据的各个二进制位向左移动S 位,再把从S 左端移出的每1 位顺次移动至右端空出的位置上,在每个时钟上升沿到来时,进行重复操作。代码如下:2.2.4 自循环右移移位寄存器

自循环右移,就是把输入数据的各个二进制位向右移动S 位,再把从S 右端移出的每1 位顺次移动至左端空出的位置上,在每个时钟上升沿到来时,进行重复操作。代码如下:

3 系统仿真测试与分析

3.1 参数可调多功能移位寄存器系统电路

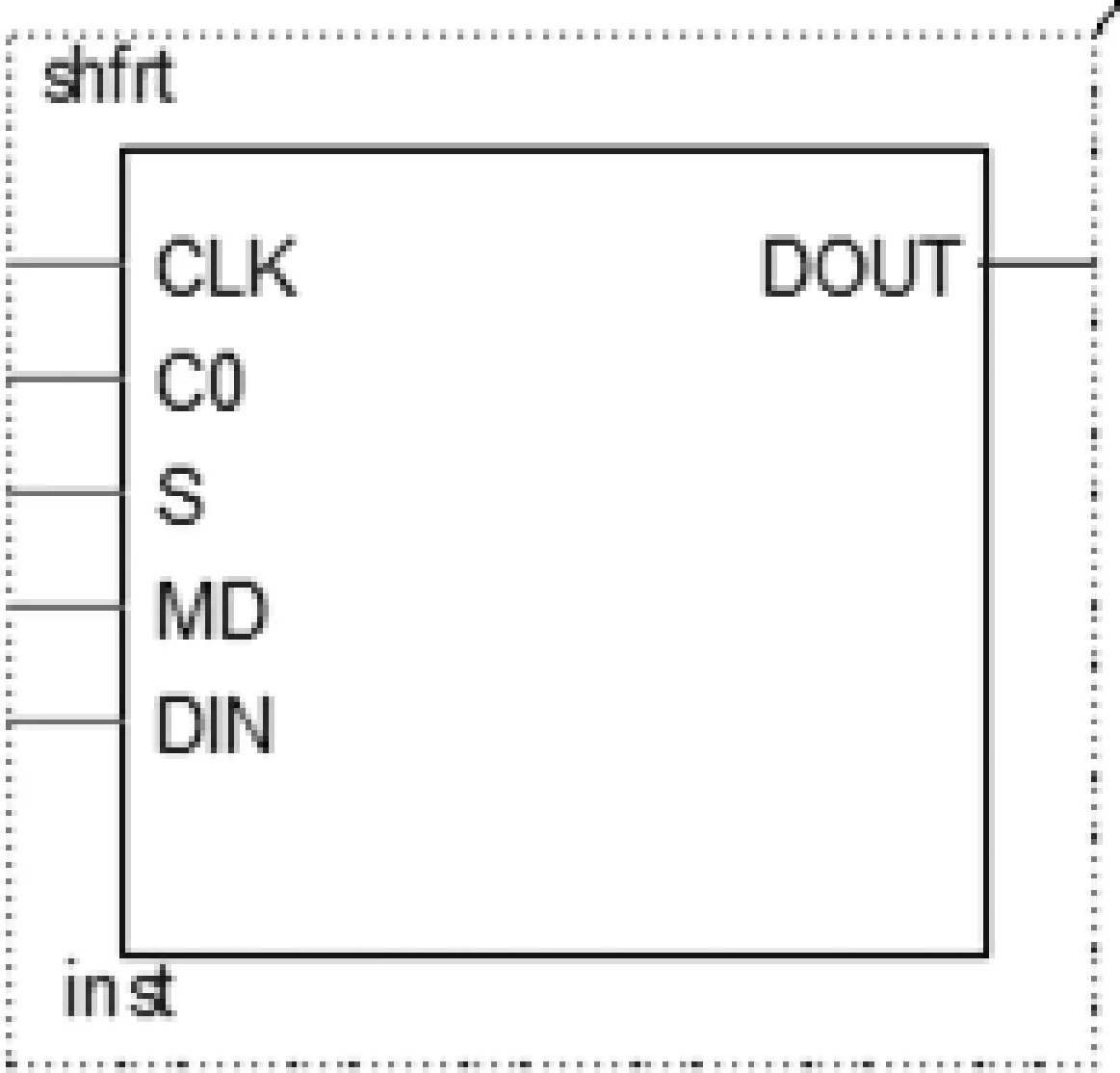

本系统采用传统的自上向下的设计理念,前面已经完成了对各个模块的设计,因此只需要将各个模块进行总体的整合即可得到整个系统[7]。系统顶层电路,如图2 所示。

图2 系统顶层电路

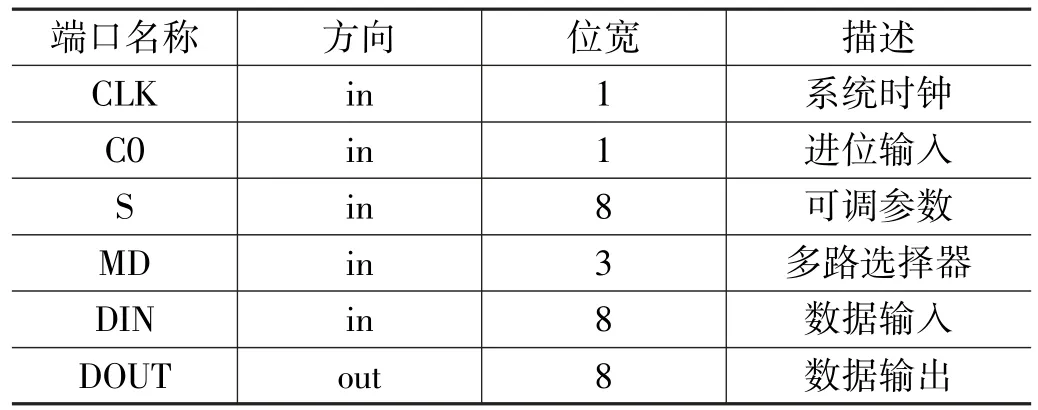

以8 位多功能移位寄存器为例,系统顶层电路的端口描述,如表2 所示。

表2 系统顶层电路的端口描述

3.2 系统仿真测试与分析

本设计使用多路选择器及移位功能模块来完成可调参数移位寄存器的系统功能[8]。首先,从外部设置1个参数。其次,通过输入端口输入对应数据和进位标志,再经过多路选择器选择所需的移位方式。最后,输出实现对应移位功能后的数据,用ModelSim 进行仿真。以8 位移位寄存器为例,则此时可调参数S 设定为8,并设DIN 为01010101,如图3 所示。

图3 8 位移位寄存器多功能仿真结果

(1)当MD 为000(置数操作),持续了1 个时钟周期,当第 1 个时钟上升沿降临时,输出 DOUT为01010101。

(2)当MD 为001(带进位循环左移),进位输入C0为0,持续了3 个时钟周期,进行移位的数应该是上一个输出DOUT,此时DIN 为01010101。每遇到1 个时钟上升沿,就执行一次移位功能,这里进行了3 次移位;当第2 个时钟上升沿降临时,DOUT 为10 101010;当第3 个时钟上升沿降临时,DOUT 为01 010100;当第4个时钟上升沿降临时,DOUT 为10101000。

(3)当MD 为010(带进位循环右移),进位输入C0为1,持续了3 个时钟周期,进行移位的数应该是上一个输出DOUT,此时DIN 为10101000。每遇到1 个时钟上升沿,就执行一次移位功能,这里进行了3 次移位。当第5 个时钟上升沿来临时,DOUT 为11 010100;当第6 个时钟上升沿来临时,DOUT 为11 101010;当第7 个时钟上升沿来临时,DOUT 为11110101。

(4)当MD 为011(自循环左移),持续了3 个时钟周期,进行移位的数应该是上一个输出DOUT,此时DIN 为11110101。每遇到1 个时钟上升沿,就执行一次移位功能,这里进行了3 次移位。当第8 个时钟上升沿来临时,DOUT 为11 101011;当第9 个时钟上升沿来临时,DOUT 为11 010111;当第10 个时钟上升沿来临时,DOUT 为10101111。

(5)当MD 为100(自循环右移),持续了3 个时钟周期,进行移位的数应该是上一个输出DOUT,此时DIN 为10101111。每遇到1 个时钟上升沿,就执行一次移位功能,这里进行了3 次移位。当第11 个时钟上升沿到来时,DOUT 为11 010111;当第12 个时钟上升沿来临时,DOUT 为11 101011;当第13 个时钟上升沿到来时,DOUT 为11110101。

经仿真测试所得的结果表明该设计达到了参数可调多功能移位寄存器的要求。

4 结语

本系统是基于FPGA 开发平台,使用VHDL 语言对不同移位功能进行编写,实现参数可调移位寄存器的多种功能。所实现的参数可调和多种移位功能都是对一般移位寄存器进行进一步的优化与完善,增强了设计的灵活性和资源的可配性,减小了电路的复杂性。