一种高精度时间间隔测量电路的设计

2022-06-15赵雪鹏苏淑靖

赵雪鹏, 苏淑靖 , 高 媛

(1. 中北大学 省部共建动态测试技术国家重点实验室, 山西 太原 030051;2. 军委装备发展部某中心, 北京 100034)

0 引 言

时间间隔测量技术在武器、 航空航天、 高能物理等研究领域中有着广泛的用途. 在武器研究领域, 对打击目标进行精确测距是精确打击的前提, 提高时间间隔测量的分辨率就意味着有效提高制导、 引爆的精确度[1]; 在航空航天领域, 通过精确测量反射波和发射波之间的时间间隔可精确标定飞行器的飞行高度, 保障飞行器的安全[2]; 在核物理实验中, 通过测量粒子的飞行时间, 再结合飞行距离即可确定粒子的质量, 实现粒子鉴别[3].

目前, 高精度时间间隔测量的方法主要有时间扩展计数法、 时间-幅度转换法、 时间游标法及抽头延迟线法等[4]. 时间扩展计数法的转换时间长, 非线性度大; 时间-幅度转换法的单次测量精度虽然高, 但测量的时间间隔范围小, 时钟稳定要求高[5]; 时间游标法需要高稳定度的可启动振荡器和高精度的重合检测电路, 制作及调试难度大、 造价高, 且转换时间长[6]; 抽头延迟线法构成的时间间隔测量系统分辨率由触发器自身器件的内部延迟时间决定, 触发器的延迟时间通常为纳秒量级[7]. 例如: 美国是德科技公司研发的 U1050A 型计时器具有12个测量通道, 最高分辨率为5 ps, 测量精度为10 ps[8]; 拉脱维亚研发的A033-ET 事件计时器单次测量精度最优到 3.5 ps, 测量精度达到 4 ps[9]; 法国研发的GT688系列计时器测量分辨率和测量精度都达到了1 ps[10]; 上海天文台通过在FPGA内部搭建延迟线结构, 设计出了基于数字延迟电路的时间测量模块, 测量分辨率为10 ps, 测量精度为50 ps[11]. 本文采用时间-数字转换和时间-幅度转换相结合的方法来研究改善时间间隔测量的方法, 进一步提高时间间隔的测量分辨率、 测量精度以及测量范围.

1 时间间隔测量方案

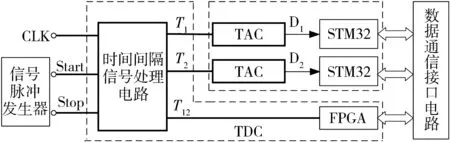

时间间隔测量电路主要由时间-数字转换模块(TDC)、 时间-幅度转换模块(TAC)以及通信接口电路组成, 如图 1 所示. 信号脉冲发生器用于产生待测标志信号Start和Stop; 时间间隔信号处理电路将待测时间间隔信号T转换为大于参考时钟周期的待测信号T12和小于参考时钟周期的待测信号T1和T2, FPGA通过内部计数器直接测量T12; 信号T1和T2用于控制TAC电路中采样电容的放电时间, 通过测量电容放电前后的电压差, 可计算出放电时间t1和t2; 数据通信接口采用RS485通信方式连接PC机, 用于接收、 处理测量的时间间隔数据, 最终计算出待测时间间隔t.

图 1 时间间隔测量方案

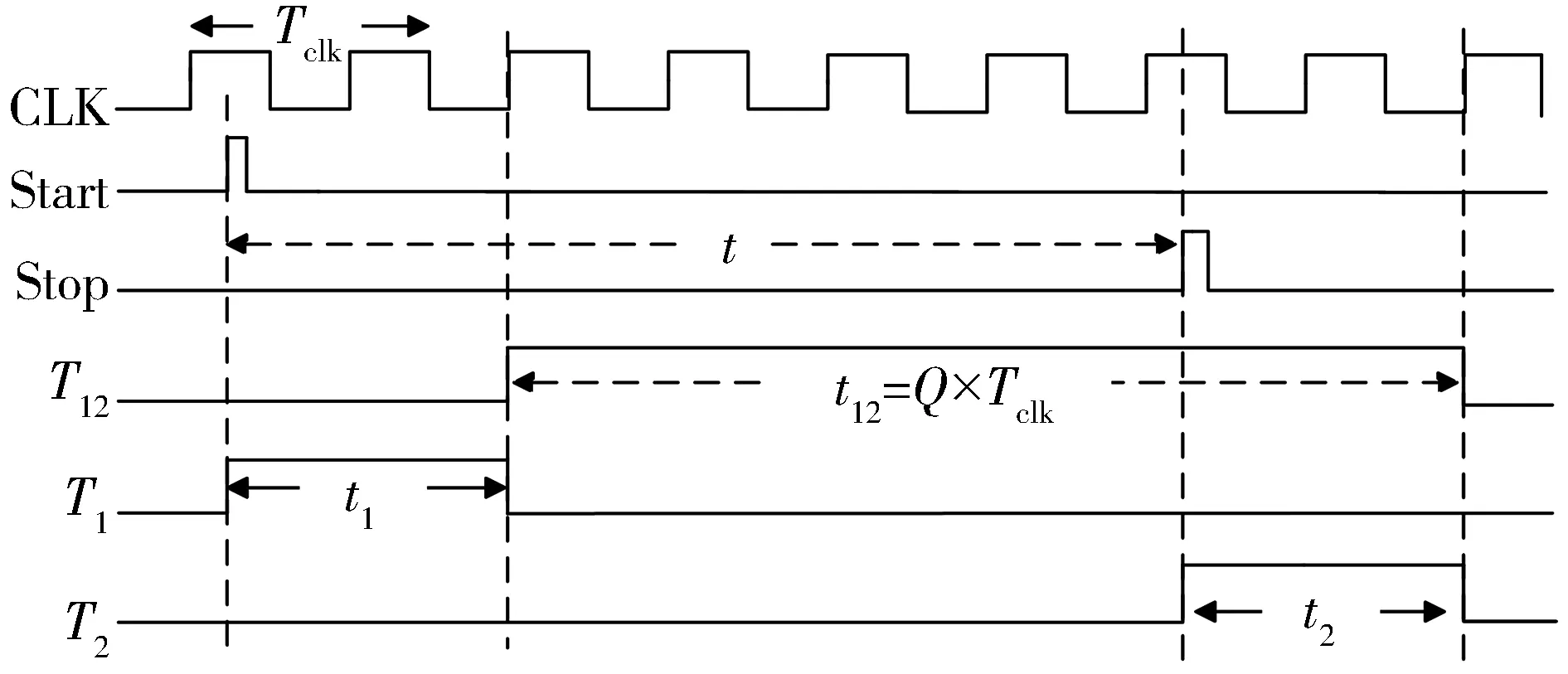

时间间隔测量原理如图 2 所示, Start信号与 Stop信号上升沿之间的时间间隔t为待测时间.在T12为高电平时, FPGA通过CLK信号上升沿触发内部计数器进行计数, 每来一个时钟上升沿计数器值Q都会加1, 直到T12信号为低电平时停止计数, 测得的时间间隔t12=Q×Tclk.采用计数法进行时间间隔测量的产生的量化误差为t-t12=t1-t2, 其中t1,t2分别为Start信号、 Stop信号上升沿到第二个时钟上升沿的时间差[12].t1和t2采用时间-幅度变换(TAC)进行量化, 被测时间间隔t=t12+t1-t2. 将时间-数字转换法和时间-幅度转换法相结合, 既可以实现大量程的时间间隔测量, 又能提高测量分辨率.

图 2 时间间隔测量原理

1.1 时间-数字转换模块设计

1.1.1 时间间隔测量途径

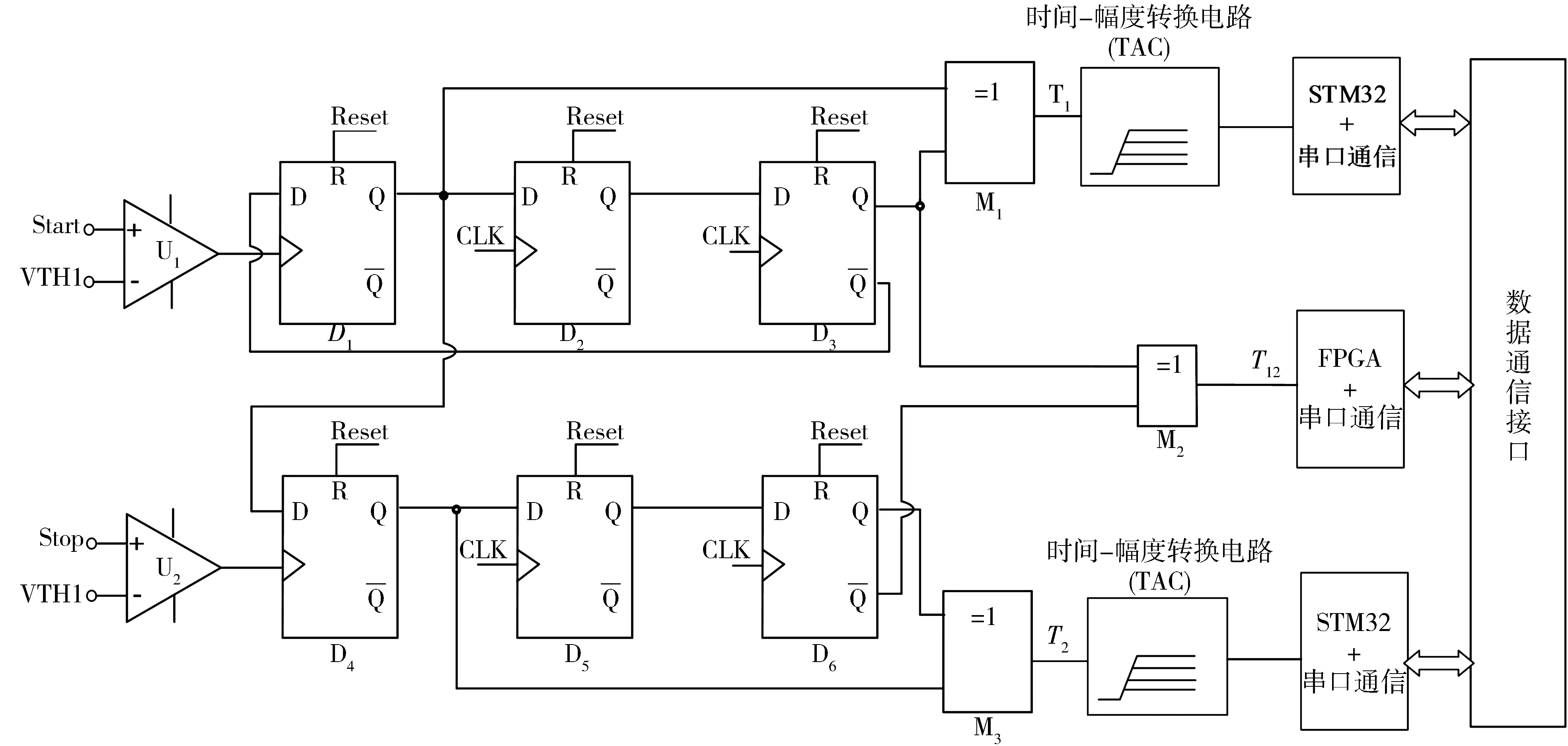

时间间隔测量方案如图 3 所示, 通过多个D触发器组成的时序逻辑电路对Start和Stop信号进行逻辑组合变换, 最终产生了待测信号T1,T2和T12.将T1和T2信号送入TAC电路进行测量, 将时钟周期整数倍的时间间隔T12信号送入FPGA作为计数器计数的控制信号. FPGA和D触发器的驱动时钟频率为400 MHz, 该时钟由铷时钟通过锁相环倍频得到[13], 具有高精度、 低温漂等特点, 保证了测量精度. 在FPGA中设计一个49 bit的计数器, 在400 MHz频率的驱动下计数周期为2.5 ns, 当计数器计满时测量的最大时间间隔为1 407 374.88 s,可实现106s时间间隔的测量.

图 3 时间间隔测量方案设计

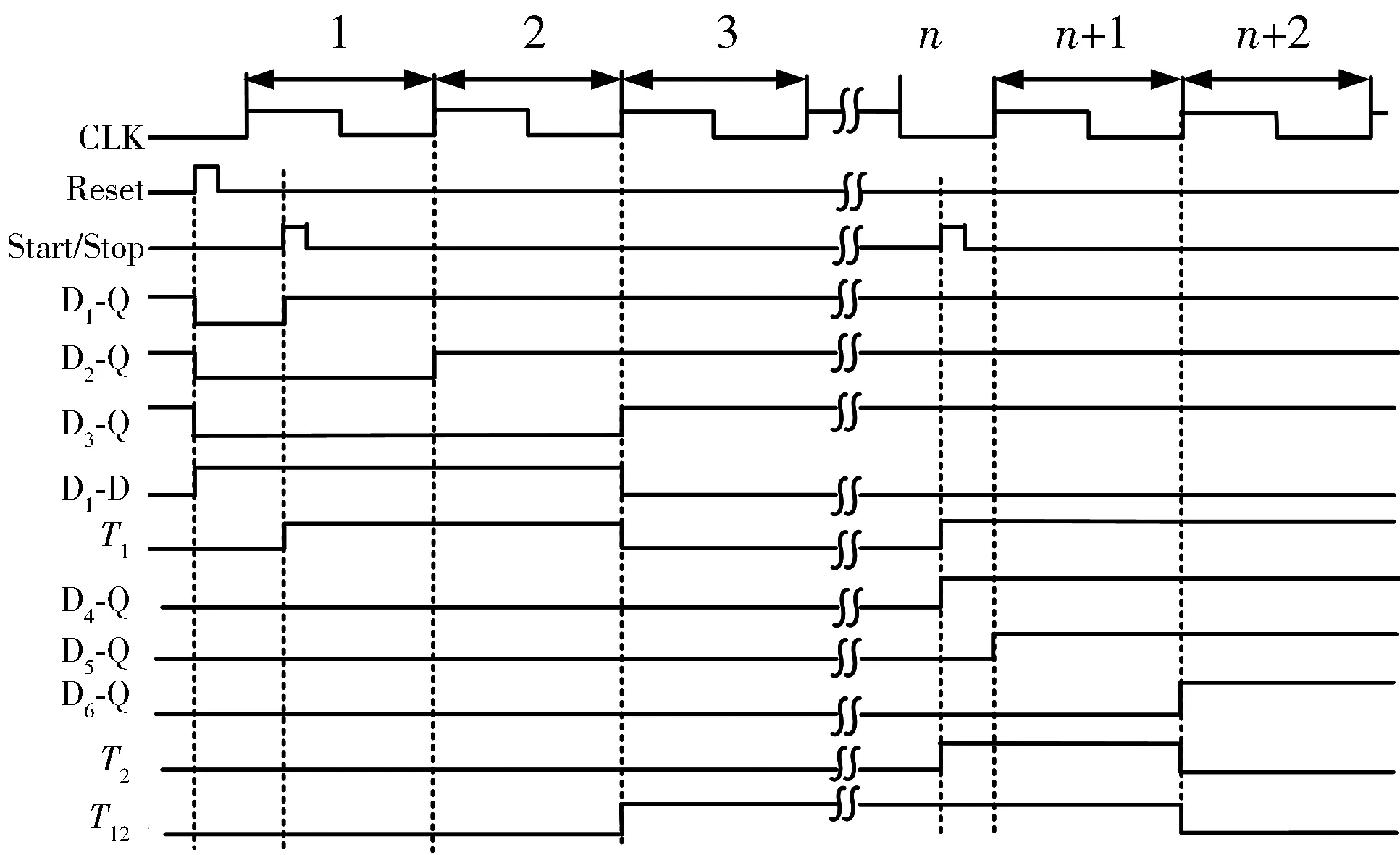

图 4 主要描述了TDC电路中主要信号的波形图.

图 4 TDC电路主要信号波形图

1.1.2 时间-数字转换电路设计

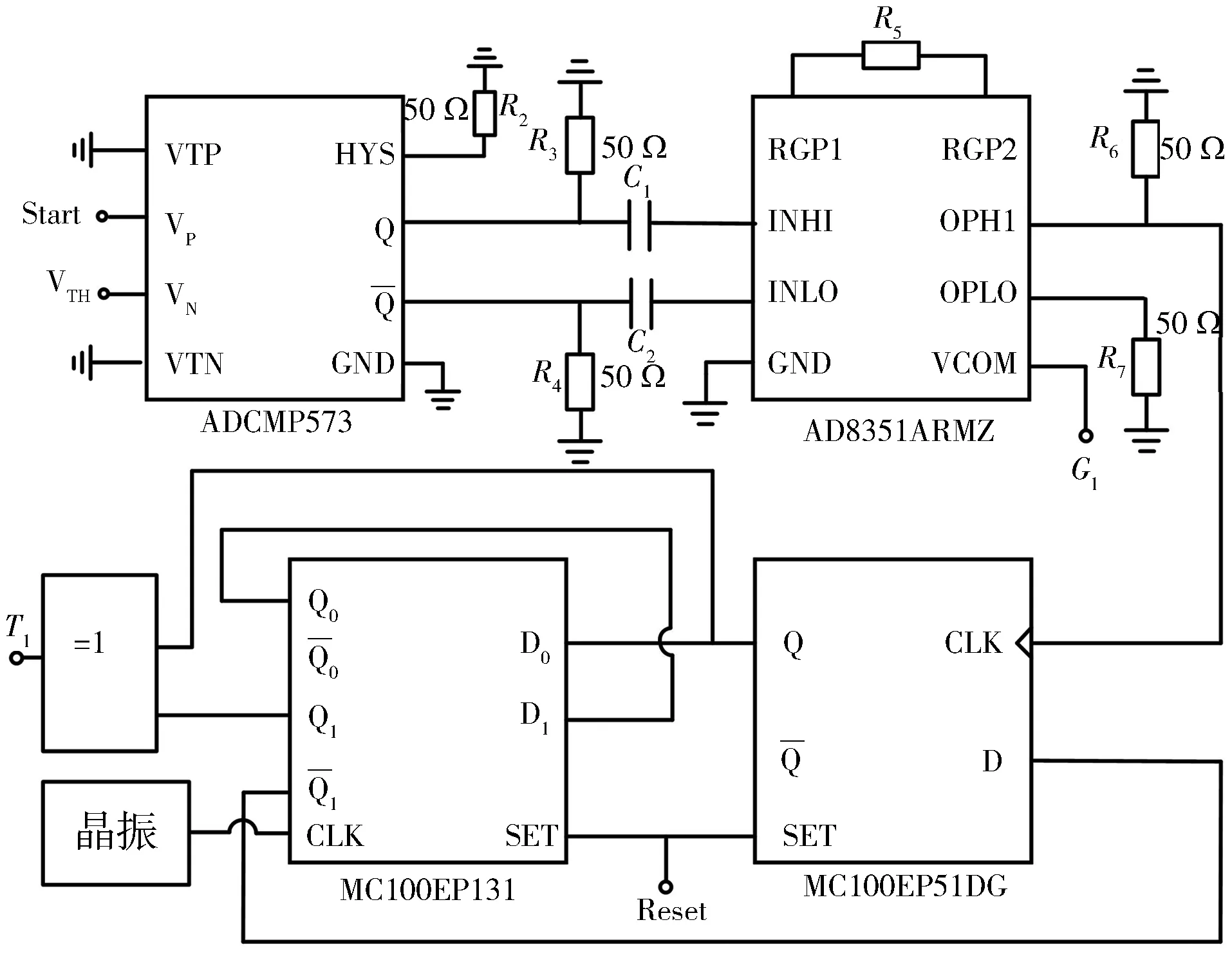

以图 3 中起始Start信号处理为例, 通过图 5 所示的电路转换出待测信号T1.输入信号通过与比较器的阈值电压比较来判断待测信号的变化, 经过差分运算放大器将触发信号传至D触发器, 通过3路D触发器的逻辑运算得到待测信号T1. ADCMP573是一种低抖动、 低传播延迟的比较器, 具有鲁棒输入和可编程迟滞等特性; VTP和VTN内含50 Ω的终端输入反馈电阻, 为匹配前端脉冲信号发生器的输出阻抗, 使VTP和VTN接地后, 信号输入端VP和VN的输入阻抗为50 Ω; HYS为磁滞控制端, 通过接地电阻R2调节迟滞电压的大小, 从而增强比较器输入端对噪声的抗干扰能力. 为解决比较器与D触发器之间电平不匹配的问题, 在两级之间加入了差分运算放大器. AD8351是一款具有低噪声和低谐波失真特性的运算放大器, 其输出的共模电压和放大增益均可调节, 通过调节放大增益和共模电压, 将比较器的输出电压调节到适于驱动D触发器的值. 其中,R3,R4,R6和R7均为50 Ω的电阻, 用于源端阻抗匹配,R5用于调节运放增益. 在差分运放前端, 通过C1和C2实现信号交流耦合传输, 隔离信号的共模量, 之后通过G1调节差分运放输出的共模电压.为了使驱动信号可同时到达4路D触发器, 提高时序稳定性, 选择了集成4路D触发器的MC100EP131, 其内异步复位SET, 也可同步复位4路D触发器, 避免了路径延时造成的复位时差.

图 5 时间-数字转换电路

1.2 时间-幅度转换模块设计

1.2.1 设计原理

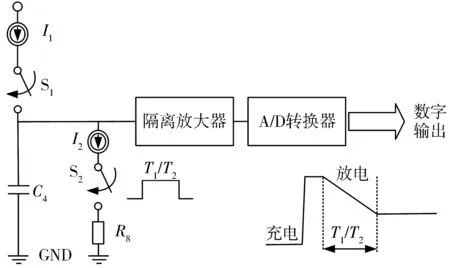

通过时间-幅度转换电路对T1和T2时间信号进行转换、 采集, 可以实现高分辨率时间测量. 时间-幅度变换原理如图 6 所示,T1,T2窄带脉冲信号作为门控信号, 与三极管基极相连构成开关来控制恒流源放电, 使得电容放电时两端的电压线性减小[10]. 电容放电前后的电压经过运放跟随和滤波后被A/D转换器采集量化.

图 6 时间-幅度变换原理

在图 6 中, 待测信号T1,T2到来前, S1闭合, 恒流源I1向电容C3充电, 充电完毕后S1断开. 当T1,T2脉冲到来时, S2闭合电容通过恒流源I2放电. 由电容及其电荷量和两端电压的关系公式(1)可得, 电容在恒流源下放电为均匀放电, 电压减小量与放电时间呈线性关系.

(1)

与充放电电容连接的是一个拥有高输入阻抗的隔离放大器, 隔离后级不影响电容的充放电. 在理想状态下, 当窄脉冲信号T1到来时, 高速三极管开启导通, 电容C3两端的电压在放电恒流源电路作用下开始线性下降, 由U下降到U′, 压差为Ud, 电压下降量为

(2)

式中:t1为放电时间长度;I2为放电恒流源大小.

将放电后的电压U′送入信号调理电路, 经过跟随器和低通滤波器后, 输出至模数转换器中进行量化. 电压模拟量与数字量的量化关系为

(3)

式中:ULSB为模数转换器的最低有效量化值;n为模数转换器的转换位数;MK为量化为二进制数的值;K代表二进制数中的第K位. 结合式(2)和式(3)可以推出时间t1为

(4)

上述公式表明, 时间间隔的分辨率由ADC位数、 电容大小和放电恒流源值共同决定. 量化误差和系统噪声的存在, 导致了测量分辨率的下降. 为了进一步优化时间间隔测量的指标, 不仅要合理选择高位数、 低增益误差的ADC, 还需要对TAC电路进行合理设计.

1.2.2 时间-幅度转换电路设计

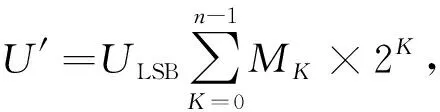

时间-幅度转换电路原理图如图 7 所示, 电路主要包含了充电恒流源电路、 放电恒流源电路、 钳位电路以及采样电路. 充放电恒流源提供稳定的电流源, 对电容进行线性充放电, 钳位电路控制电容充电时的电压上限, 采样电路用于采集电容放电前后的电压值.

在充电恒流源模块中, 开关S1控制充电恒流源开启闭合, 当S1闭合时, 三极管Q1的发射结正偏, 运放A1通过发射结进入负反馈, 根据虚短可得Q1的发射极的电压等于A1同相端的输入电压, 恒流源电流大小为电阻R9两端的电压除以电阻的阻值. 电路中电压U1,U3分别为8 V, 7 V, 电阻R9为100 Ω, 可得充电恒流源的大小为10 mA. 电路中开关S1选用FDMC7660, 该芯片为N沟道的MOS管, 其门控开启阈值电压为2.5 V, 当大于2.5 V时, MOS管漏极和源极导通, 其导通电阻为mΩ级别, 功率损耗很小; 三极管Q1选用CM5160, 它是一种硅材料的PNP射频晶体管, 专为高频放大和开关应用而设计, 当未导通时其漏电流只有10 μA; 为保持恒流源的稳定, 本文选择的运放为AD8605, 该芯片是一个单通道轨到轨的运算放大器, 其具有非常低的偏置电压(65 μV)和噪声(8 nV/Hz), 单位增益稳定. 可通过改变电压U3来控制R9两端的电压, 从而改变恒流源的大小.

图 7 时间-幅度转换电路原理图

Fig.7 Schematic diagram of time-amplitude conversion circuit

为了使电容充电后电压处于稳定状态, 钳位电路采用稳压二极管的反向稳压特性以及二极管正向导通特性来实现钳位功能. 设计方案中, 电容充完电后电压设定在5 V, 所以钳位电路中供电电压U6为5 V; D2采用的是4.3 V的稳压二极管, 当S1闭合后, 恒流源开始对电容C3进行充电, 充电至5 V 后停止充电, 到达钳位效果.

在放电恒流源模块中, 当脉冲信号T1,T2到来时, 短暂的脉冲信号会抬高三极管Q2基极的电压, 使得发射结正偏, 三极管CE两端导通, 电容通过恒流源均匀放电. 放电恒流源同充电恒流源原理一致, 通过改变运放A3同相输入端的电压值来控制电阻R14两端的电压, 以达到控制恒流源大小的目的. 电路中, 运放A3同相端提供1 V的电压, 电阻R14为100 Ω, 所以, 放电恒流源大小为10 mA.

采样电路对电容C3放电前后的电压进行采样, 通过电压跟随器减少采样电路对电容充放电的影响, 起到隔离保护的作用.R15和C4构成低通滤波器, 可以减少噪声对信号采集的干扰. STM32通过SPI通信方式控制AD转换器对滤波后的电压采集并存储, 其数据可通过数据通信接口传至PC机. 为了获得高分辨率的时间间隔信号, 本文选择16 bit高分辨率的ADC, 芯片选用ADI公司的AD7980. AD7980芯片是一个逐次逼近的模数转换器, 内含一个高速、 低功耗的16 bit采样ADC和一个通用串行接口端口, 电压输入范围为0~UREF, 其转换误差只有±0.6LSB, 保障了时间间隔采样的分辨率和精度.

当AD7980的参考电压为5 V时, 16 bit ADC对应的电压分辨率为76.3 μV. 电路中放电恒流源的电流I2为10 mA, 为了实现1.5 ps的分辨率测量, 通过式(4)计算可得电容C最大为131.58 pF. 当电容选择100 pF, ΔU为5 V时, 代入式(1)计算可得Δt(完全放完电所需要的时间)为50 μs, 即TAC测得的最大时间间隔为50 μs.

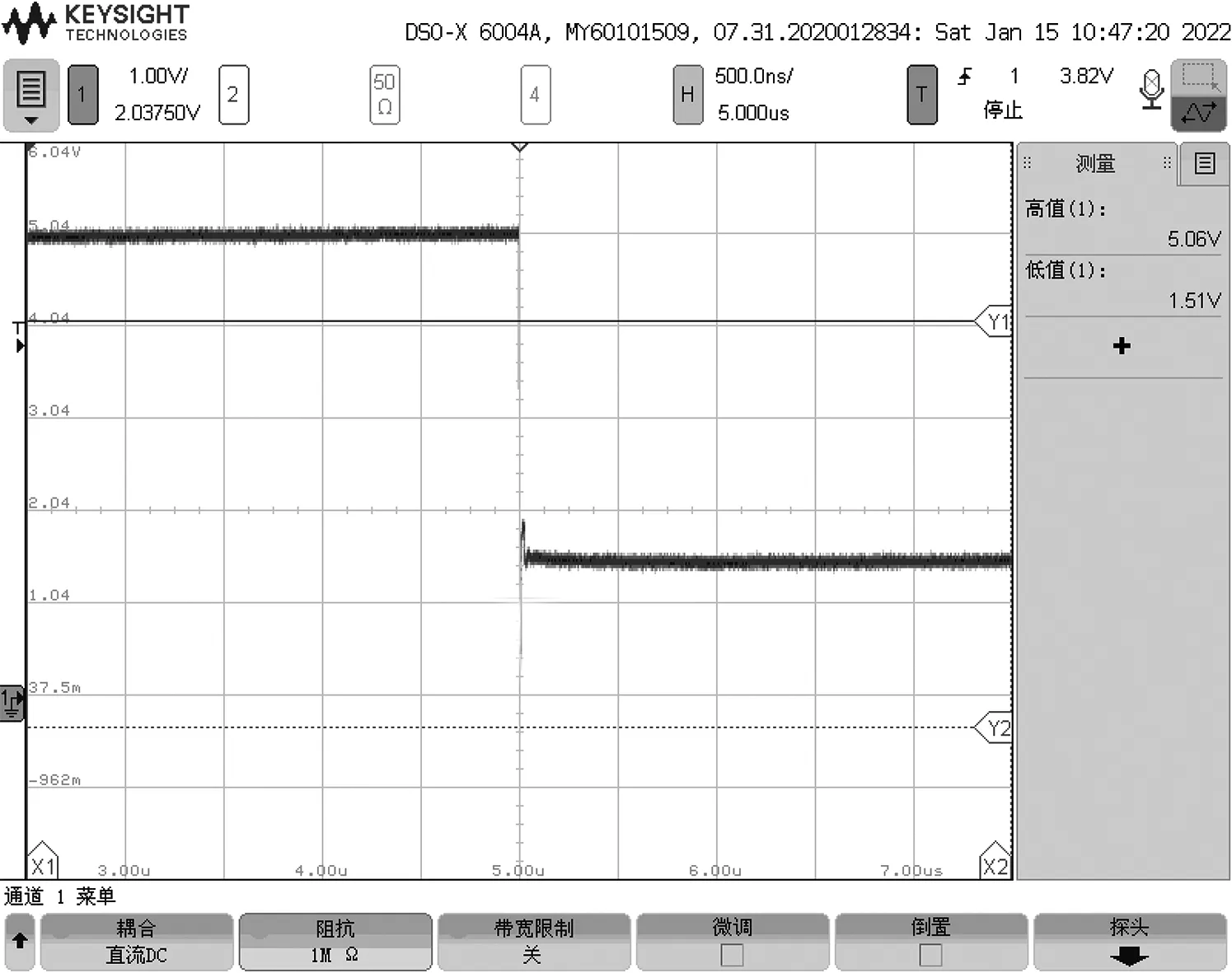

通过示波器对时间-幅度转换电路进行测试, 可观测到电容的放电过程如图 8 所示. 从图中可以看到, 电容呈线性放电, 放电前后的电压分别为5.06 V和1.51 V.

图 8 电容放电过程

1.2.3 STM32程序设计

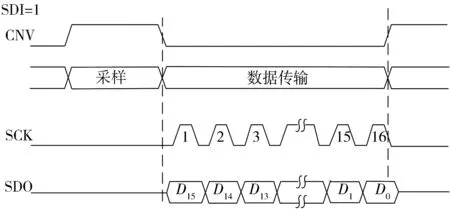

AD7980采用SPI的通信方式与STM32连接, 通信时序如图9所示. 串行数据接口通过串行数据输入(SDI)、 时钟输入(SCK)和转换控制(CNV)引脚实现了三线式控制输入. 当SDI输入端为高, CNV上升沿到来时, 芯片通过+IN端开始对数据进行采样, SDO输出为高阻抗; 当CNV下降沿到来时, 数据开始输出至SDO, 并随着SCK的下降沿依次输出数据至STM32, 其采样时序图如图 9 所示.

图 9 AD7980时序图

1.3 通信机制及通信接口电路设计

为了获取所测量的时间间隔数据, 设计时保留了数据通信接口, 用于读取STM32和FPGA内部寄存器的数据, 测试时使用PC机串口助手通过RS485转接器来读取T1,T2和T12的值, 最终计算出时间间隔t.

主机与从机通信采用帧结构形式. 一帧数据为11字节, 帧头、 地址和校验位各为1字节, 数据位8字节[14]. 帧头被用来识别数据帧的开始; 帧地址为接受数据的从机地址, RS485总线上的通信为广播方式, 所以, 每个从机都有独立地址, 通过地址对比来判断该数据帧是否应该接收; 帧中的数据位为实际传输数据, 是PC机下达的命令; 校验位用于数据帧的校验, 通过异或校验的方式来验证数据传输过程中是否出现误码.

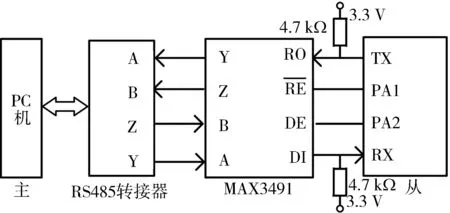

PC机与从机的通信接口采用半双工UART 接口, 通过异步串行通信方式接收和发送信息. 上电后, 从机处于待机状态, 实时监测总线上是否有数据传输. 当检测到数据传输时, 从机开启串口中断, 接受数据并判断该帧数据是否正确, 若不正确则需要主机重新发送, 如果正确则将寄存器中测量的数据发给PC机, 通信接口电路连接示意图如图 10 所示.

图 10 通信结构图

通信芯片选用Maxim Integrated厂商的MAX3491, 该芯片具有通信速率高、 功耗低特点, 能够满足电路通信需求. 在电路上, 芯片的接收端和发送端都需要接4.7 kΩ的上拉电阻, 当没有数据发送时总线默认置高, 使得总线上电平稳定.

2 实验测试及结果分析

时间间隔测量电路选择的驱动设备为美国是德科技生产的81134A. 该设备是一个双通道脉冲码型信号发生器, 具有低抖动、 快速上升时间等特点[15], 通过时间调制功能, 可以设置脉冲信号的间隔时间和电平值.

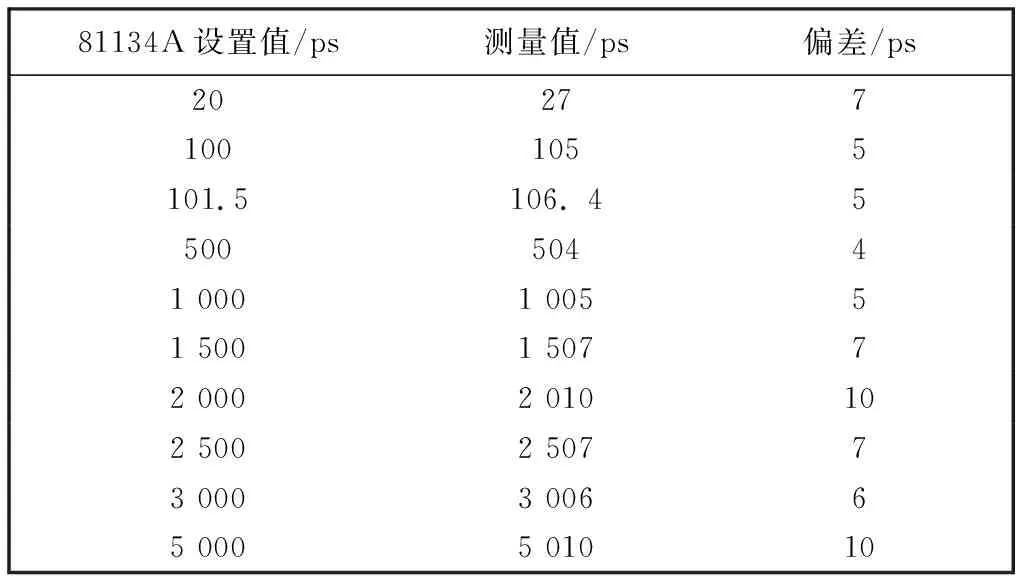

在搭建好的测试平台上, 系统上电后先闭合S1, 对电容C3进行充电. PC机通过数据通信接口向STM32发送指令, 获取电容充电后的电压; 断开S1, 设置81134A设备的脉冲信号, 设置时间间隔为100 ps, 打开该设备输出通道给系统提供脉冲信号, PC机再次向从机发送指令, 读取电容放电后的电压, 记录串口助手界面上回传的数据; 重新闭合开关S1, 更改81134A设备的时间间隔参数, 重新测量电容放电前后的电压并记录. 经过多次测量后, 最终计算的待测信号时间t如表 1 所示. 由于8113A设备本身所设置的间隔时间有限, 所以实际测试的最大间隔为 3 000 ps.

表 1 时间间隔测试数据

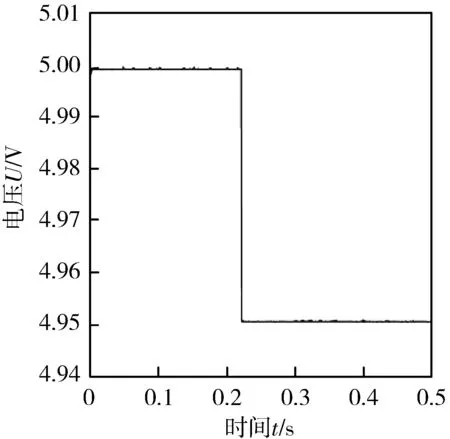

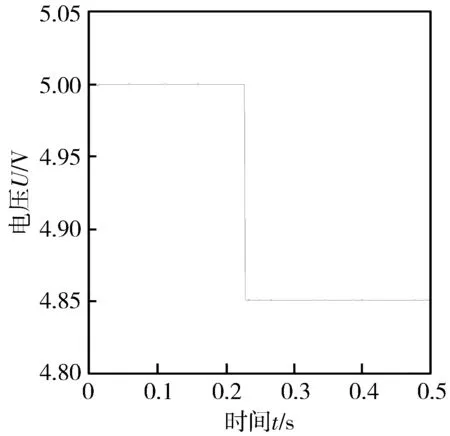

对500 ps, 1 000 ps, 1 500 ps和2 000 ps的时间间隔进行测量, 根据采样电路中电容放电前后的电压数据绘制的电压变化图形如图 11 所示.

(a) 时间间隔为500 ps

(c) 时间间隔为1 500 ps

表 1 中的数据都是对10次测量结果进行算术平均得到的. 由表 1 的数据可知, 设置值和测量值的偏差最大为10 ps, 实现了高精度时间间隔测量. 同时, 当设置1.5 ps的间隔时, 测量值同步产生1.5 ps的变化, 证明了电路可达到1.5 ps的分辨率. 由图 11 可知, 测量的时间间隔每增加500 ps 时, 电容放电后的电压值会减小0.05 V. 在时间-幅度转换电路中, 已知电容为100 pF, 放电电流为10 mA, 将这些参数代入式(1)中等式成立, 表明电路设计可靠且测试正确.

数据测量存在的误差主要包含了由电路和测量仪器内部热噪声导致的随机误差, 以及由参考时钟的不稳定度、 时间扩展的非线性以及信号传输延时等导致的系统误差. 对于随机误差采用数据统计方法进行误差处理, 系统误差通过软件校准和数据修正进行处理. 通过上述两种方法有效减少了测量误差, 提高了测量精度.

3 结 论

本文设计了一种高分辨率时间间隔电路, 对其主要部分的硬件电路设计进行了详细论述. 为了实现大量程、 高精度的时间间隔测量, 采用直接计数法与时间-幅度法相结合的时间间隔测量方式, 通过TDC电路将时间间隔拆分为大于驱动时钟周期的大时间间隔和小时间间隔. 大时间间隔由FPGA内部计数器直接计数得到, 每当时钟的上升沿到来时, 计数器就会加1; 小时间间隔信号作为开关信号来控制电容放电, 通过ADC采集电容放电前后的电压, 计算出小时间间隔的时间. 通过FPGA设计的49 bit的计数器能实现大量程测量, 测量范围可达106s; 实验结果表明, 电路的测量分辨率可达 1.5 ps, 测量精度为10 ps.