一种高精度限流电路的设计

2022-06-14董振斌

陶 敏 ,唐 威 ,董振斌, ,李 晶,

(1.西安邮电大学 电子工程学院,陕西 西安 710121;2.上海电子线路智能保护工程技术研究中心,上海 201202;3.上海维安电子有限公司,上海 201202)

限流电路在DC-DC、AC-DC、限流开关等电源管理芯片中被广泛应用,主要用于环路控制和限流保护[1-2]。当芯片外接负载过重时,会导致输出电流过大,严重时将会对功率管和后级系统造成不可恢复的损坏。因此,对于电源管理芯片而言,要求其不仅具有过流保护功能,而且还能精准地调节限流范围,确保输出电流可被限制在预期范围内,故限流电路是电源管理芯片中不可或缺的一部分[3-4]。

限流精度作为电源管理芯片关注的重要性能指标,在实际设计中,电流采样方式、运放的失调电压以及流片、封装均会对其造成影响[5-8]。倪春晓等[9]提出采用串联电阻采样技术,精度较高。但该方法对采样电阻要求较高,若电阻阻值过大,会导致芯片功耗较大,且采样电阻易受到工艺和环境温度变化的影响;谭玉麟等[10]提出通过采样管采样电流的方式,其采样电流较小,功耗较低,但采样管串联小电阻后与功率管并联,导致二者源端电位不相等,进而影响限流精度,且其电路结构未考虑失调电压对限流精度的影响。鉴于此,为保证限流精度,本文通过采样管采样技术,并使用CMOS 电流源结构代替采样管串联的小电阻,以提高采样精度;采用预放大再生锁存比较器结构,对运算放大器失调电压进行校正,减小失调误差对限流精度的影响;为减小流片、封装的误差对限流精度造成影响,设计了数字修调电路。

1 电路设计

1.1 电路结构

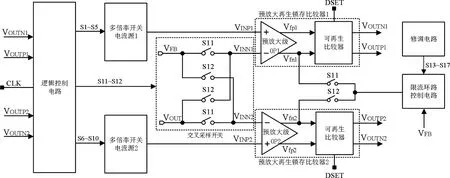

本文设计的限流电路分为失调电压校正和限流两种工作状态,结构框图如图1 所示。限流电路由逻辑控制电路、两组多倍率开关电流源、交叉采样开关、两组预放大再生锁存比较器、限流环路控制电路以及修调电路六部分组成。CLK 为时钟周期信号,VOUT为输出电压,VFB为连接采样管源端的反馈电压,DSET为复位信号。

图1 带失调电压校正的高精度限流电路结构框图Fig.1 Block diagram of the high-precision current limiting circuit with offset voltage correction

利用交叉采样开关控制预放大再生锁存比较器1 和2 的工作模式。当CLK 为低电平时,S11 闭合,S12 断开,交叉采样开关将预放大再生锁存比较器1 的负向端VINN1与VFB相连接,运算放大器OP1 输出端Vfn1与限流环路控制电路相连接,构成限流环路,对输出电流进行限制。预放大再生锁存比较器2 的负向端VINN2与VOUT相连,输出数字信号VOUTN2、VOUTP2至逻辑控制电路,通过逻辑控制电路控制多倍率开关电流源2,并将其结果反馈至预放大再生锁存比较器2,构成失调电压校正环路,对运算放大器OP2 进行失调电压校正;反之,当CLK为高电平时,S11 断开,S12 闭合,通过交叉采样开关控制预放大再生锁存比较器1 和2 交换工作模式,分别构成失调电压校正环路和限流环路进行工作。

失调电压校正环路是通过可再生比较器监测运算放大器两输出端,判断运放失调情况,通过逻辑控制电路调节多倍率开关电流源,改变运放正向输入端电压,实现对差分对管的电流补偿,减小运放失调电压,可得到一低失调运算放大器。

限流环路由运算放大器OP1/OP2 与限流环路控制电路构成,即采用低失调运算放大器钳位采样管的源端电压,能更精准地对输出电流进行采样及限制。

若限流值在流片、封装后与设计值存在偏差,可通过修调电路控制限流环路控制电路中的修调位,调节限流值大小,使其符合预期限流阈值范围,从而保证限流精度。

1.2 限流电路设计

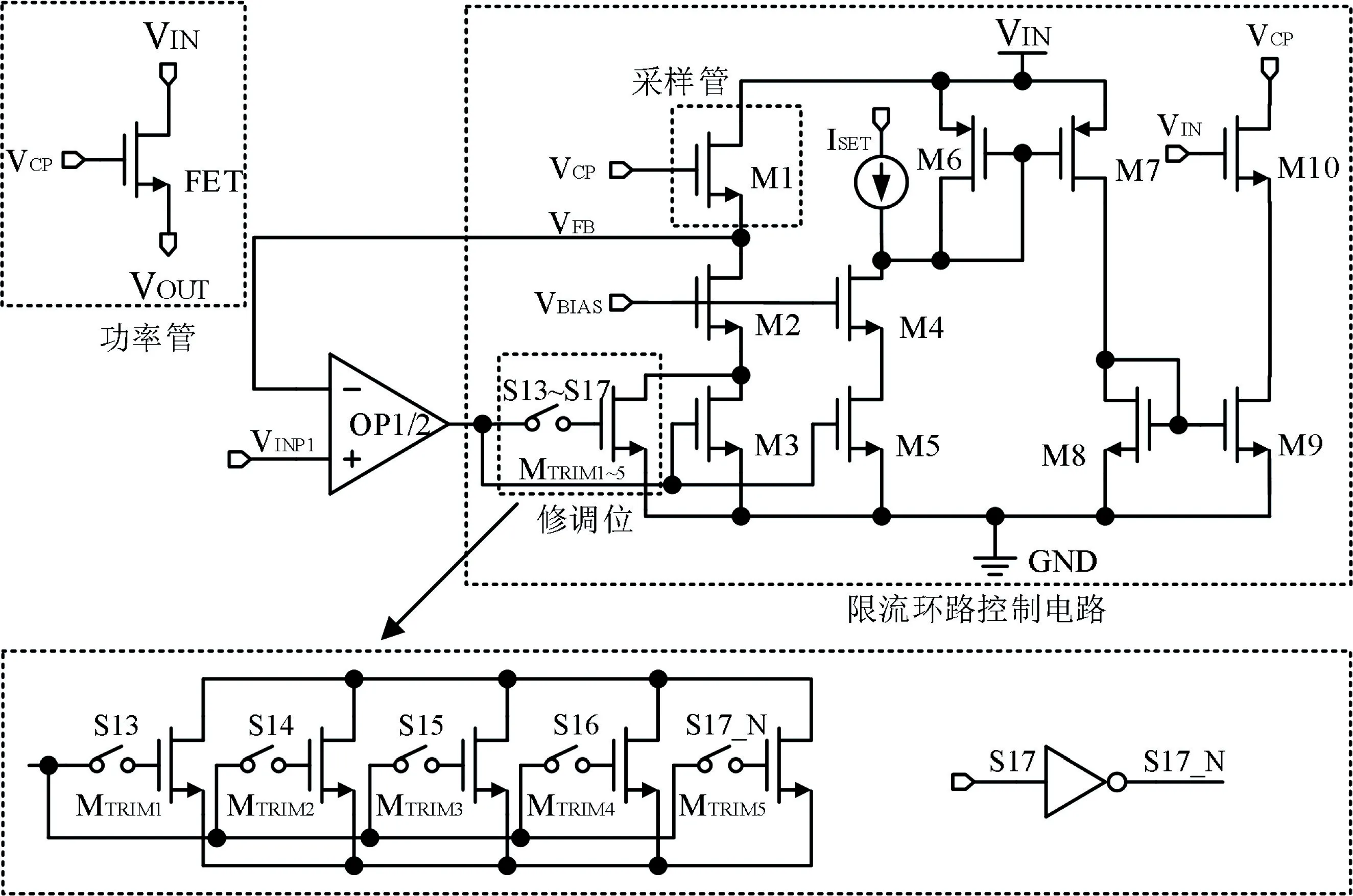

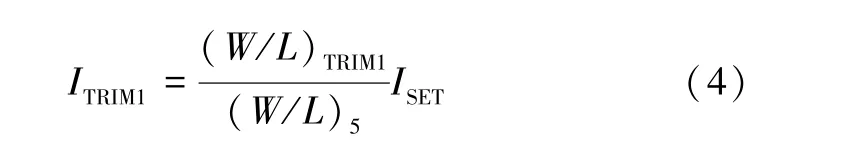

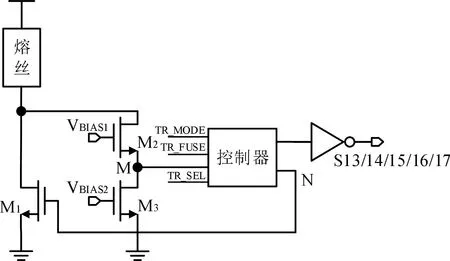

限流电路利用采样管实时采样功率管电流,当电流超过设定阈值后进行限流。并在限流电路中设置修调位,利用采样管与功率管的比例关系,通过修调电路改变流过采样管电流的大小,可实现对限流值的修调,保证其限流精度。当CLK 为低电平时,经失调电压校正后的运算放大器OP1 与限流环路控制电路构成限流环路,如图2 所示。其中,VINP1为多倍率开关电流源1 输出信号,VCP为电荷泵输出电压,VBIAS为偏置电压,S13~S17 为修调电路控制信号,MTRIM1~5为5 个修调位,ISET为限流值的基础电流。

图2 限流电路Fig.2 Current limiting circuit

通过将采样管M1 的源端VFB连接到运放的负向端形成负反馈结构,当输出电流过大时,将反馈调节栅电压VCP稳定至合理电位。M1 的源端电压反馈回运放的负向输入端,跟随输出电压的变化,使流过采样管M1 的电流ISENSE精确复制功率管电流ILIMIT。同时设计CMOS 电流源结构M2、M3 以及MTRIM1~5,使之与M4、M5 管并联,以提供限流值的基础电流。

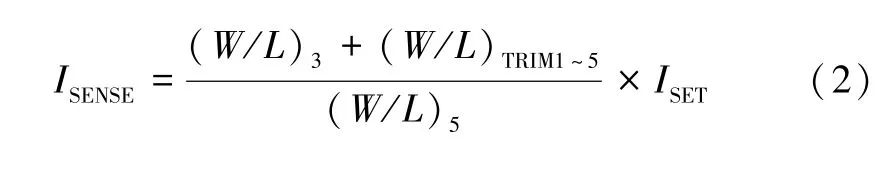

采样管M1 与功率管FET 的宽长比为1 ∶N,根据电流镜比例镜像关系可得:

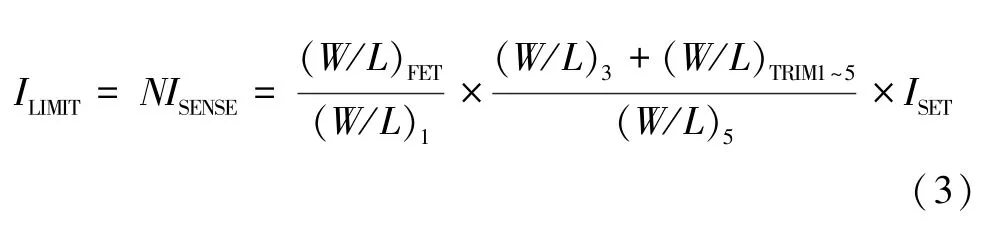

因M3、MTRIM1~5与M5 的栅源电压相等,在忽略沟道长度调制效应的情况下,流过采样管的电流即采样电流值为:

流过功率管的电流即限流值为:

其中,MTRIM1~5的宽长比为1.5 ∶3 ∶6 ∶12 ∶24,在未修调情况下,S13~S16 处于断开状态,S17_N 处于闭合状态,MTRIM1~5与M3 并联。式(3) 中M3、MTRIM1~5、M5 的宽长比为17 ∶24 ∶2,N为11223,ISET为5.3 μA,可计算得,限流值ILIMIT为1.219 A。

通过修调电路控制5 组开关的闭合与关断,改变MTRIM1~5与M5 比例关系,即改变流过采样管M1 的电流大小,可对限流值进行微调以达到预期指标。其中,ITRIM1为流过M1 最小修调位的电流,最小修调位可修调的电流为:

则流过功率管电流可修调的最小电流为:

式(5)中,MTRIM1、M5 的宽长比为1.5 ∶2,最小修调电流为ILIMIT的3.7%。根据MTRIM1~5的宽长比,由式(3)计算,可实现对限流值-58.5%~54.9%的修调,在一定程度上减小流片、封装的误差,使其保证限流精度。

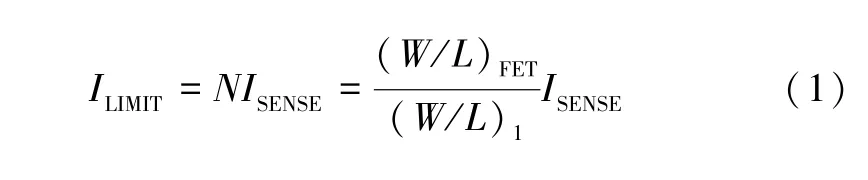

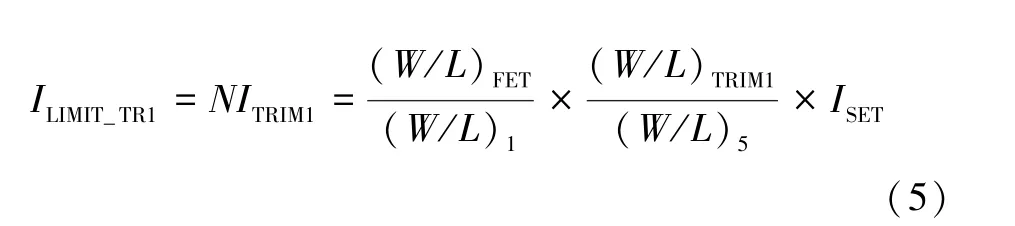

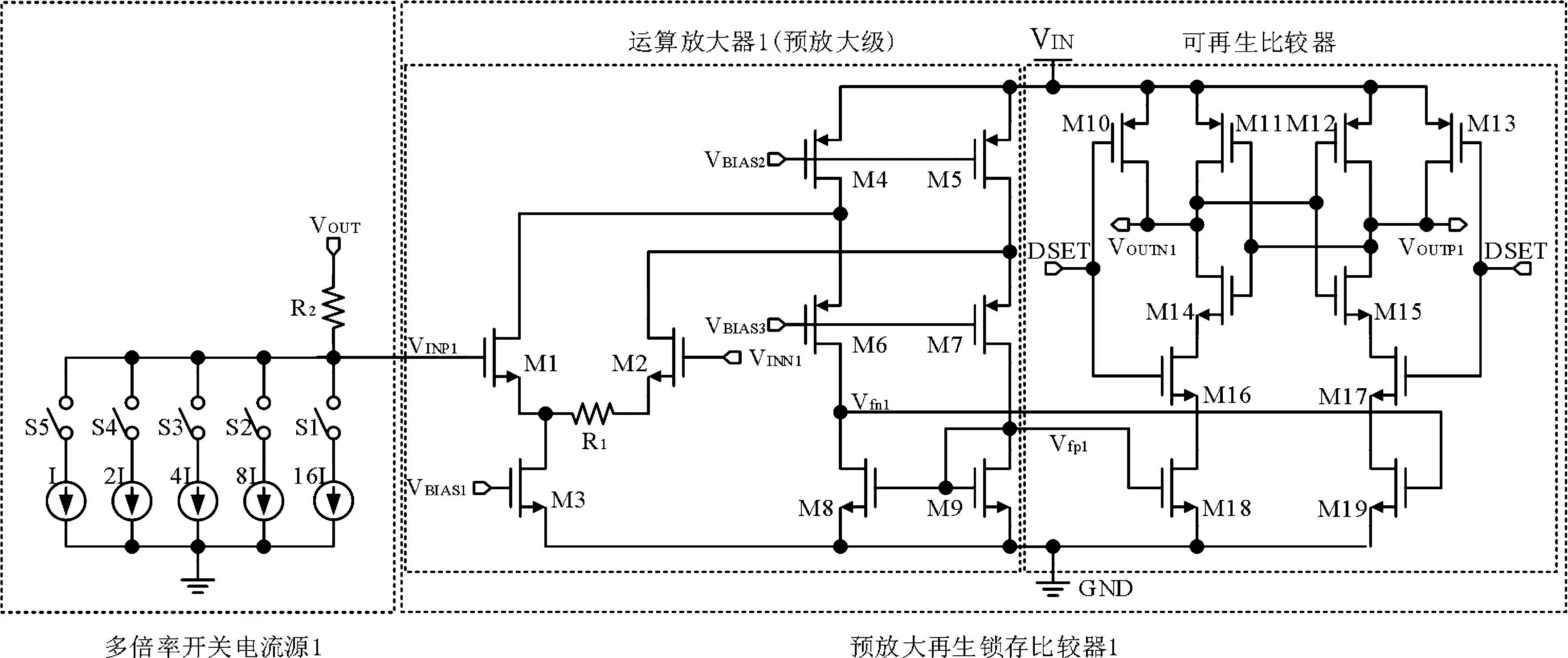

1.3 失调电压校正设计

失调电压校正电路由多倍率开关电流源、预放大再生锁存比较器与逻辑控制电路三部分组成,如图3所示。其通过可再生比较器监测运放两输出端电压,判断运放失调情况,由逻辑控制电路调节多倍率电流源开关电路,改变差分对管正向输入端电压VINP1,从而以电流补偿的方式在运放输入端减小失调电压。当CLK 为高电平时,对运算放大器1 进行失调电压校正。其中,S1~S5 为逻辑控制电路输出信号,I、2I、4I、8I、16I中的I为偏置电流,VBIAS1、VBIAS2、VBIAS3均为偏置电压,VOUTN1、VOUTP1为可再生比较器输出信号。

图3 失调电压校正电路Fig.3 Offset voltage correction circuit

当DSET 为低电平时,可再生比较器处于复位阶段,M16、M17 关断,M10、M13 导通,分别将比较器输出电压VOUTN1、VOUTP1上拉至VIN,避免在比较过程中放电不完全引起失配,导致结果错误;当DSET为高电平时,可再生比较器处于比较阶段,M16、M17 导通,M10、M13 关断。初始状态VINP1与VINN1电压相等,Vfp1

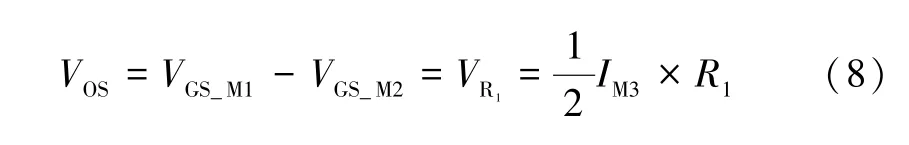

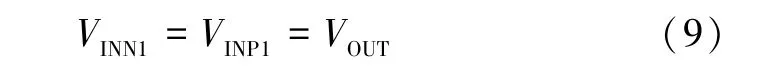

电阻R1的引入,一方面增大了运算放大器的共模输入范围,同时也引入失调电压,使得运算放大器具有较大失配。其中:

流过M3 的电流IM3与多倍率开关电流源1 中偏置电流为比例镜像关系:

由式(6)和(7)可计算引入失调电压VOS约为:

式中,VGS为栅源压差。

电路开始工作时:

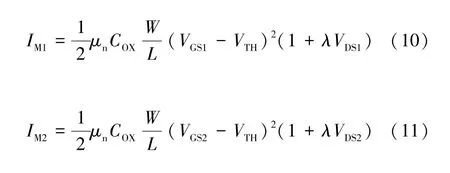

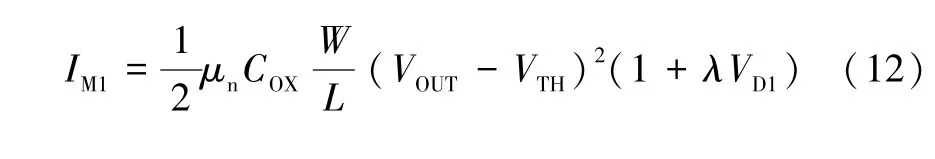

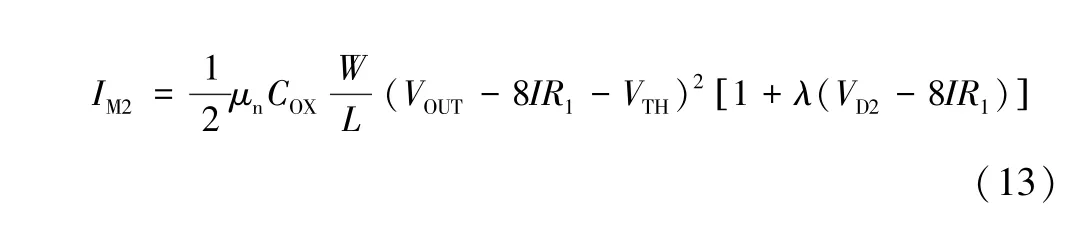

流过M1 和M2 管的电流分别为:

式中:μn为电子迁移率;COX为单位面积的栅氧化层电容;W/L为MOS 管的宽长比;VTH为MOS 管的阈值电压;λ为沟道长度调制系数;VDS为漏源压差。

由式(9)和(10)可计算流过M1 管的电流为:

由式(7)~ (9)和(11)可计算流过M2 管的电流为:

由式(12)和(13)可知,IM1>IM2,则经过可再生比较器的输出VOUTP1为高电平,VOUTN1为低电平,将输出结果传递至逻辑控制电路,控制多倍率开关电流源1 中S1 闭合,持续至下一个CLK 的上升沿。

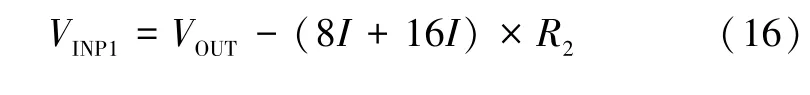

此时,由于S1 闭合,VINP1电压降低为:

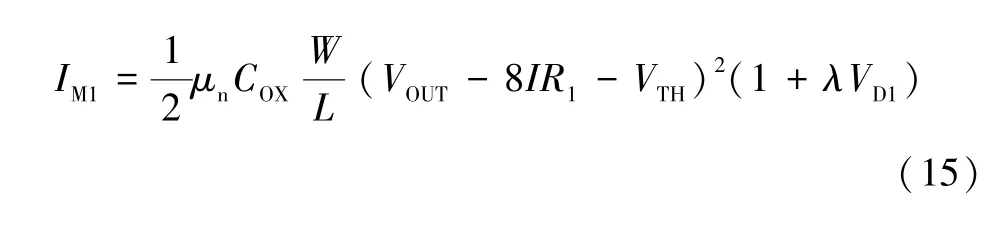

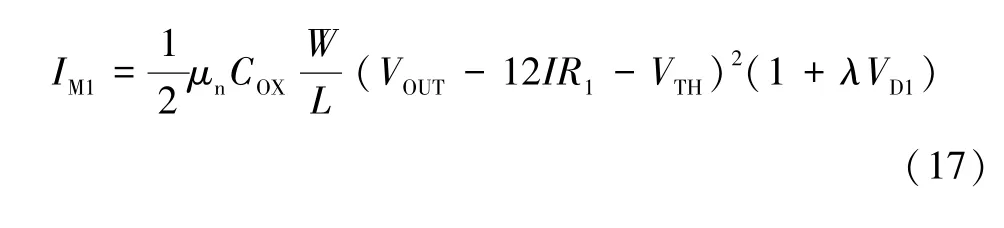

由式(6)、(7)、(10)和(14)可计算流过M1 管的电流为:

由式(13)和(15)可知,IM1>IM2,则可再生比较器的输出仍为VOUTP1高电平,VOUTN1低电平,将输出结果传递至逻辑控制电路,控制多倍率开关电流源1 中S2 闭合,持续至下一个CLK 的上升沿。

此时,由于S2 闭合,VINP1电压降低为:

由式(6)、(7)、(10)和(16)可计算流过M1 管的电流为:

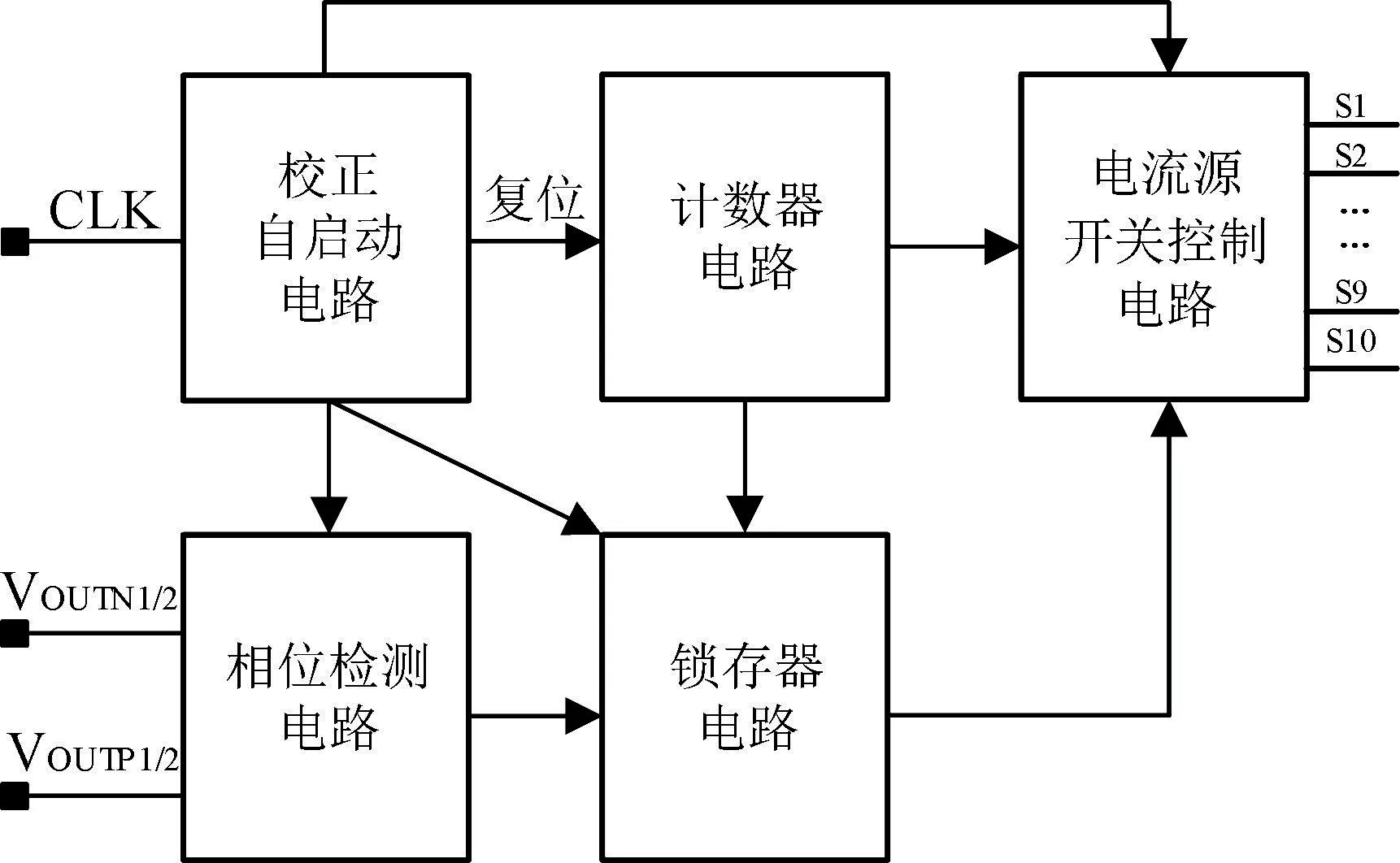

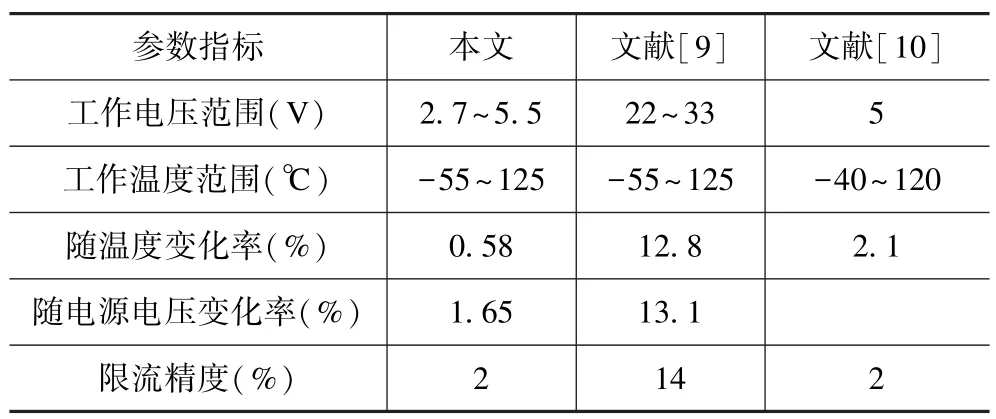

由式(13)和(17)可知,IM1 在CLK 高电平期间,S1~S5 均由预放大再生锁存比较器输出经过逻辑控制电路控制其闭合与断开,完成失调电压校正,得到一低失调的运算放大器1,用于在CLK 为低电平时,与限流电路构成限流环路,能够更为精准地进行采样及限流。 在不打断转换过程的前提下,以运算放大器的输出信号为基础,达到校正运算放大器失调电压的目的[11-14]。逻辑控制电路由校正自启动电路、相位检测电路、锁存器电路、计数器电路以及电流源开关控制电路五个部分构成,如图4 所示。校正自启动电路主要是为计数器提供复位信号;相位检测电路主要是检测可再生比较器输出信号VOUTN1/2、VOUTP1/2的变化;锁存器电路主要采集相位检测电路输出结果并进行锁存,将锁存结果与计数器信号叠加提供给电流源开关控制电路,并由其输出控制多倍率开关电流源电路。 图4 逻辑控制电路结构框图Fig.4 Logic control circuit block diagram 通过校正自启动电路检测CLK 的上升/下降沿,并在边沿处产生较小的高脉冲信号,为计数器电路提供复位信号;当计数器复位完成后,计数器在内部时钟CLK_INT 下开始计数,并在每个时钟下降沿处依次产生一个高脉冲信号,将其传送到电流源开关控制电路中;相位检测电路通过采集可再生比较器的相位信号VOUTN1/2、VOUTP1/2的变化,为锁存器电路提供输入信号;锁存器电路受计数器电路的输出控制,即在每个时钟下降沿处唯一确定开启对应的数据传输通道,完成对VOUTN1/2、VOUTP1/2信号的采集,并在下一个CLK_INT下降沿处关闭通道实现数据锁存;锁存器电路与计数器电路共同作用于电流源开关控制电路,产生5 个脉冲信号。当VOUTP1为低电平,VOUTN1为高电平时,经相位检测电路检测为无效信号(无需校正);当VOUTP1为高电平,VOUTN1为低电平时,经相位检测电路检测为有效信号(需校正)。在5 个脉冲期间,检测结果为无效信号时,其脉冲只维持一个CLK_INT 周期;检测结果为有效信号时,其脉冲维持到下一个CLK 的上升沿处复位并重新采样。整个校正过程分为CLK 的高/低电平控制过程,且相互独立,低电平时采取与高电平同样的方式对VOUTN2、VOUTP2进行检测,输出相应的低电平控制信号。 为减小封装引入的工艺误差、寄生电阻以及寄生电感等对限流精度的影响,设计了修调电路。可通过读入修调编码来找到对应熔丝的信息位置,控制熔丝通断[15],从而改变流过采样管的电流,对限流值进行修调,使其符合预期限流阈值范围,保证限流精度。修调电路由修调启动电路、移位寄存器、译码器电路以及熔丝烧写电路四部分组成,结构框图如图5 所示。修调电路由双引脚控制,通过修调启动电路控制修调电路开启,写入修调编码储存至移位寄存器,由译码器电路对修调编码进行译码,得到有效的熔丝信息,并输入至熔丝烧写电路,控制对应熔丝通断。 图5 修调电路结构框图Fig.5 Modification circuit block diagram 由修调启动电路中的高低电平计数器开始计数,当计数至5 个时钟下降沿,并且高电平电压为7 V,即可进入修调模式。此时,通过移位寄存器写入时钟信号和修调编码。修调编码由14 位二进制代码组成,1~3 位为预修调控制(A0~ A3),4 位为测试控制(B0),5~11 位为数据位(D0~D6),12~13 位为控制位(C0~C1),14 位为结束位(STOP),如图6 所示。 图6 修调编码示意图Fig.6 Schematic diagram of trimming coding 将修调编码储存在移位寄存器中,通过译码器电路将修调编码译码,形成有效的修调模块地址信息和熔丝地址位信息,作为熔丝烧写电路的输入信号,熔丝烧写电路根据译码器电路提供的信号来熔断对应的熔丝,如图7 所示。其中,VBIAS1、VBIAS2为偏置电压,TR_MODE 为修调模式使能信号,TR_FUSE 为修调编码的数据位(D0~D6),TR_SEL 为修调编码的控制位(C0~C1),S13~S17 为修调控制信号。 图7 熔丝烧写电路Fig.7 Fuse programming circuit 当熔丝未熔断时,S13/14/15/16/17 保持低电平;反之,S13/14/15/16/17 保持高电平。当熔丝烧写电路的TR_MODE、TR_FUSE、TR_SEL 被选通后,控制器输出N 为高电平,M1 管导通,产生大电流熔断熔丝,使得M 点变为低电平,进而使输出端口S13/14/15/16/17 翻转为低电平。当S13/14/15/16/17 电平发生翻转时,图2 中限流电路对应的修调位开关闭合,利用采样管与功率管的比例关系,改变流过采样管电流的大小,实现对限流值的修调,保证限流精度。 基于0.18 μm 1P3M BCD工艺设计,利用Cadence Virtuoso 进行仿真。经验证,限流电路仿真结果如图8 所示,在输入电源电压VIN为5 V,温度为25℃,负载电阻RLOAD为2 Ω 的条件下,曲线D 为未修调情况下的限流值1.217 A,与理论限流值1.219 A 基本一致。曲线B 是对曲线D 进行修调,可实现最大的修调限流值1.865 A,修调率为+53.3%。曲线C 对曲线D 进行修调,可实现最小的修调限流值0.5137 A,修调率-57.8%,均符合设计预期。 图8 限流电路仿真图Fig.8 Simulation diagram of current limiting circuit 限流值随温度变化曲线如图9 所示,在-55~125 ℃温度范围内,可看出限流值随温度变化的最大值为1.217 A,最小值为1.210 A,差值为7 mA,变化率为0.58%。 图9 限流值随温度变化曲线Fig.9 Curve of current limiting value versus temperature 图10 为电源电压VIN在2.7~5.5 V 范围内的限流值变化曲线,可看出限流值随电源电压增大而增大,限流值最大值为1.23 A,最小值为1.21 A,差值为20 mA,变化率为1.65%。 图10 限流值随电源电压变化曲线Fig.10 Curve of current limiting value versusVIN 验证结果表明,限流值与理论预期基本一致,可实现2%的限流精度且随温度以及电源电压变化范围较小,满足设计需求。 表1 为本文与其他文献的限流电路参数指标对比,在温度环境基本一致的情况下,本文限流值随温度变化最小。限流值随电源电压变化较小。本文限流精度优于文献[9],与文献[10]限流精度一致,但本文限流值变化率较低,整体限流能力更优。 表1 与其他文献的限流电路参数指标对比Tab.1 Compared with the parameters of current limiting circuit in other literatures 本文设计了一种带失调电压校正功能的高精度限流电路,通过采样管采样技术提高采样精度,利用失调电压校正技术降低运放失调电压,使得限流电路采采低失调运放来进行反馈控制,并通过数字修调技术对限流值偏差进行调节,实现高精度限流。基于0.18 μm 1P3M BCD 工艺进行仿真验证,当功率管电流超过限流阈值时,将输出电流稳定在1.217 A 左右,限流精度可达2%,限流值随电源电压和温度变化率分别为1.65%和0.58%,限流值可实现修调范围-58.5%~ 54.9%。该电路可应用于精度需求较高的DC-DC、AC-DC、限流开关等芯片设计。1.4 逻辑控制电路设计

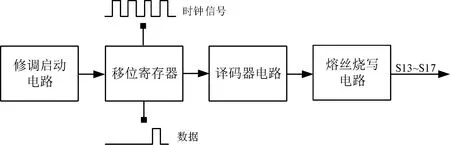

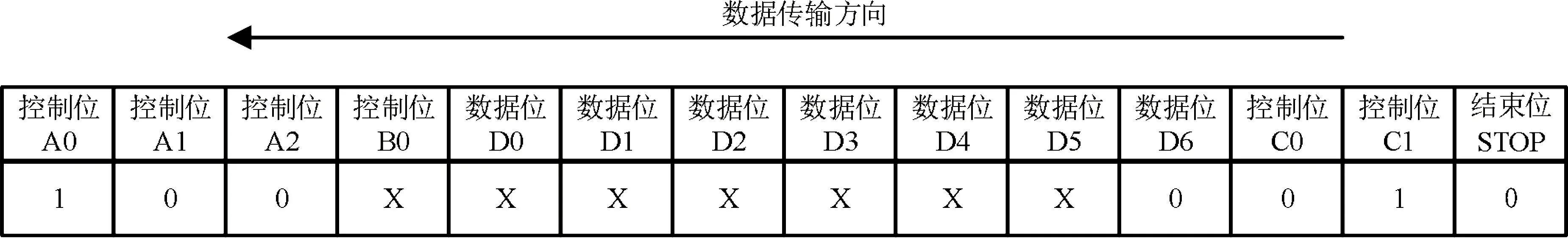

1.5 修调电路设计

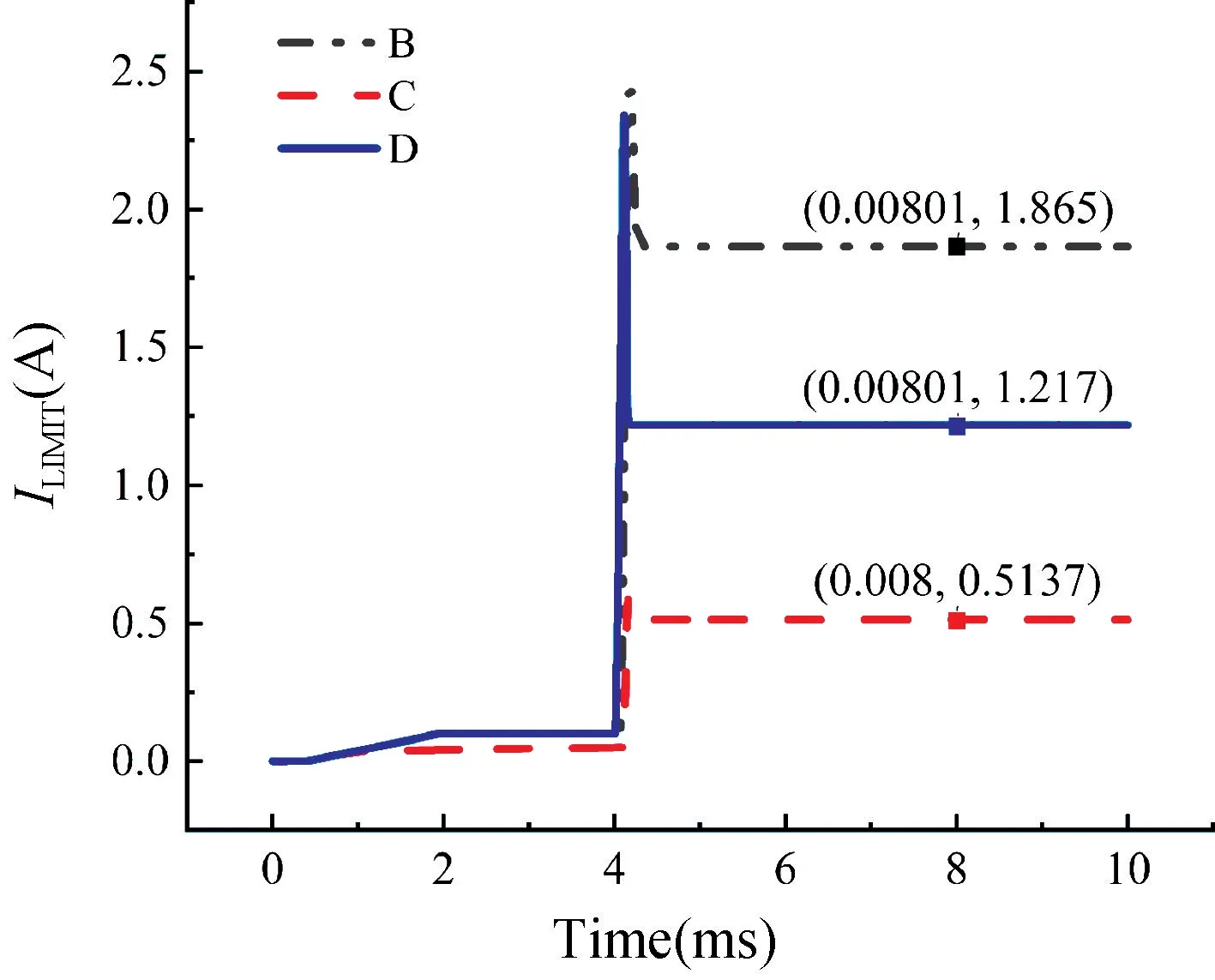

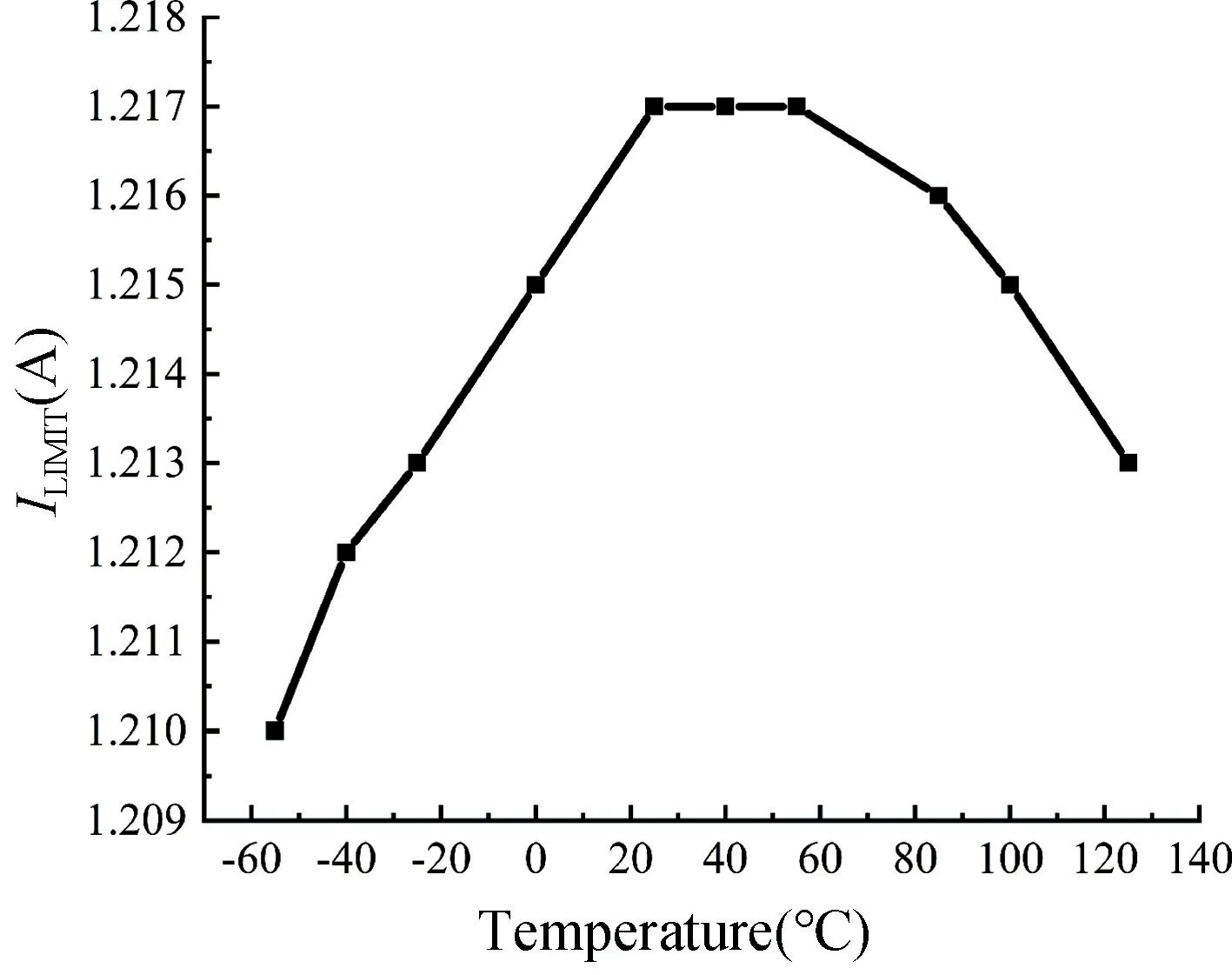

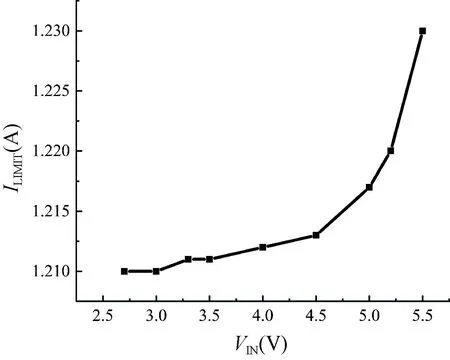

2 仿真结果与讨论

3 结论