基于SCAPS仿真分析CZTSe薄膜太阳能电池的性能影响因素

2022-06-02方奕锟谈晓辉韩修训

方奕锟,谈晓辉*,韩修训

(江西理工大学 材料冶金化学学部光电功能材料与器件研究所,江西 赣州 341000)

铜锌锡硫硒(CZTSSe)因具有高吸光系数(>104cm-1)、可调的光学带隙(1.0~1.5 eV)和无毒、地壳储量丰富的组成元素,被认为是极具应用前景的光伏材料,有望取代铜铟镓硒(CIGS)和碲化镉(CdTe)薄膜太阳能电池[1].然而,目前CZTSSe薄膜太阳能电池的转换效率记录仅为13%[2],远低于其理论转换效率[3].与CIGS太阳能电池相比[4],严重的开路电压损失和相对低的填充因子是制约CZTSSe电池性能的主要原因.CZTSSe电池器件的结构较复杂,影响器件效率的因素也较多,而且往往在不同的条件下,同一因素对器件性能的影响程度也不一样[5].研究者通过阳离子掺杂、替换缓冲层、优化硒化工艺等各种方法提高CZTSSe太阳能电池性能[6],但CZTSSe电池转化效率的进展仍然比较缓慢.通过仿真预测各种因素对CZTSSe电池性能的影响,可以为实验提供理论指导.目前已开展了很多CZTSSe器件仿真工作.Patel等[7]通过仿真研究了CZTS吸收层的厚度和受主浓度对器件性能的影响;Xu[8]揭示了渐变载流子浓度对CZTS光伏性能的影响规律;Conde等[9]深入研究了体缺陷密度对器件效率的影响;Kanevce等[10]的仿真结果表明局部二次相会导致严重的开路电压损失;Mether等[11]分别模拟了载流子在cliff-和spike-型导带边的跃迁行为等.大部分的仿真工作均是针对某些因素优化CZTSSe电池的性能表现,而未与实际制备的一般器件进行综合比较和分析或指出有效提升实际电池效率的关键因素和途径.

文中基于实际制备的CZTSe电池,采用SCAPS分别研究了串/并联电阻、体相深能级缺陷态和界面复合对CZTSe太阳能电池性能的影响,并综合分析了影响该器件性能的主要因素和可能的性能提升空间.

1 器件结构及仿真方法

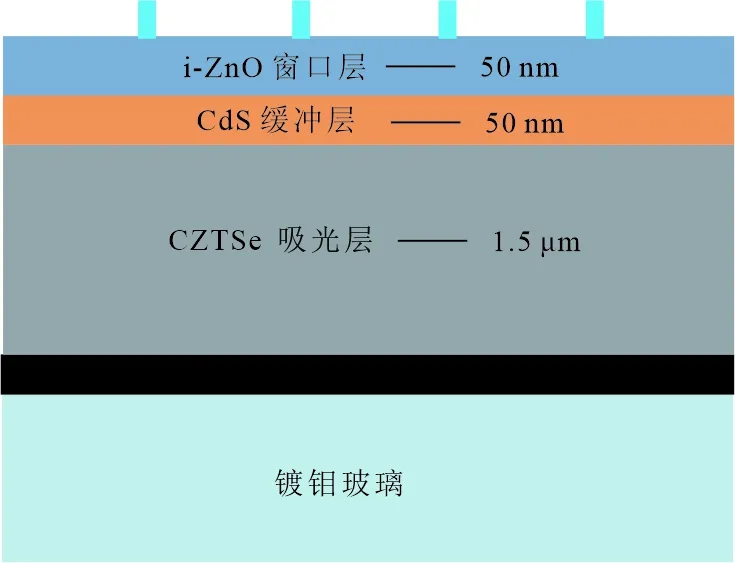

仿真所采用的器件主体结构从入光侧至玻璃基底依次为Al电极、透明电极、本征ZnO层、CdS缓冲层、CZTSe吸光层和Mo背接触电极,如图1所示各层厚度已在图中标注.

图1 器件结构示意图

仿真过程采用一维光伏器件数值仿真软件(Slar cell capacitance simulator, SCAPS)完成.SCAPS在解决一维能带、本征缺陷态、掺杂元素等复杂分布和界面态复合问题方面具有突出的数值分析能力,非常适合于铜基薄膜电池体系的仿真研究和设计[12].其基本原理是通过有限差分方法数值求解约束条件下的泊松方程和连续性方程:

其中,ε为介电常数;φ为电势;q为电子电量;p和n分别为空穴和电子浓度;ND和NA分别为施主和受主浓度;Jn和Jp分别为电子电流密度和空穴电流密度;R和G分别为电子和空穴的复合率和产生率.

为使器件仿真具有实际指导意义,仿真过程基于溶液法制得的具有7.53%转化效率的CZTSe电池展开.首先,以串联电阻Rs、并联电阻Rsh、体相深能级缺陷态浓度和界面缺陷态密度作为拟合参数,对器件实际所测得的电流密度—电压(J-V)曲线进行拟合,获得与实验结果基本相符的拟合结果;然后分别以上述参数为变量,在合理范围内研究其在单一作用下对器件性能的影响规律和内在机制,揭示器件性能在优化后的可能提升程度;在此基础上总结改善实际器件转化效率的有效途径和器件可以达到的最优性能.

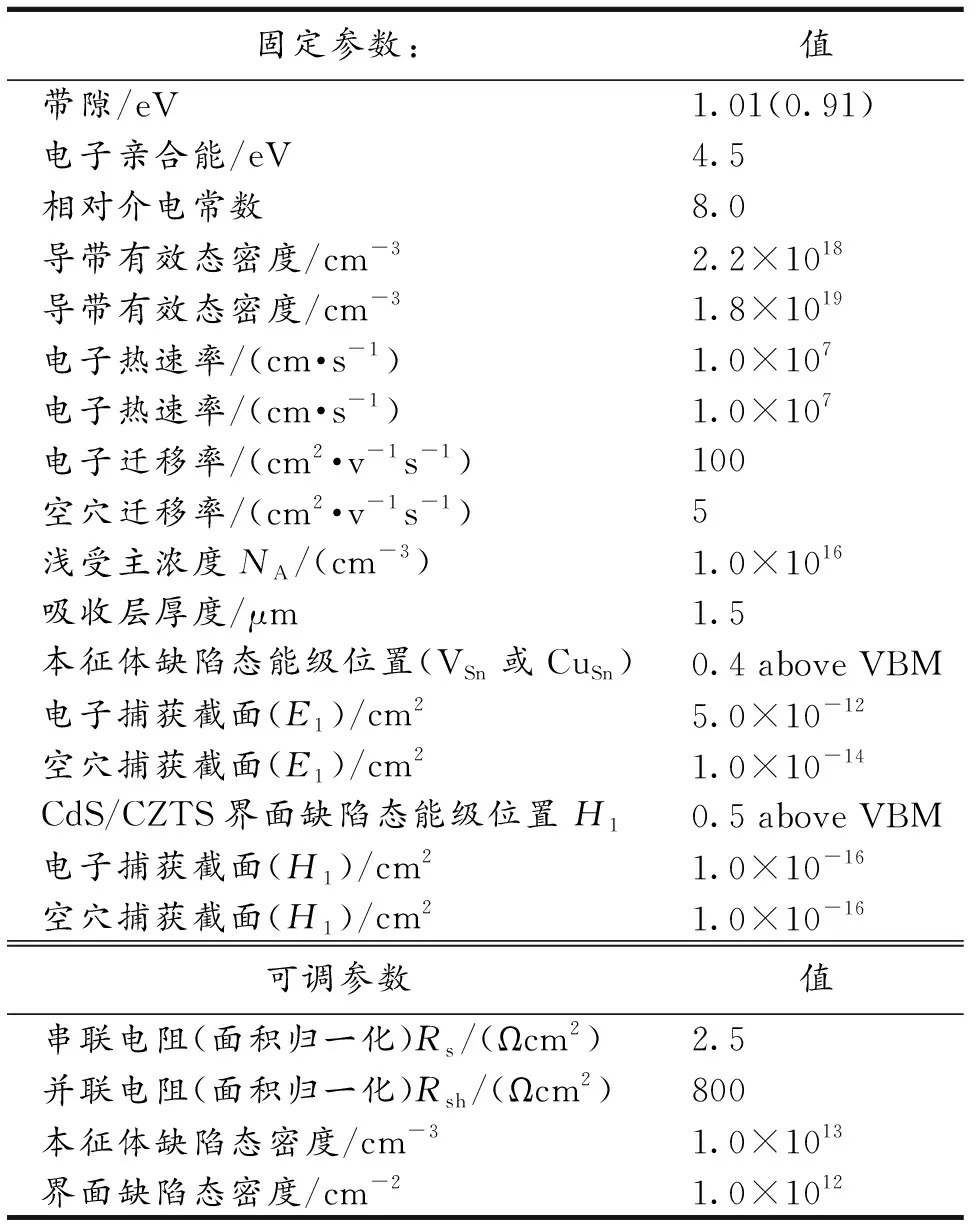

ZnO窗口层和CdS缓冲层材料性能已经研究的非常成熟,因此在拟合过程中,两者的基本材料参数直接引自程序自带的数据例库(参照普遍采用的Numos CIGS baseline结构中的参数值).对于CZTSe吸光层,带隙、空穴浓度及空穴迁移率则采用所制得CZTSe薄膜的实测值,分别约为1.01 eV,1×1016cm3及5 cm2·v-1s-1.其中空穴浓度直接以1×1016cm3浅受主的方式引入,对应于形成能比较低的CuZn替位受主.同时,由于CZTSe为四元化合物体系,组成元素的复杂性也导致产生众多深能级本征缺陷态,比较典型的有VSn、CuSn和SnZn等[13].相应地,与上述替位缺陷相关的一些受主-施主缺陷簇也很容易形成,其中[CuZn+ZnCu]和[2CuZn+SnZn]缺陷簇的形成能都很低.[2CuZn+SnZn]等缺陷簇的大量存在会产生带尾态,致使带隙变小、载流子局域化;而CuSn、SnCu、SnZn等深能级缺陷有可能充当复合中心[14].基于此,为使模拟结果更加清晰,在拟合过程中并不指认区分具体缺陷态的种类.参考理论计算得出的各类缺陷的能级位置,在价带以上~0.4 eV引入决定体相复合的本征深能级缺陷态,与可能存在的VSn或CuSn相关联;在界面处价带以上约0.5 eV引入决定异质界面复合的界面态,与可能存在的SnZn或其他缺陷相关联;缺陷态的捕获截面沿用文献中的典型值不变,而将缺陷态的浓度作为变量拟合实验结果.拟合参数的合理性还可通过与实验测得的载流子寿命相比较来进一步验证.带尾态所引起的能带带边涨落是影响开路电压的另一重要因素,在拟合过程中沿用IBM团队的做法,即直接利用电子带隙替代光学带隙计入带尾态的影响(两者相差约100 meV)[15].其他相关材料参数详见表1.

表1 CZTSe基本材料参数

2 结果与讨论

2.1 器件拟合

图2给出了在采用表1参数下所得到的J-V曲线拟合结果.可以看到,理论计算值与实验值吻合较好.此时的串联电阻较大,为2.5 Ωcm2;其与较小的并联电阻(约800 Ωcm2)一起决定了器件只有约54%相对较低的填充因子.而此时E1约1.0×1013cm-3和H1约1.0×1012cm-2的缺陷态浓度分别对应2 ns的电子寿命和1.0×103cm·s-1界面复合速率,少数载流子寿命值基本与实测值相符.说明上述参数在一定程度上能够较好描述所制得CZTSe薄膜电池的器件行为.

图2 采用表1的材料参数得到J-V曲线 (括号里为拟合值)

2.2 串、并联电阻对器件性能的影响

在此基础上,首先保持其他所有基本器件参数不变,在一定范围内考察了串联电阻和并联电阻对器件性能的影响,如图3所示.其中,图3a给出了Rs在0.01至2.5 Ωcm2变化时各器件性能参数的变化趋势,可以看到,串联电阻Rs的进一步减小对Voc和Jsc影响不大.而随着Rs的减小,填充因子可从原来的54%提升到71%.相应于填充因子的改善,器件转换效率可明显提高到9.98%.图3b给出了在800 Ωcm2基础上将并联电阻增加至1×104Ωcm2时各器件参数的变化.模拟结果显示,进一步优化Rsh对器件整体性能的提升效果有限,光电转换效率仅由7.55%提升至7.61%.亦即,目前器件的并联电阻不是限制转换效率的主要因素.我们在现有器件基础上,模拟给出了单纯通过改善串/并联电阻提升器件效率最大可能程度,比较结果示于图3c.当同时将Rs降至0.01 Ωcm2、Rsh增至1×104Ωcm2后,得益于填充因子的有效提升器件效率可达10.14%;因此可知,改善串联电阻是将当前CZTSe电池器件性能提升至~10%的有效手段.

图3 各参数对器件性能的影响及 经过参数优化后的J-V曲线

2.3 体相深能级缺陷态对器件性能的影响

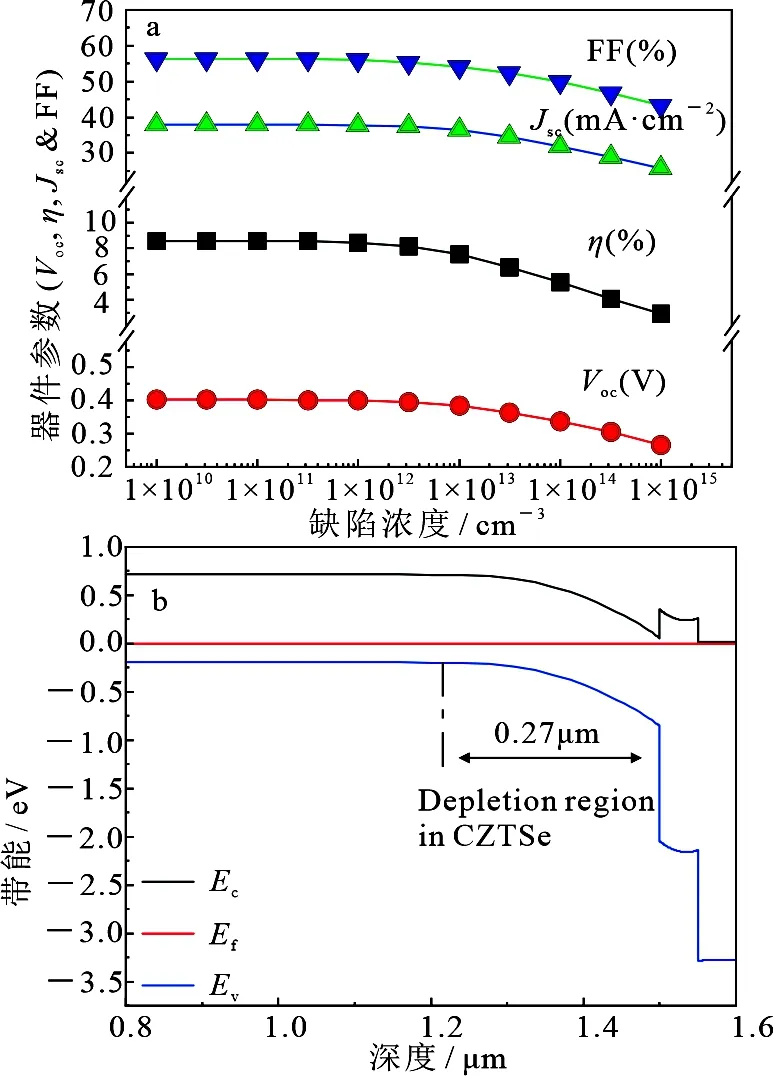

E1作为深能级缺陷态对光生载流子的寿命有着重要影响,导带中的电子和价带中的空穴通过深能级发生非辐射复合的行为遵循Schockley-ReadHall(SRH)机制,SCAPS对该过程进行了精确的计算和描述.图4a给出了深能级缺陷态浓度在1.0×1010cm-3和1.0×1015cm-3范围内变化时对器件主要参数的影响.可以看到,体相深能级缺陷态所引起载流子的非辐射复合对所有主要器件参数都有影响,影响程度的强弱取决于缺陷态浓度的大小,当缺陷态的浓度低于3.162×1012cm-3(依据本计算过程中所取的浓度间隔)时,器件参数基本不随其浓度的大小而改变;当浓度超过这一临界值时,随缺陷态浓度的增加器件性能迅速衰减.

为解释上述现象,进一步考察了在浓度达到3.162×1012cm-3缺陷态的作用下少数载流子(电子)的寿命,大约为6.3 ns.结合电子的迁移率,得到此时对应的扩散长度约为1.3 μm.图4b给出了所考察器件的能带结构,平衡状态下在CZTSe吸光层一侧可形成宽为约为0.27 μm的耗尽层.理论上太阳能电池光生载流子的有效收集范围为少数载流子的扩散长度和耗尽层宽度之和,本条件下对应于1.3+0.27=1.57 μm的有效收集范围,该范围恰好超出了吸光层的厚度1.5 μm.由此可以理解,小于3.162×1012cm-3的缺陷态浓度皆可满足整个吸光层范围内光生载流子的有效收集,因而即便再进一步降低缺陷态的浓度,也不会对器件性能带来更多的贡献.但当缺陷态浓度高于临界值时,光生载流子寿命进一步减小,降低了其扩散至耗尽层的几率,进而影响载流子的收集效率,短路电流变小;同时,光生载流子寿命减小引起扩散长度变短,使暗电流增加,进而影响开路电压和填充因子.这也是缺陷态浓度高于1.0×1013cm-3后器件性能迅速劣化的主要原因.

图4 深能级缺陷态浓度对器件性能的影响及 平衡状态下器件的能带结构

基于以上分析可知,缺陷态的浓度越低无疑越易于获得高效率的电池器件.但根据吸光层的吸光深度确认恰当的载流子扩散长度后,只要将深能级缺陷态的浓度限制于获得该扩散长度的最低浓度范围内即可满足较高器件性能的要求.另外值得注意的是,在上述器件模拟过程中并没有考虑背接触界面复合的影响.如果背界面也存在较高的界面态,也会很大程度上影响光生载流子的有效扩散和收集,该影响主要表现在对长波长太阳光的转化上.

2.4 界面复合对器件性能的影响

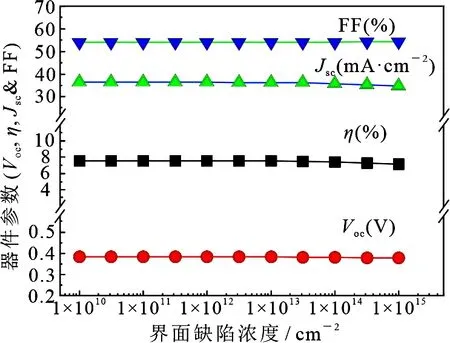

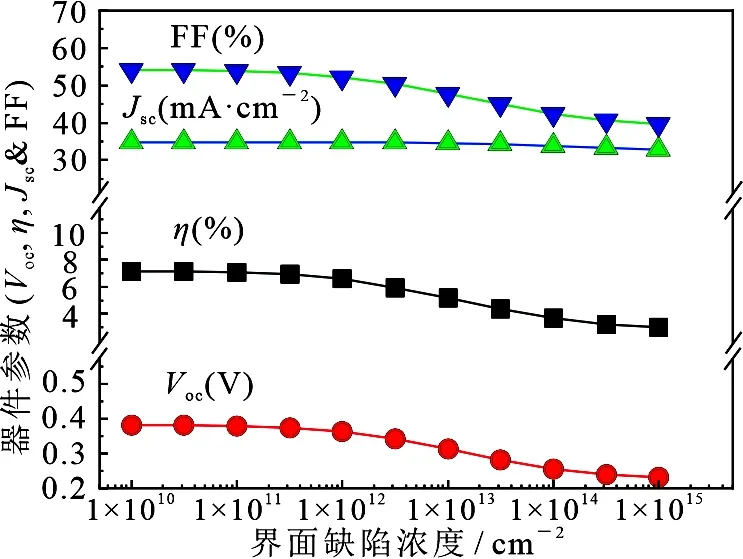

目前的研究认为,CZTSSe太阳能电池中存在过多的界面态是器件开路电压损失较大的主要原因之一.因此,在考察了串/并联电阻和本征深能级复合中心对器件性能的影响规律后,保持基础器件的其他参数不变,在较大范围内模拟计算了界面态密度对电池器件主要参数的影响,计算结果如图5所示.可以看到,器件各项主要参数受界面复合影响而表现出的变化规律与预想不太一致.即便界面缺陷态的密度达到1×1015cm-2(对应1×106cm·s-1的高界面复合速率)仍未观察到器件性能的大幅衰减.同样,在1010至1015cm-2界面态密度变化范围内,开路电压也只是从0.383 V稍降低至0.378 V.因此,在当前的器件结构下,单纯界面态的增减不会对器件性能带来大的改变.

图5 界面缺陷浓度对器件性能的影响(spike-like结构器件)

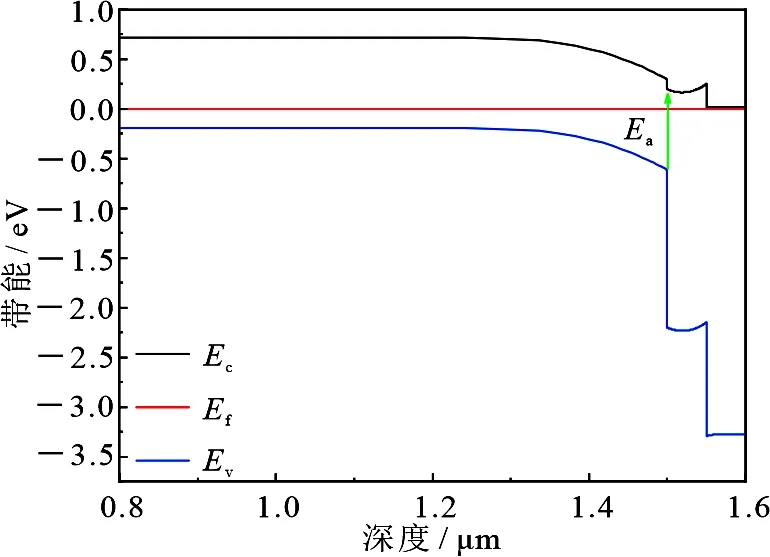

事实上,早在CIGS电池器件的研究过程中就已发现,界面的能带结构排布会对器件性能产生重要影响.当CdS缓冲层导带带边高于CIGS的导带带边时会形成正导带带阶,称为spike-like结构;而当缓冲层导带带边低于CIGS的导带带边则形成负导带带阶,称为cliff-like结构.而一定范围内的正导带带阶(0<ΔE<0.4 eV)是有利于提升器件性能的[17].本器件结构中CdS的电子亲合能为4.2 eV,CZTSe为4.5 eV,两者形成了0.3 eV的理想正导带带阶(参见图4b),这可能是该器件中界面复合影响较小的潜在原因.为了验证该推测,同时考虑到约1 eV的CZTSe吸光层带隙偏小,将来的工作也将致力于开发导带带边更高、带隙更宽的高S组分CZTSSe吸光层,我们进一步将CZTSe的电子亲合能降至4.1 eV,保持带隙等所有其他基本器件参数不变.此时CdS与电子亲合能调整后的CZTSe形成了约-0.1 eV的导带带阶.仍然在1010至1015cm-2界面态密度变化范围内考察其对各器件参数的影响,计算得到的结果如图6所示.可以看出,在cliff-like结构中,即便是CdS的导带带边只比CZTSe低了0.1 eV,在整个考察范围内开路电压从0.381 V大幅降至0.231 V,FF变化趋势与Voc一致,相应的转化效率由最初的7.13%降至约3.0%.这一结果说明界面缺陷态密度的变化,对具有负导带带阶结构器件的界面复合产生了更大的影响.为了更形象的阐述这一原因,图7给出了平衡状态下cliff-like结构器件的能带图.CdS缓冲层导带带边低于CZTSe导带带边时,发生复合的空穴及电子可分别来自于界面两侧,复合激活能Ea小于CZTSe带隙(图中箭头所示);而缓冲层与CZTSe形成正导带带阶时(图4b),复合激活能与CZTSe带隙一致,而且正导带带阶值控制在一定范围内(<0.4 eV)时,不会阻挡载流子的有效传输.cliff-like结构中更小的复合激活能意味着载流子复合更容易发生;因此界面缺陷态密度增大时,对该结构的界面复合影响程度也会更显著.

图6 界面缺陷浓度对器件性能的影响 (cliff-like结构器件)

图7 平衡状态下具cliff-like导带带阶结构器件的 能带分布图

由此可见,除了尽可能降低界面态的生成外,寻求能够与光吸收层形成理想正导带带阶排布的缓冲层材料也是提升器件性能的有效手段.

2.5 器件性能提升空间的综合分析

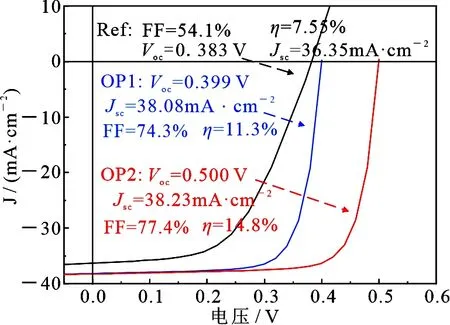

综合以上对几个主要影响因素的分析,可以推测在串/并联电阻、体缺陷复合和界面复合均进行一定程度的优化后,器件性能将有明显的提升.且在当前的器件结构下,减小串联电阻的效果最明显.图8比较了基础器件和进行不同程度优化后器件的J-V曲线,可以看到,与基础器件相比,OP1采用Rs=0.01Ωcm2、Rsh=1×104Ωcm2;E1=1.0×1012cm-3;H1=1.0×1010cm-2的优化参数后,FF可获得大幅改善,Jsc有一定程度的提升,相应光电转化效率将达到11.3%. 但仅靠上述参数的优化尚不能有效改善Voc,当进一步消除约100 meV带尾态所造成的带隙收缩后,Voc才能在此基础上有大幅改善(器件OP2),此时预期转化效率可达14.8%.

OP1(Rs=0.01Ωcm2、Rsh=1×104Ωcm2;E1=1.0×1012cm-3;H1=1.0×1010cm-2)

3 结束语

文中基于实际制备的CZTSe电池器件,采用SCAPS对其J-V特性进行了拟合,并通过仿真考察了串/并联电阻、体缺陷态浓度、界面缺陷态密度四个关键因素对器件性能的影响,仿真结果表明,串联电阻是导致器件填充因子过低的主要限制因素,进一步改善并联电阻对器件性能的提升效果不明显;体相深能级缺陷态密度的高低对载流子寿命和扩散长度有重要影响,其对器件性能的影响存在一临界值,只有高于该临界值时,所有器件参数才会出现明显的劣化;界面复合对开路电压的影响程度与界面能带结构排布密切相关,当界面处形成负导带带阶时,复合激活能小于吸光层带隙,界面缺陷态引起的界面复合程度增强,可致使开路电压显著降低.

结合上述几个关键因素的分析,文中用于仿真的CZTSe器件预期具有以下的性能提升空间,重点降低串联电阻,适度增加并联电阻、降低体相缺陷态和界面缺陷态密度,将大幅改善填充因子,有效提升短路电流,转化效率可提升至11.3%;若要进一步改善开路电压,则需要消除带尾态的影响,在此情况下转化效率有望提高到14.8%.