基于标准CMOS工艺的光电浮栅突触研究

2022-05-12高旭斌毛陆虹

谢 生,高旭斌,毛陆虹

基于标准CMOS工艺的光电浮栅突触研究

谢 生1, 2,高旭斌1,毛陆虹3

(1. 天津大学微电子学院,天津 300072;2. 天津市成像与感知微电子技术重点实验室,天津 300072;3. 天津大学电气自动化与信息工程学院,天津 300072)

作为神经形态视觉感知系统的基本单元,光电突触需实现光敏和突触双重功能.本文基于TSMC 180nm标准CMOS工艺提出了一种由两个PMOS晶体管构建的光电浮栅突触结构,并利用浮栅电压表征突触权重.其中,一个PMOS管工作在光电混合模式,在光信号和电信号的刺激下,突触的浮栅电压分别呈现增加和降低特性,以此实现突触的兴奋性和抑制性功能;另一个PMOS管工作在隧穿模式,并通过Fowler-Nordheim(FN)隧穿机制修正突触权重.基于光电浮栅突触的电路模型,设计了用于像素识别的单元电路,搭建了3×3的像素阵列,并分析了无噪声和有噪声两种情形下的二值图像“+”识别.仿真结果表明,在基础光强为0mW/cm2和75mW/cm2的无噪情形和引入0.5mW/cm2噪声的有噪情形下,所设计的光电浮栅突触均可实现二值图像识别,并具有一定的抗噪声能力.

神经形态计算;CMOS;光电突触;浮栅;突触权重

为了突破传统冯·诺伊曼计算机架构带来的数据传输瓶颈,实现信息存储与处理融合的新型计算机体系架构,研究者将关注点投向神经形态计算领 域[1-2].使用新兴的非易失性阻变器件(或忆阻器)模拟生物突触功能已成为通向神经形态计算的关键技术[3].但大多数忆阻器由特殊材料和定制工艺制造,缺乏统一的制备工艺流程,且与目前的主流CMOS工艺不兼容,这使得基于忆阻器的商业产品缺乏CMOS集成[4].另外,现有忆阻器的商业化也受到诸如工艺一致性和泄漏电流路径等可靠性问题的限 制[4-6].因此,急需寻找一种可商业化的神经形态替代方案.

浮栅MOS器件具有和类似忆阻器件的非易失性,故在神经形态计算领域受到广泛关注[7-11]. 1992年,基于浮栅的MOS神经元被首次提出,并实现了加权求和等简单的生物神经元操作[8].此后,浮栅器件以多种方式应用于神经形态计算,实现了诸如LTP/LTD、STDP等复杂的突触学习规则[7,9].此外,具有忆阻工作模式的浮栅突触器件也被提出,作为神经形态系统中替代两端忆阻器件的潜在方案[10-11].然而,这些神经形态应用均采用双多晶硅工艺,与标准CMOS工艺相比,存在制造周期长、良率低和成本高等问题[12].

人类70%以上的信息源于视觉,光信号在生物感知系统中起着至关重要的作用[13],故研究光感应的人工突触在类脑神经形态系统具有重要意义,是迈向神经形态视觉和人工智能的关键一步,但目前受光激励响应的浮栅突触器件研究甚少.

针对上述问题,本文提出了一种可在商业化的CMOS工艺平台上制造的浮栅突触器件,同时引入光信号,实现突触的光响应.利用浮栅电压表征突触权重,在光刺激和电刺激的作用下,实现突触连接强度的增强和抑制.基于提出的光电浮栅突触,设计了对应的像素识别单元和阵列,完成了二值图像“+”的识别.

1 光电浮栅突触设计

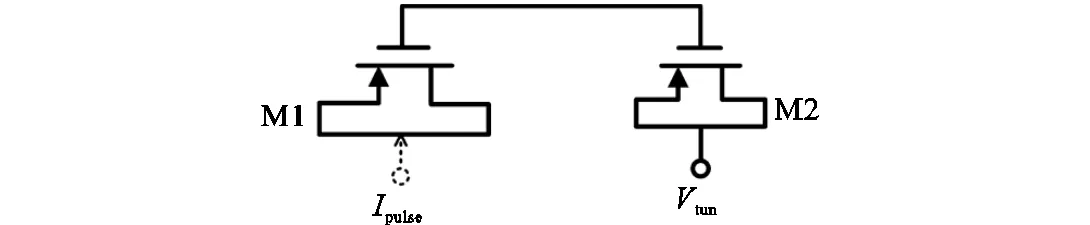

图1给出了基于TSMC 180nm标准CMOS工艺构建的浮栅型光电突触.该突触由两个PMOS晶体管构成,其中一个为光电混合模式的光感应晶体管,另一个为电操控的隧穿晶体管,二者的栅极相连并与其余部分隔离,形成浮栅.因浮栅可长期存储电荷,故采用浮栅电势作为突触权重.光感应管M1由光电二极管与PMOS管组合构成,其中光电二极管利用N阱与P型衬底形成的纵向PN结实现;PMOS晶体管的源和漏短接,用做MOS电容器.为避免入射光信号的干扰,除M1的N 阱上方区域外,其余部分皆用遮光金属覆盖.在光脉冲的照射下,光电二极管产生的脉冲电流对MOS电容充电,所以M1的栅极电势随光脉冲改变.隧穿晶体管M2的源、漏和阱短接,且外接隧穿电压tun,利用FN隧穿效应对浮栅进行电子注入和擦除,实现突触权重的双向修正.根据电容分压原理,M1的电容M1应大于M2的电容M2,以使tun的大部分压降落在M2的两端,利于电子隧穿.文献[12]中指出M1∶M2>3∶1时,FN隧穿显著.由于M1和M2主要取决于MOS管的栅电容,设计不同的栅面积即可确定二者的电容比.取M1和M2的宽/长分别为6μm/6μm和2μm/2μm,则二者的电容比值约为9∶1,满足设计要求.综上所述,由M1积累电荷和M2隧穿电荷共同决定的浮栅电势fg[7, 9]为

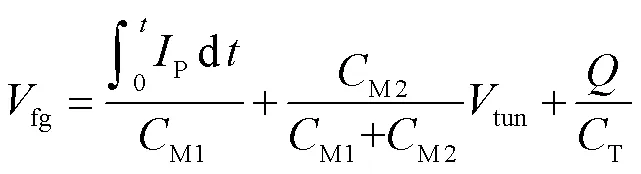

式中:IP为光响应电流;为浮栅总电容;Q为隧穿效应导致的浮栅电荷改变量.

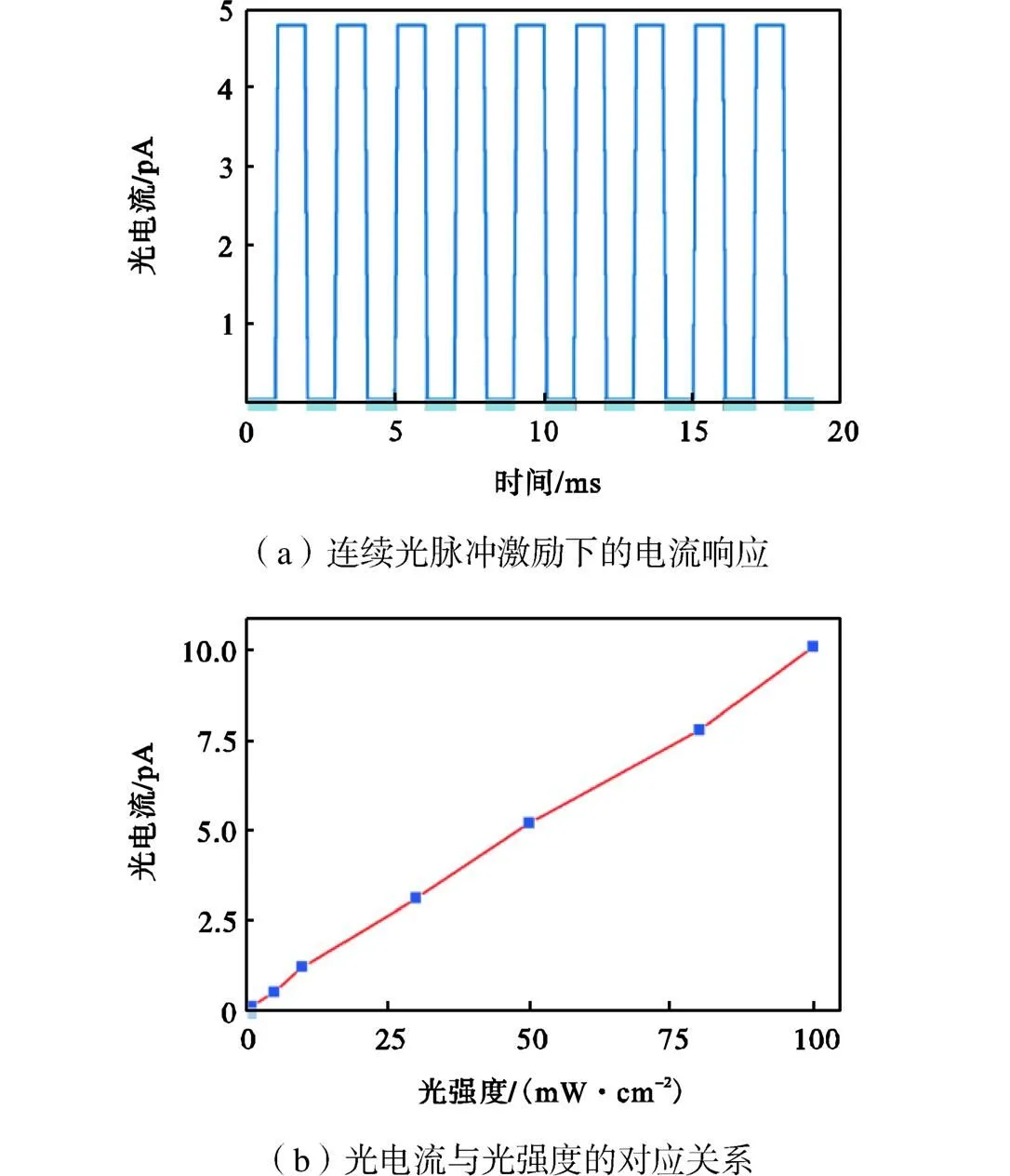

为了建立光脉冲和电流响应间的关系,利用器件仿真软件对光感应晶体管建模,所用工艺参数如表1所示.当施加光波长为900nm、光强度为35mW/cm2、宽度为1ms的光脉冲时,光感应管的响应电流如图2(a)所示.在毫秒光脉冲信号的激励下,光电流随时间保持良好的脉冲响应.图2(b)所示为不同光强脉冲所对应的电流响应.由图可见,光电流幅度随光强近似线性增长.这对调节突触权重非常关键.

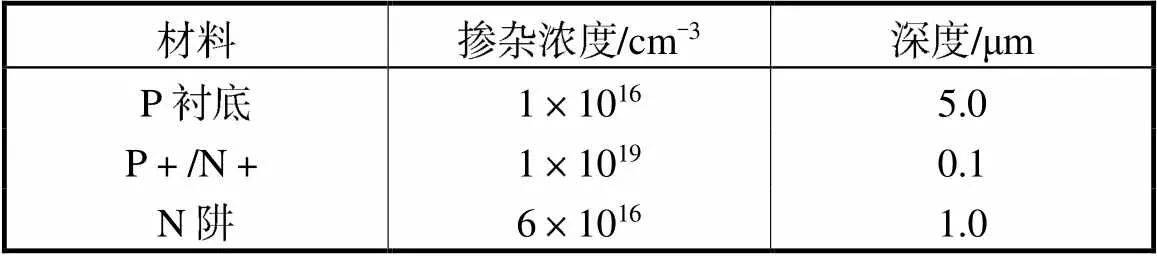

表1 TSMC180nm CMOS 技术的工艺参数

Tab.1 Process parameters of the TSMC 180nm CMOS technology

图2 光电流随时间和光强度的变化

2 突触权重的调节

虽然通过器件仿真可获得光脉冲信号和电流响应的关系,但无法直接测量脉冲电流对浮栅电压,即突触权重的影响.为此,在Cadence环境中搭建了如图3所示的光电浮栅突触的电路结构,研究突触权重的变化机制.在仿真过程中,使用等效的电流脉冲替代施加于M1的光脉冲信号.

图3 光电突触的电路结构

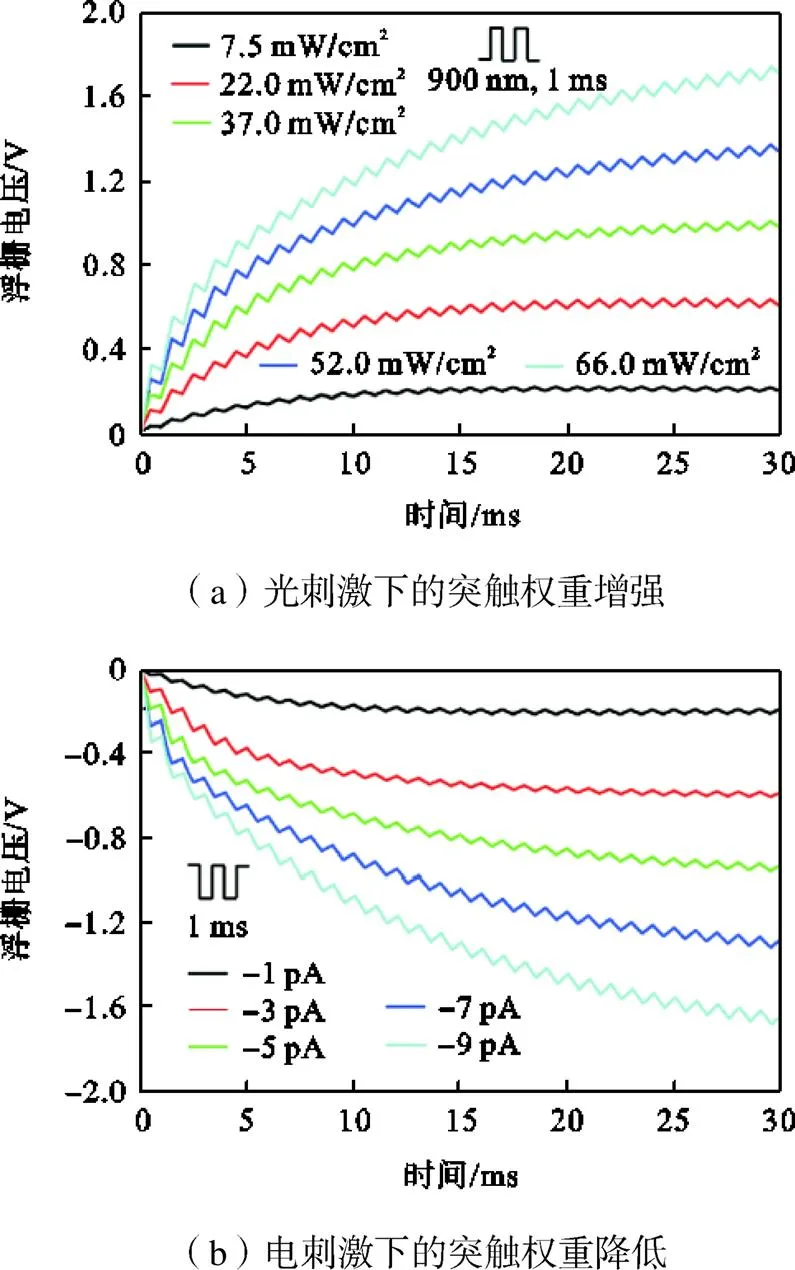

在生物突触中,突触后膜上的受体接收突触前膜释放的神经递质,使突触权重增大或减少,这是突触的兴奋性和抑制性.连续的兴奋或抑制刺激可进一步促成突触可塑性.光电浮栅突触在光刺激和电刺激的组合作用下,可模拟突触行为并实现光增强和电抑制.图4分别展示了光脉冲(即正电流脉冲)和负电流脉冲对浮栅电压的调制结果.浮栅对脉冲信号有“积分”特性,其中光脉冲使浮栅电压增大,即突触权重增加,可看作兴奋性脉冲;负电流脉冲使浮栅电压减小,即突触权重减小,可看作抑制性脉冲.浮栅电压在连续刺激下增强或降低,并最终趋于稳定,这与生物突触在连续刺激下的饱和现象是一致的.

图4 Vtun=1.0V时,突触的光增强和电抑制

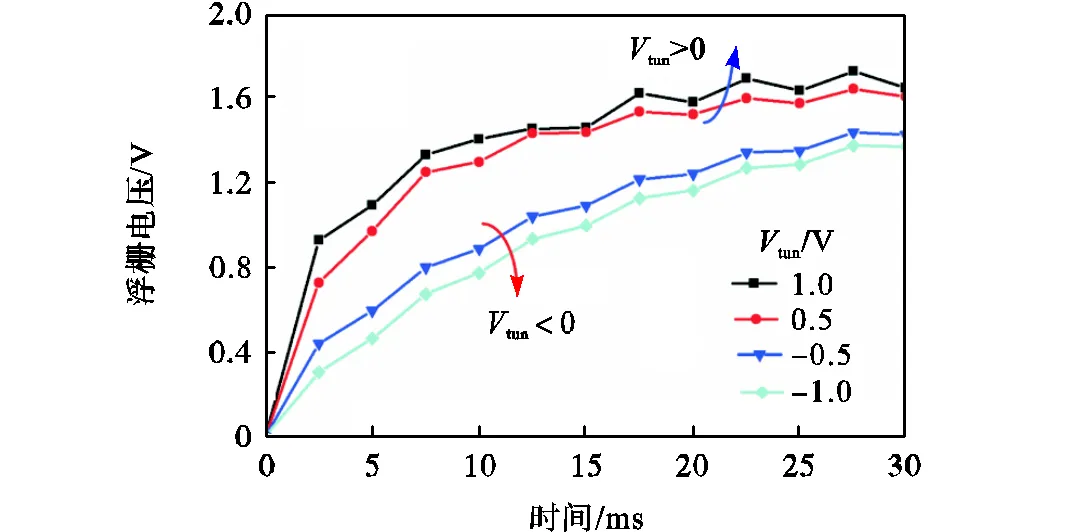

图5所示为FN隧穿对浮栅电势的影响.当施加正向隧穿电压时,M2管形成由阱指向栅极的强电场,电子从浮栅隧穿到阱,等效于浮栅积累正电荷,电势升高;反之,电子从阱隧穿到浮栅,电势降低.在隧穿过程中,M2管两端的电压差逐渐减小,故隧穿效应也趋于缓和,如图5中浮栅电压的变化所示.这可以作为突触权重的一种修正方案,例如突触权重被无关变量影响且增强时,可以施加负偏压来抵消这一误差,反之亦可.

图5 隧穿效应对突触权重的影响

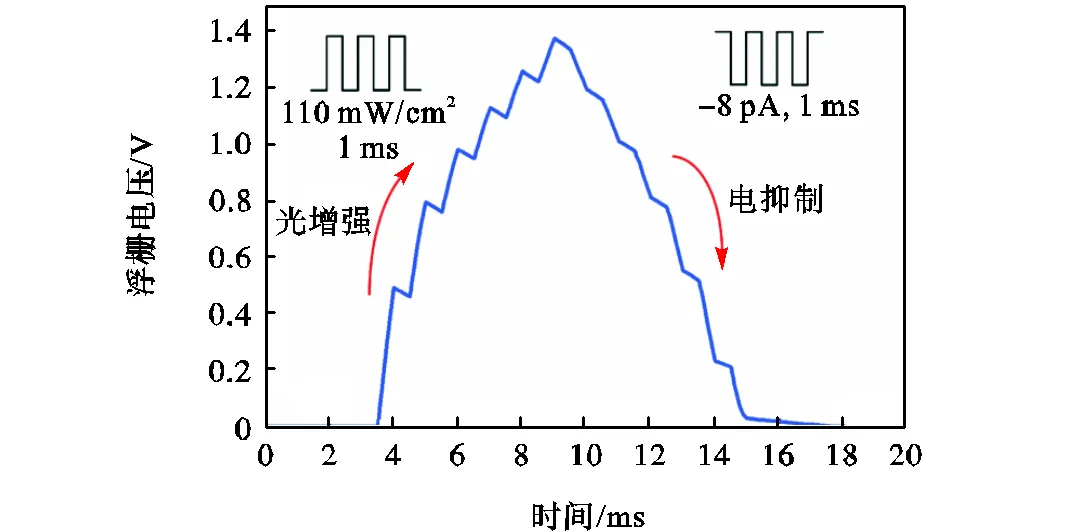

生物突触在接收刺激后,突触权重会逐渐恢复到初始状态.光电浮栅突触的复位则通过光信号和电信号的交替刺激实现.图6给出了光电浮栅突触权重在连续刺激下的复位操作.当施加光脉冲刺激时,浮栅电压升高,随后在负电流脉冲的刺激下,浮栅电压降低,回到初始状态.通过此特性可擦除浮栅中存储的信息,使突触权重复位.

图6 突触权重的复位操作

3 图像识别

光电突触作为神经形态视觉感知的基本单元,在图像识别和模式分类等领域具有广阔的应用前景.本节基于前面提出的光电突触,设计用于图像识别的视觉传感阵列.

将图7(a)所示的3Í3像素的二值图像“+”作为识别目标,其中各像素定义为P(和分别表示行和列).图像的每个像素由光电浮栅突触与比较器构成的阈值电路识别,如图7(b)所示.其中,比较器由M3~M8晶体管构成,电压th是与浮栅电压比较的“阈值”,设定为1.2V;电压bias控制比较器的偏置电流,设定为1.6V.光电突触的浮栅电压驱动比较器,输出代表逻辑“1”和“0”的高低电平.图像识别的具体过程如下.

图7 二值图像及像素识别单元

首先,光脉冲照射对应的光电突触将光信号转换为电压并存储到浮栅;然后浮栅电压驱动比较器,并与阈值电压比较.若光脉冲感应的浮栅电压大于th,则比较器的输出out升至接近dd的高电平,即输出逻辑“1”,代表白像素的识别成功;若浮栅电压低于th,则out保持低电平,即输出逻辑“0”,代表黑像素识别成功.本文采用不同强度的光脉冲定义黑/白像素.

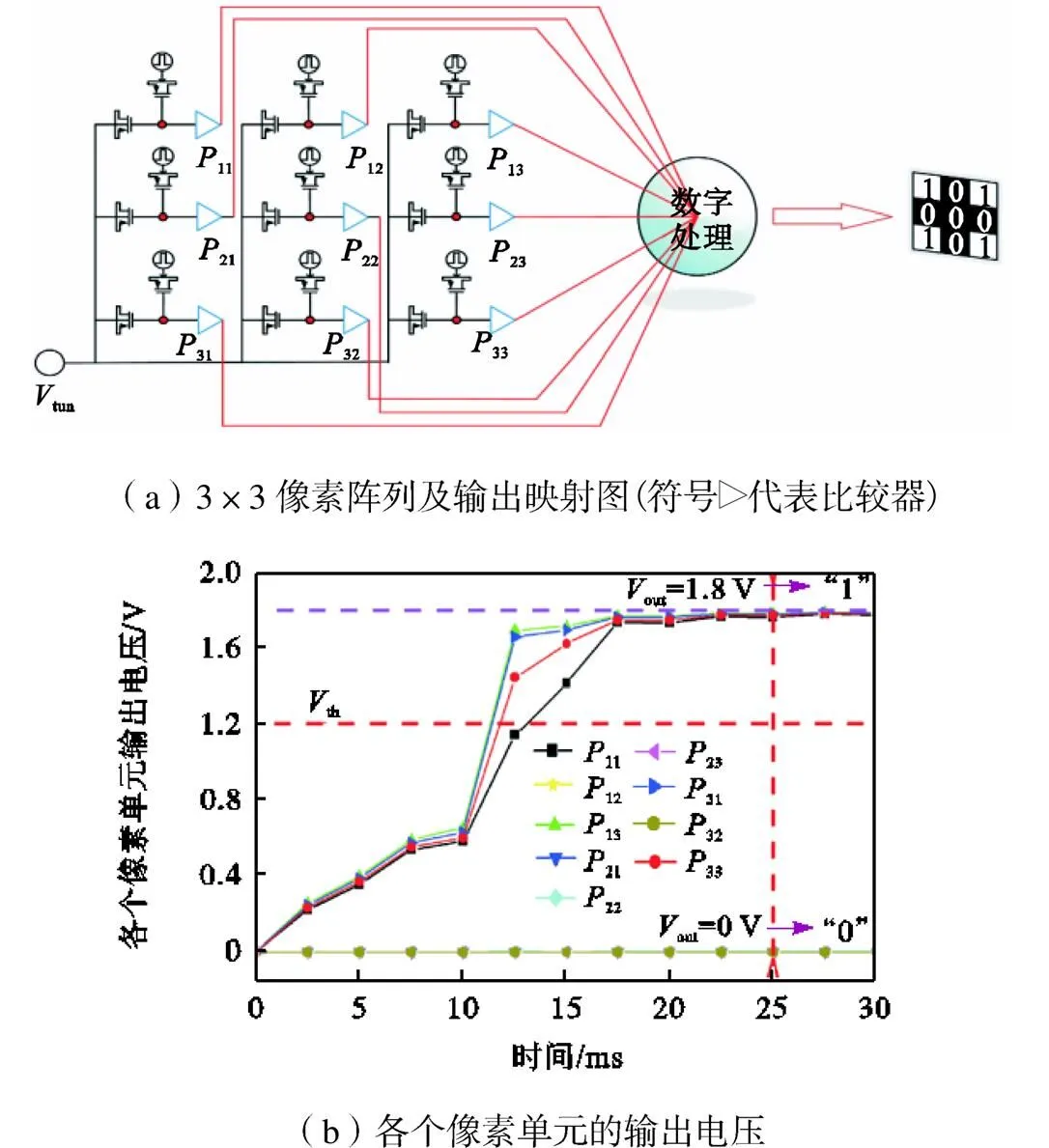

为识别二值图像“+”,搭建了如图8(a)所示的3×3像素阵列,其与图像像素规模相同.在Cadence中实现整体电路设计,并令各像素单元中M2管的隧穿电压均为0.5V,M1管输入与光强对应的电流脉冲. 在无噪声情况下,黑白像素的光强分别设定为0和75mW/cm2.在完成各像素判决后,使用Matlab合成所有像素的输出,结果如图8(a)右侧图像所示,所设计像素阵列可成功识别二值图像“+”.为了模拟真实应用场景,本文也分析了像素阵列存在噪声的情况.其中,定义黑像素12的基础光强为0mW/cm2,像素21、22、23和32在基础光强上依次增加0.5mW/cm2;定义白像素11的基础光强度为75mW/cm2,像素13、31和33也在基础光强上依次增加0.5mW/cm2.将器件仿真软件得到的不同光强对应的电流脉冲输入像素阵列电路,即可获得各像素的仿真结果,如图8(b)所示.由图8可见,与黑像素对应的识别单元输出近似为0V的低电平,而与白色像素对应的识别单元输出接近dd的高电平,光噪声并未对图像识别造成影响.这说明本文设计的基于光电突触的像素阵列可实现图像识别,并具有良好的抗噪声性能.

图8 图像识别阵列及结果

4 结 语

基于TSMC 180nm CMOS工艺,设计了一种光电浮栅突触.器件使用光敏二极管感应光信号,利用浮栅电荷调节突触权重,实现了突触的光增强、电抑制和复位功能.在此基础上,搭建了3×3的视觉传感阵列,在无噪和有噪两种情况下,均成功实现了二值图像“+”识别.与传统双多晶硅CMOS工艺的浮栅突触相比,本文提出的光电突触具有成本低、可靠性高和抗干扰等优点,有望在图像识别领域获得广泛应用.

[1] Yu Z,Abdulghani A M,Zahid A,et al. An overview of neuromorphic computing for artificial intelligence enabled hardware-based hopfield neural network[J]. IEEE Access,2020,8:67085-67099.

[2] Katumba A,Freiberger M,Laporte F,et al. Neuromorphic computing based on silicon photonics and reservoir computing[J]. IEEE Journal of Selected Topics in Quantum Electronics,2018,24(6):1-10.

[3] Mohan C,Camuñas-Mesa L A,Vianello E,et al. Neuromorphic low-power inference on memristive crossbars with on-chip offset calibration[J]. IEEE Access,2021,9:38043-38061.

[4] Danial L,Pikhay E,Herbelin E,et al. Two-terminal floating-gate transistors with a low-power memristive op-eration mode for analogue neuromorphic computing[J]. Nature Electronics,2019,2:596-605.

[5] Adam G C,Khiat A,Prodromakis T. Challenges hindering memristive neuromorphic hardware from going mainstream[J]. Nature Communications,2018,9(1):5267.

[6] Rajendran B,Alibart F. Neuromorphic computing based on emerging memory technologies[J]. IEEE Journal on Emerging and Selected Topics in Circuits and Systems,2016,6(2):198-211.

[7] Pankaala M,Laiho M,Hasler P. Compact floating-gate learning array with STDP[C]//2009 International Joint Conference on Neural Networks. Atlanta,USA,2009:2409-2415.

[8] Shibata T,Ohmi T. A functional MOS transistor featuring gate-level weighted sum and threshold operations[J]. IEEE Transactions on Electron Devices,1992,39(6):1444-1455.

[9] Ramakrishnan S,Hasler P,Gordon C. Floating gate synapses with spike-time-dependent plasticity[J]. IEEE Transactions on Biomedical Circuits and Systems,2011,5(3):244-252.

[10] Ziegler M,Kohlstedt H. Mimic synaptic behavior with a single floating gate transistor:A memFlash synapse[J]. Journal of Applied Physics,2013,114(19):194506.

[11] Ziegler M,Gunther R,Kohlstedt H. Complementary floating gate transistors with memristive operation mode[J]. IEEE Electron Device Letters,2016,37(2):186-189.

[12] Ohsaki K,Asamoto N,Takagaki S. A single poly EEPROM cell structure for use in standard CMOS processes[J]. IEEE Journal of Solid-State Circuits,1994,29(3):311-316.

[13] Wang G,Wang R,Kong W,et al. Simulation of retinal ganglion cell response using fast independent component analysis[J]. Cognitive Neurodynamics,2018,12:615-624.

Photoelectric Floating-Gate Synapse Based on Standard CMOS Process

Xie Sheng1, 2,Gao Xubin1,Mao Luhong3

(1.School of Microelectronics,Tianjin University,Tianjin 300072,China;2. Tianjin Key Laboratory of Imaging and Sensing Microelectronic Technology,Tianjin 300072,China;3. School of Electrical and Information Engineering,Tianjin University,Tianjin 300072,China)

As a building block of the neuromorphic visual-perception system,both photosensitive and synaptic behavior are required for a photoelectric synapse. This paper proposes a photoelectric floating-gate synapse structure comprising two PMOS transistors based on the TSMC 180nm standard CMOS process using the floating-gate voltage to characterize the synaptic weight. The floating-gate voltage of one PMOS transistor,which operates in an opto-electric hybrid mode,increases and decreases under the stimulation of photonic and electrical signals,thus imitating the excitatory and inhibitory functions of synapses. The other one works in a tunneling mode,and the synaptic weight is modified through the Fowler-Nordheim(FN)tunneling. Based on the circuit model of the proposed photoelectric floating-gate synapse,the circuits for pixel recognition and array were designed,and the recognition processes of binary image“+”were analyzed without/with noise. Simulation results showed that the designed photoelectric synapse of this paper could realize a binary image in a noise-free situation with basic light intensities of 0mW/cm2and 75mW/cm2in a noisy situation with the introduction of a 0.5mW/cm2noise. This demonstrates that the proposed photoelectric floating-gate synapse in this paper has a certain antinoise ability.

neuromorphic computing;CMOS;photoelectric synapse;floating-gate;synapse weight

10.11784/tdxbz202106029

TN60

A

0493-2137(2022)07-0701-05

2021-06-21;

2021-08-20.

谢 生(1978— ),男,博士,副教授,xie_sheng06@tju.edu.cn.Email:m_bigm@tju.edu.cn

高旭斌,gao_xubin1995@163.com.

国家自然科学基金资助项目(61774113).

the National Natural Science Foundation of China(No. 61774113).

(责任编辑:孙立华)