无线通信系统数字接口模块的设计

2022-05-05汪鹏志

李 欣,张 渊,汪鹏志

(1.中国人民解放军92728部队,上海 200436;2.武汉船舶通信研究所,湖北 武汉 430079)

0 引言

本文设计的无线通信系统数字接口模块主要应用于高速数据传输系统,使用超短波为传输手段,采用时分复用方式完成主站和从站之间的数据传输,设计了一种同步机制,完成从站和主站之间的时隙同步。

1 概述

主站高速数据传输系统的主芯片使用Xilinx公司的v6系列芯片,从站系统主芯片使用Altera公司的stratix_IV系列芯片,由于硬件不同,接口也不同。主站高速数据传输系统的数字接口有CPU接口、光纤接口、时隙中断接口。从站的数字接口有网口接口、AD/DA芯片初始化、时隙同步接口,实现数字上下频变换。

2 主站高速数据传输系统设计

主站高速数据传输系统的各个硬件模块之间通过高速串行接口rapid_io进行通信,FPGA采用是Xilinx公司的V6系列,其FPGA框图如图1所示。

图1 主站高速数据传输系统FPGA框架图

srio_dataport为主模块,完成了CPU数据到调制/解调模块之间数据包格式的转换,并且将数字基带信号通过光纤传送给外接的中频板,接收光纤传来的基带数据,提取出适合解调的基带数据。

2.1 CPU接口设计

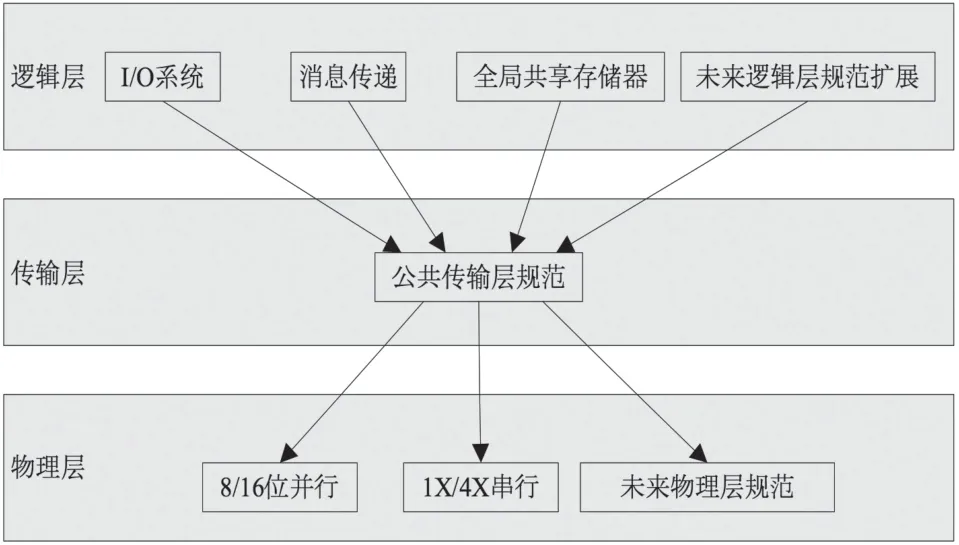

CPU接口采用高速SRIO接口。SRIO协议[1]设计了三层的分层结构,分别是逻辑层(Logical Layer)、传输层(Transport Layer)以及物理层(Physical Layer),如图2所示。

图2 SRIO协议规范分层

(1)逻辑层:制定了逻辑层协议,规定了包格式以及端点设备所完成事务的信息,这些是终端处理所必需的,包括传输类型ttype、包长度size、目的地址(Destination Addr)等。当前,逻辑层支持全局共享存储器、存储器映射的输入输出、消息传递以及流式数据4种不同的传输机制,并且保留了逻辑层功能的扩展功能。

(2)传输层:定义了包交换的路由和寻址机制。SRIO支持8位小系统(最多256个独立的端点地址)和16位大系统的地址空间(当前已支持32位的ID空间)。ID号为端点设备间的报文传输提供了相应的路由信息,交换器件可通过ID信息查询路由表将数据转发到目的设备。

(3)物理层:说明设备级接口信息,如电气特性、错误管理和流量控制机制。物理层包括8位/16位并行接口标准和1X/4X串行接口标准。

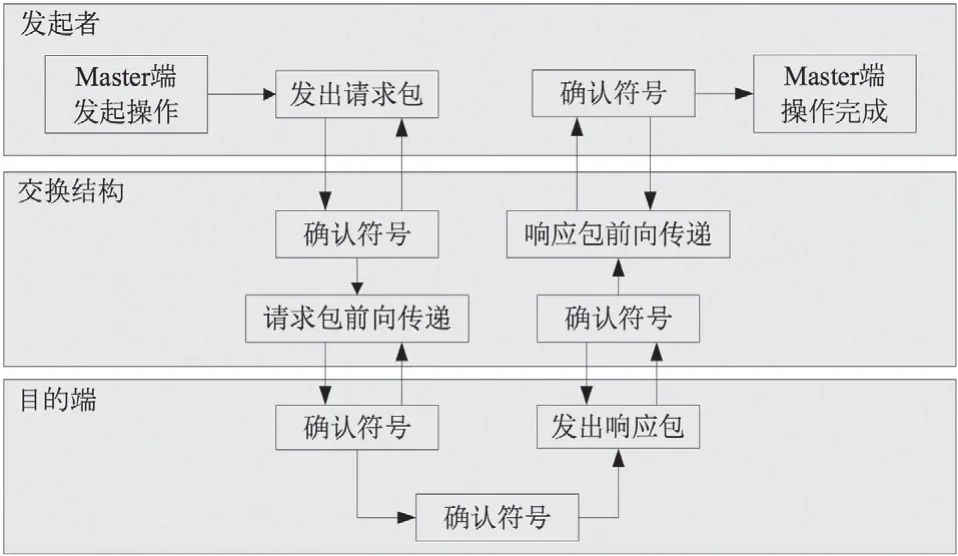

SRIO的核心操作[2-4]包括请求和响应事务两种。包是SRIO系统中端点器件间报文传输的基本单元。事务发起者(Initiator)发起一个请求事务给目的端点,目的端点将ACK发送给发起者来完成一次握手操作。硬件上通常不好将SRIO端点直接互连在一起,而是通过介于其中的一个或多个交换器件的集合链接,SRIO事务传递过程如图3所示。

图3 SRIO事务传递过程

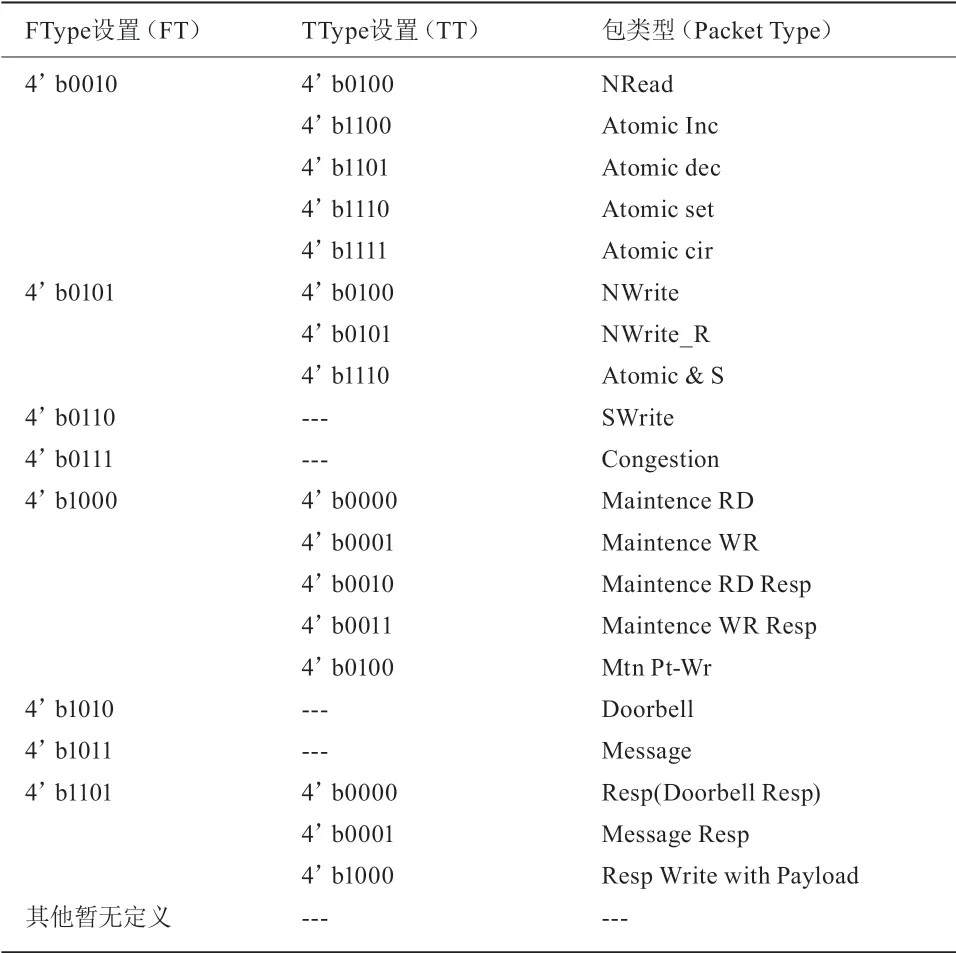

SRIO数据包类型[5-7]由其Ftype(Format Type)和TType(Transaction Type)共同确定,表1描述了由FType、TType共同确定的所有模式及其对应的解码动作。根据包格式的不同,事务类型主要有3种,分别是NRead(基本读操作)、NWrite(基本写操作)以及Doorbell(门铃操作),通过这3种类型的组合就可以完成所有的存储器读写操作。具体的SRIO包类型如表1所示,最常用的包类型是NWrite和Doorbell。

表1 SRIO包类型

鉴于SRIO总线的复杂程度,Xilinx公司没有公开SRIO协议实现的技术细节和源码,而是以一种技术不开源的ngc文件形式存在的。通过例外SRIO ip核,设置速率为2.5 Gbps,并完成初始化。串行数据通过srio_top_2g5核之后转化成64位双口ram端口信号。CPU向FPGA发送数据后会发送一个doorbell信息当FPGA监测到doorbell信息时,则读取CPU发来的数据,并将读取的64位数据转换成8位数据传递给调制解调模块,其中第1~3字节保留,第4字节表示调制模式,第4个字节为0xff则表示发送的是网控帧,同时开启time_counter计数,当sync_flag指示信号拉高时,则停止;若不是0xff则表示调制模式,接下来的数为待编码调制的有效数据,0x0表示二进制,40字节;0x1表示四进制,80字节;0x2表示四进制,160字节;0x3表示二进制,80字节。当收到数据后,并不是马上开启调制/解调模块产生调制波形,而是等待下一个时隙中断到来,同时产生start_tran,保证调制波形开始于时隙中断,调制波形就不会跨时隙。接收时,在有效数据前插入8字节,前4字节填充time_counter的值,第6~7字节保留,第8字节表示收到数据包的调制模式,0x0表示二进制,40字节;0x1表示四进制,80字节;0x2表示四进制,160字节;0x3表示二进制,80字节;将其转化为64位数据写进srio_top_2g5核,并通过igen_0控制帧通知srio_top_2g5读取数据。

驱动接收SRIO NWrite数据包时序示例如图4所示。驱动程序收到NWrite包后,剥离SRIO NWrite帧头等信息,将数据以wr_en,wr_addr和wr_data信号发送给用户,用户可以将wr_en,wr_addr和wr_data至FPGA的RAM,FIFO或者用户应用。RAM和FIFO由用户根据需要自行维护大小和状态,驱动不开用户RAM或FIFO。

2.2 光纤接口设计

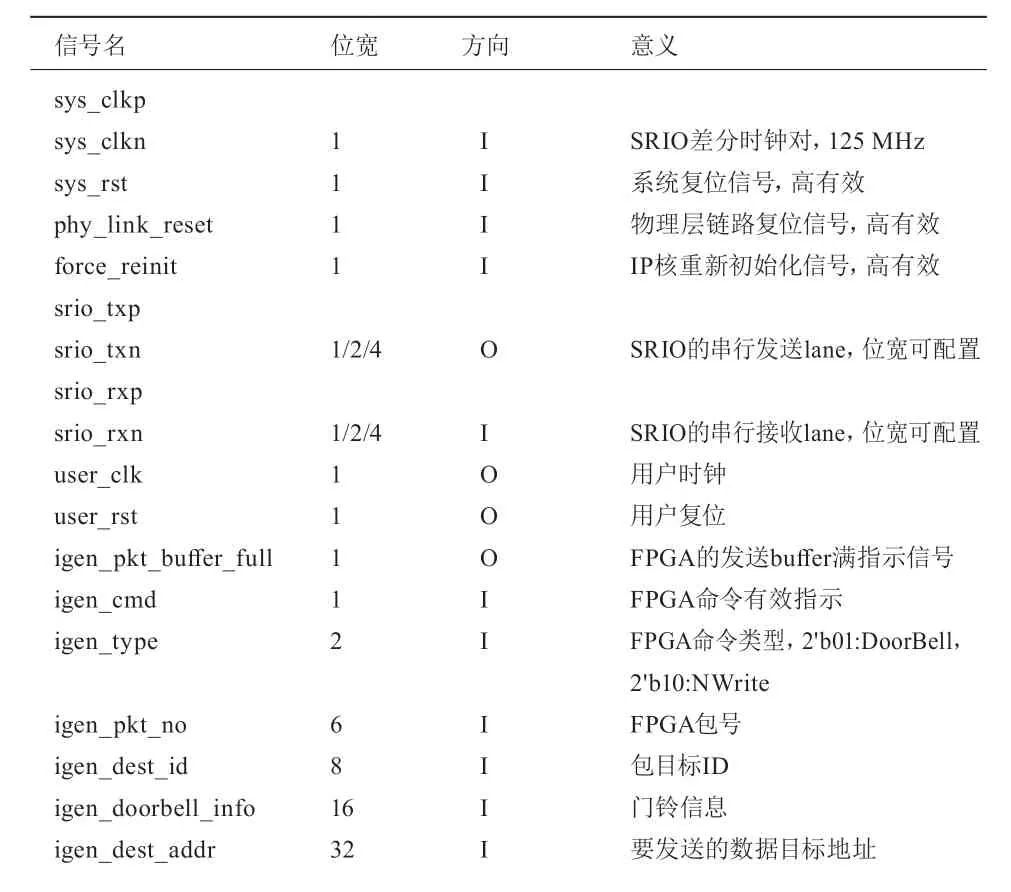

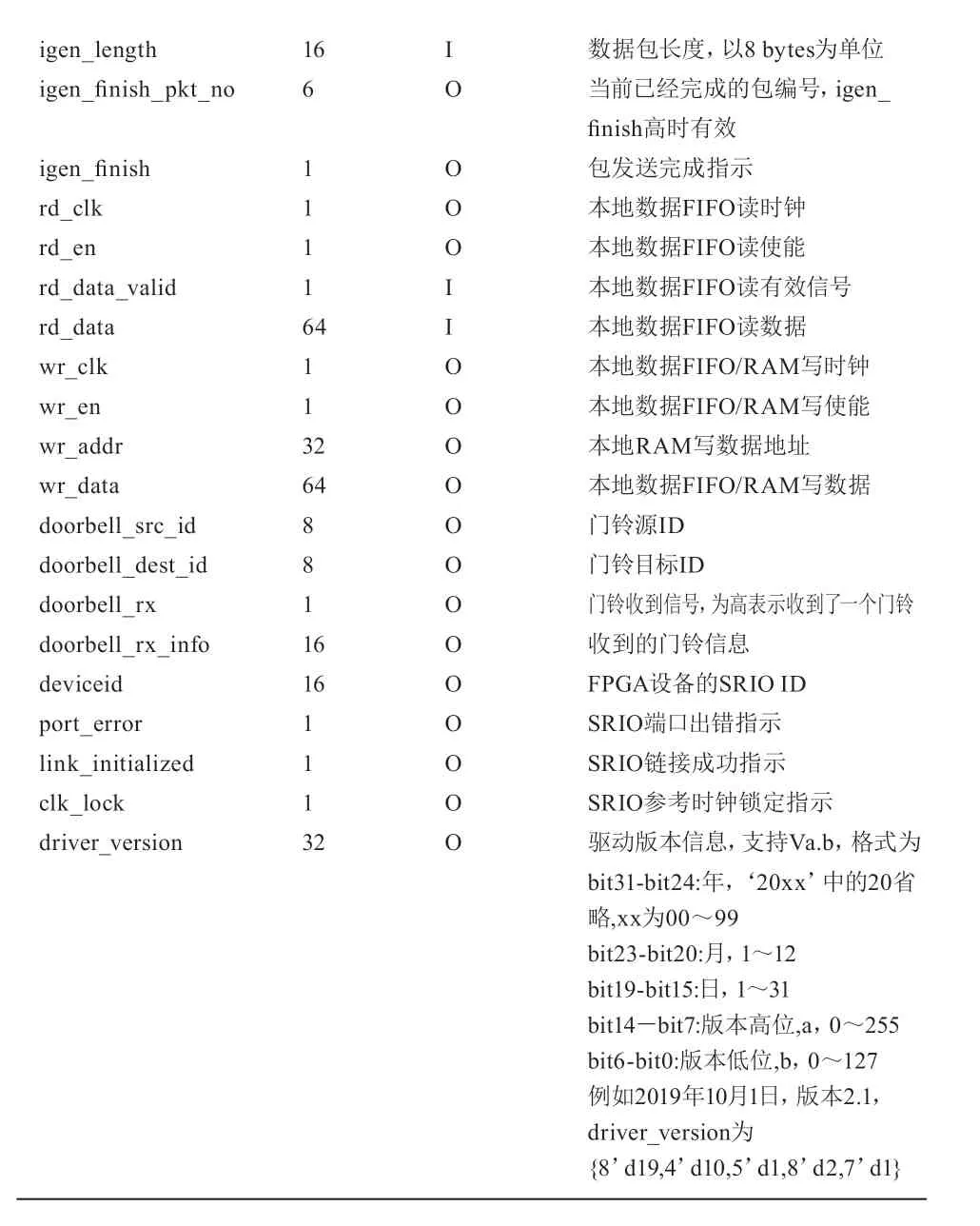

光纤接口是基于SRIO接口的,经过光电转换模块,将待发送/接收的数据转换为光信号发送出去,其FPGA内部核心还是使用SRIO接口。本文使用的光纤SRIO接口速率为1.25 Gbps,例外的ip核名字为srio_top_1g5,其接口信号定义如表2所示。

表2 SRIO驱动接口说明

igen_length 16 I 数据包长度,以8 bytes为单位igen_finish_pkt_no 6 O 当前已经完成的包编号,igen_ finish高时有效igen_finish 1 O 包发送完成指示rd_clk 1 O 本地数据FIFO读时钟rd_en 1 O 本地数据FIFO读使能rd_data_valid 1 I 本地数据FIFO读有效信号rd_data 64 I 本地数据FIFO读数据wr_clk 1 O 本地数据FIFO/RAM写时钟wr_en 1 O 本地数据FIFO/RAM写使能wr_addr 32 O 本地RAM写数据地址wr_data 64 O 本地数据FIFO/RAM写数据doorbell_src_id 8 O 门铃源ID doorbell_dest_id 8 O 门铃目标ID doorbell_rx 1 O 门铃收到信号,为高表示收到了一个门铃doorbell_rx_info 16 O 收到的门铃信息deviceid 16 O FPGA设备的SRIO ID port_error 1 O SRIO端口出错指示link_initialized 1 O SRIO链接成功指示clk_lock 1 O SRIO参考时钟锁定指示driver_version 32 O 驱动版本信息,支持Va.b,格式为 bit31-bit24:年,‘20xx’中的20省 略,xx为00~99 bit23-bit20:月,1~12 bit19-bit15:日,1~31 bit14-bit7:版本高位,a,0~255 bit6-bit0:版本低位,b,0~127 例如2019年10月1日,版本2.1, driver_version为 {8’d19,4’d10,5’d1,8’d2,7’d1}

调制/解调模块的基带I/Q两路信号通过光纤和外面的中频板交互数据。当发送时,采用了乒乓存储技术,将调制后的基带I/Q两路信号写进双口ram中,时钟频率为16 MHz,当写满128字节时,发送igen_1控制帧,通知srio_top_1g5读取数据,并告诉srio_top_1g5读取数据的首地址,在srio_top_1g5读取数据的时候,由于数据是连续来的,为保证数据不丢失,写到另一块双口ram中。这样通过写A,读B,写B,读A实现了存储器的乒乓读写操作,保证连续数据不丢失地发送出去。收的时候,将srio_top_1g5发送来的64位数据写进fifo中,同时不停地读fifo数据,只要速率匹配,就能输出有效的基带I/Q两路信号,供解调模块捕捉同步头并解调出有效数据。当fifo为空时,对于解调模块而言,基带I/Q为噪声信号,不会影响其他模块的正常工作。

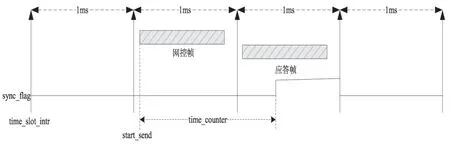

2.3 时隙中断接口设计

主站采用的定时计数器1 ms产生一个时隙脉冲,能精确到50 ns,其产生的时隙中断脉冲如图4所示。主从站之间的时隙调整采用RTT方式。主站在网控帧时隙的固定时刻发送一个网控帧,下个时隙接收从站发来的应答帧,并记下主站波形开始时刻到收到应答帧的同步sync_flag后的时间,伴随着应答帧将该时间传送给CPU。当传输距离为0时,该时间time_counter为固定的,在实验室下,通过示波器测出该固定时间。当传输距离变化时,该时间也会变化,从而主从站时隙中断也会产生偏差。CPU每收到一包应答帧,就从中提取出这个时间,若大于实验室量出的值,则在下一个网控帧插入命令,通知从站将时隙中断向左移;若小于实验室量出的值,则在下一个网控帧中插入命令,通知从站将时隙中断向右移动,移动的数量为两个值偏差的一半。该时间是按一定速度慢慢变化的,这种时隙调整方式能完成时隙调整功能。

图4 主站时隙中断脉冲

3 从站高速数据传输系统设计

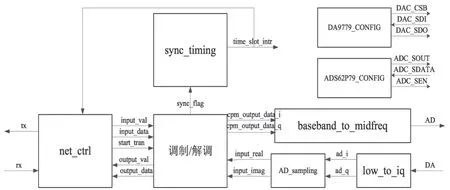

从站高速数据传输系统的硬件平台采用FPGA+PowerPC+AD+DA构建,采用的是Altera公司的Stratix_iv系列的FPGA。PowerPC和FPGA之间的接口为百兆网口,与射频模块之间的接口传送模拟信号。其框图如图5所示。

图5 从站高速数据传输系统接口框架图

3.1 net_ctrl模块设计

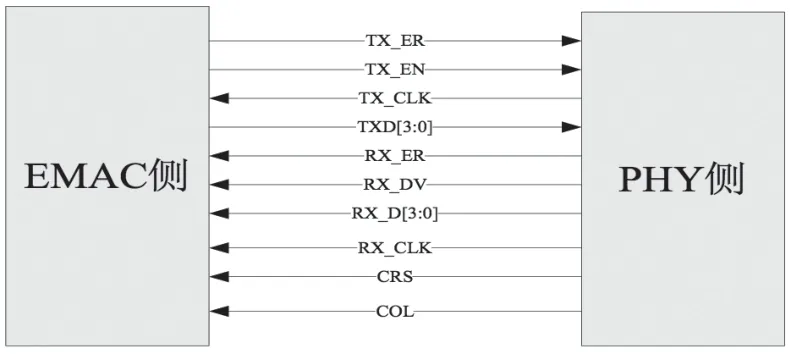

百兆网口直接调用FPGA自带的三速以太网ip核,FPGA的EMAC控制器与以太网物理芯片是MII接口,如图6所示。通过MDIO将物理芯片配置为百兆模式,通过寄存器接口根据寄存器定义将EMAC ip核配置成百兆模式。

图6 MII接口

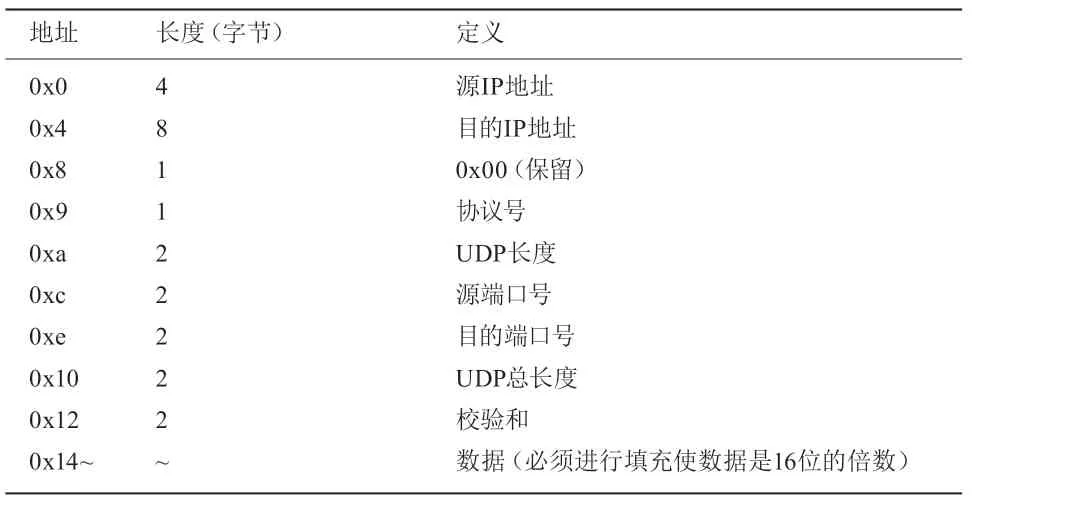

根据约定号的帧格式,如表3所示,接收UDP包,完成IP地址的检测以及帧头校验,去掉UDP包头后,提取出数据。收到数据包的第4字节为0xff,接下来4字节表示CPU配置的time_slot_offset的值。若收到包的第4字节不是0xff,则表示是调制波形模式,接下来的数为待编码调制的有效数据,0x0表示二进制,40字节;0x1表示四进制,80字节;0x2表示四进制,160字节;0x3表示二进制,80字节。当收到网口的数据后,并不是马上将数据调制成波形,而是等待下一个时隙中断到来后,才发送start_tran信号给调制解调模块,使其产生波形,这样保证波形固定从时隙中断开始时刻产生。解调出来的数据采用相同的格式,在有效数据前插入4字节,前个字节保留,第4字节表示收到数据包的调制模式,0x0表示二进制,40字节;0x1表示四进制,80字节;0x2表示四进制,160字节;0x3表示二进制,80字节,打包好后通过百兆以太网发送给CPU。

表3 UDP包数据格式

3.2 数字上下频模块设计

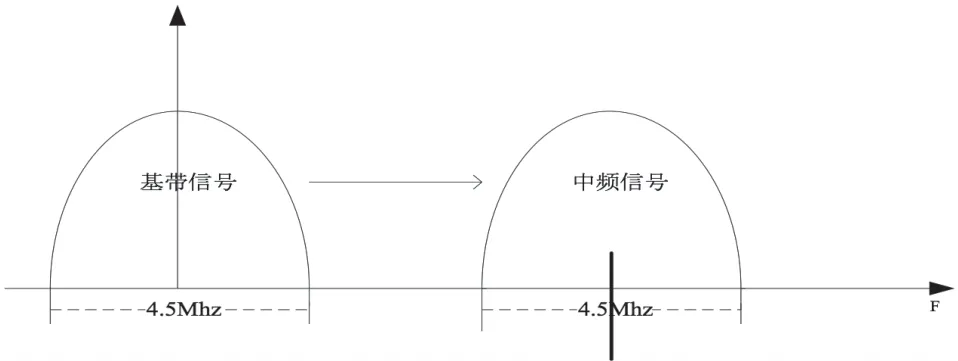

数字上变频即将带宽为4.5 MHz的数字基带信号的变更为中频频率为24.384 MHz的数字中频信号,如图7所示。首先将采样速率为16 Mbps的已调制数字基带数据经过插值滤波变到128 Mbps采样频率下,然后根据公式AD=i×cosIq×sinf,生成中心频率为24.384 MHz的中频调制波形。

图7 数字上变频频谱搬移

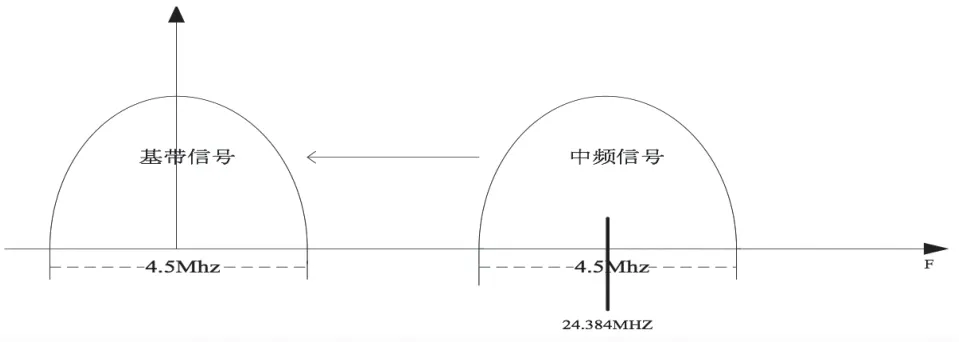

数字下变频即为将采样后的24.384 MHz数字中频信号通过频谱搬移转换为带宽为4.5 MHz的数字基带信号,如图8所示。数字下变频由low_to_iq和AD_sampling两个模块共同完成,FPGA输入的一路AD信号经过low_to_iq模块,生成两路ad_i,ad_q信号,其原理公示是adi=ad×cosf,adq=ad×cosf。AD_sampling模块通过8倍抽取将采样速率从128 Mbps降为16 Mbps。

图8 数字下变频频谱搬移

3.3 时隙同步接口设计

从站产生的时隙中断以主站为基准,保证主从站时隙中断对齐,时隙中断的周期为1 ms。由于波形都是从时隙中断开始的固定时刻开始发送的,从站收到波形后产生sync_flag的时间也是固定的,故sync_flag从拉高到产生时隙中断的时间也是固定的,设为time_slot_offset为调整的初值,这个时间是在实验室条件下通过示波器测出来的。故从站时隙中断由两个条件决定,当从站收不到包时,即无法检测到sync_flag的上升沿,由本身的1ms计数器产生,当从站收到包时,检测到sync_flag的上升沿后启动sync_counter,当sync_counter计到time_slot_offset时产生时隙中断,同时复位sync_counter,这样保证从站跟主站的时隙中断是对齐的。当从站由近到远,由于波形在空中的传输延时,time_slot_offset的值会变小;当从站由远到近,time_slot_offset的值会变大。由2.3节介绍可知,time_slot_offset的变化值是由主站通过RTT校验计算出来的,然后将该帧插入到网控帧中,当从站收到数据包时,根据帧头的类型以及格式,确定网控帧并提取出调整值,更新time_slot_offset的值,这样通过动态调整time_slot_offset的值确保无论从站和主站之间的距离怎么变化,主从设备的时隙中断对准。其时隙中断生成和调整如图9所示。

图9 从站高速数据传输系统的时隙中断

4 AD/DA芯片设计

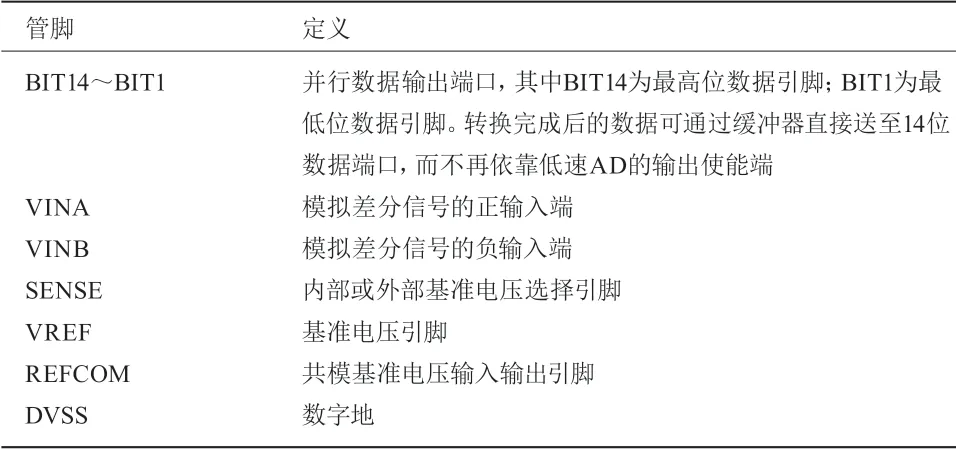

AD芯片采用的是美国公司推出的高速14位并行模数转换集成电路。该芯片自带SHA采样保持电路和OUTPUT BUFFER输出缓冲器。与早期AD芯片相比,AD9240具有极高的采样速率和转换速率,适用于高速模拟信号的采集[8]。AD9240内部结构紧凑,集成度高,工作性能好,所以可以大幅减少印制板的面积,并且降低系统成本。AD9240采用44脚方形封装,其主要引脚的功能如表4所示[9-10]。和传统的低速AD不同的是,AD9240芯片的时序控制完全依靠时钟来控制其采样、转换以及数据输出的操作。在第一个时钟的上升沿开始采样转换,当第三个时钟上升沿来临时,数据将出现在D14~D1端口上。由于AD9240是分级型模数转换,因此,其数据输出时刻比相应的采样开始时刻要晚三个时钟周期。

表4 AD9240引脚说明

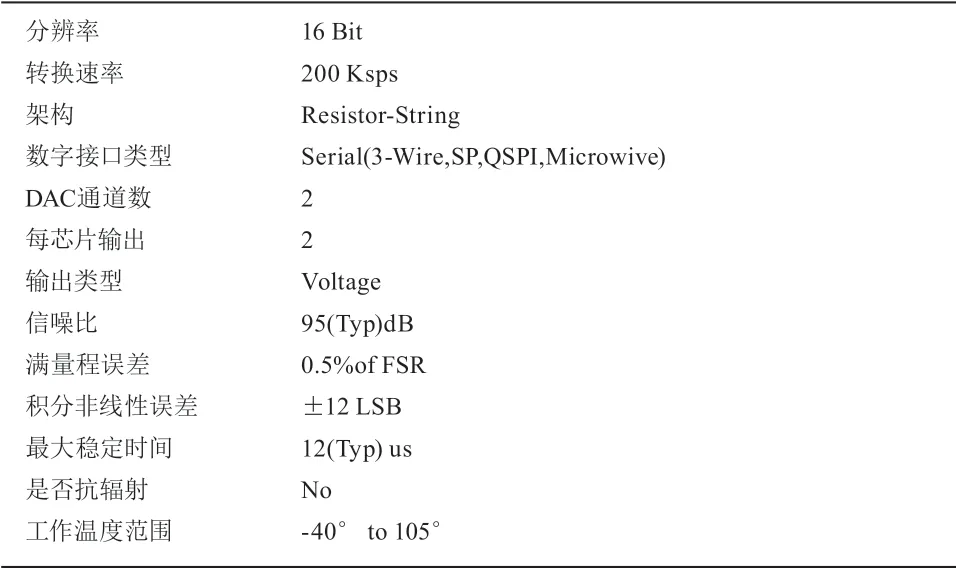

DA芯片使用的是TI原厂推出的DAC8552芯片,该芯片是一款16位双路、超低短时脉冲波形干扰、电压输出数模转换器,其电器特性如表5所示。其使用方法如下:

(1)把SYNC拉低,开始传输信号序列。

(2)数据信号由Din引脚进入,然后写入24 bit移位寄存器,每bit数据在SCLK引脚下降沿的时候写入。SCLK频率最高可达30 MHz。

(3)在SCLK第24个下降沿到来时,最后一位数据被写入移位寄存器,然后移位寄存器自动锁住,此后的SCLK下降沿不在改变移位寄存器内容。

(4)当24位数据全部写入移位寄存器后,高8位作为控制数据,低16位是DA数据DAC8552自动进行DA转换。

(5)再一次SYNC下降沿到来开始下一轮DA转换。转换中若SYNC拉高,则DAC8552复位。

AD和DA芯片通过spi串口进行配置,串行时钟采用低速4 Mbps时钟,通过查询芯片文档,将待配置的寄存器的值和地址制成mif文件,初始化生成的rom存储器核,待系统复位后,自动从rom存储器中读出地址和数据,并将其转化成接口时序,配置AD和DA芯片。若想改变寄存器配置,通过fpga仿真器,操作quartus开发工具自带的In_System_Memory Content完成到寄存器配置值的修改,同时可以通过该工具观察读取AD和DA芯片的状态,看是否正确。

表5 ADC8552电器特性

5 结束语

本文设计了无线通信系统的各个接口以及同步机制,针对不同的硬件平台以及不同的接口,完成对各个接口的驱动,保证数据的高速运转。此外,设计了主从站自同步机制,保证主站和从站高速数据传输系统能快速同步,为TDMA网络协议的正常运行提供了基本保障。