基于FPGA 的AES 快速加解密模块软件设计

2022-04-28魏林,刘刚

魏 林,刘 刚

(中国电子科技集团公司第七研究所,广东广州 510310)

0 引言

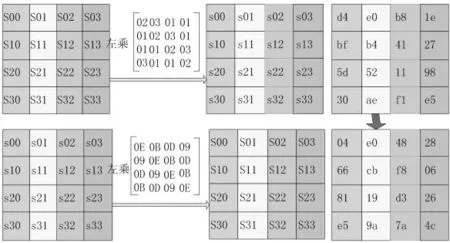

高级加密标准(Advanced Encryption Standard,AES)为最常见的对称加解密算法。对称加解密算法也就是加密和解密使用相同的密钥,具体加解密流程如图1 所示。

图1 AES 加解密算法

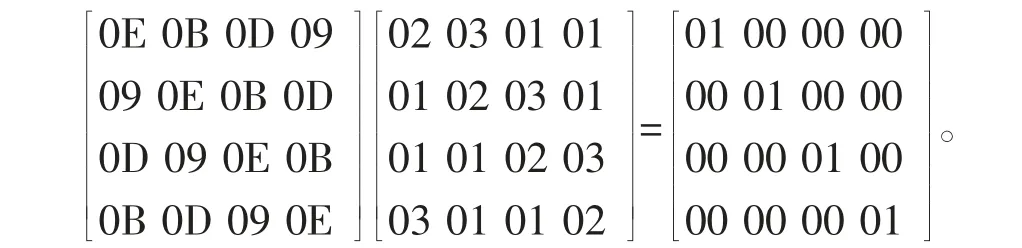

AES 加密过程涉及4 种操作,分别是字节替代、行移位、列混淆和轮密钥加。解密过程分别为对应的逆操作。由于每一步操作都是可逆的,按照相反的顺序进行解密即可恢复明文。加解密中每轮的密钥分别由原始密钥扩展得到。算法中的16 字节明文、密文、轮密钥都以一个4×4 的矩阵表示,我们称其为基本数据单元,如图2 所示。

图2 AES 加解密算法基本数据单元

1 软件架构

AES 加解密软件部件如图3 所示。其主要部件分为AES 加密模块、AES 解密模块、密钥扩展模块三部分。这三部分的实现是通过调用字节替代函数、行移位函数、列混淆函数和论密钥加函数来实现。

图3 AES 加解密软件部件

AES 加解密算法中密钥扩展是将16 字节的原始密钥扩展为11 组16 字节的轮密钥。加密过程中16 字节明文数据经10 轮正变换后输出16 字节密文数据;解密过程中16 轮密文数据经过11 轮反变换后输出16字节明文数据。AES 加解密算法数据处理流程如图4所示。

图4 AES 加解密算法数据处理流程

2 软件详细设计

2.1 字节替换与反替换

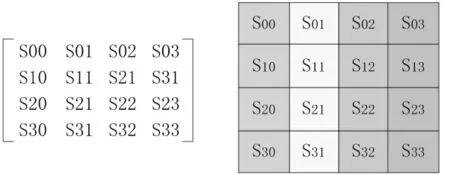

字节替换的主要功能是通过S 盒完成一个字节到另一个字节的映射。其主要实现方法是查找表。字节的bit7-bit4 作为x 值(0 到f 区间),bit3-bit0 作为y 值(0到f 区间),x 列与y 行交叉处即为替换值。字节替换映射表如图5 所示。字节的反替换是字节替换的逆操作,实现方法与字节替换相同。反S 盒替换表如图6 所示。

图5 S 盒替换表

图6 反S 盒替换表

2.2 行位移及其反操作

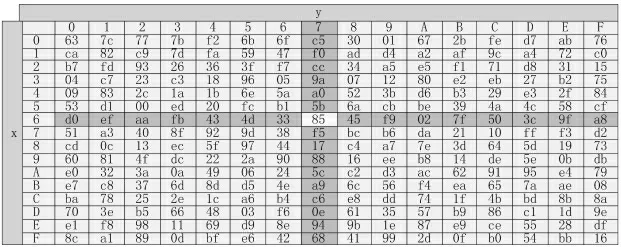

行位移的功能是实现一个4×4 矩阵内部字节之间的移位替换。行位移的操作步骤是:①第一行保持不变。②第二行循环左移1 个字节。③第三行循环左移2 个字节。④第四行循环左移3 个字节。变换过程如图7 所示。

图7 行位移操作及示例

2.3 列混淆及其反操作

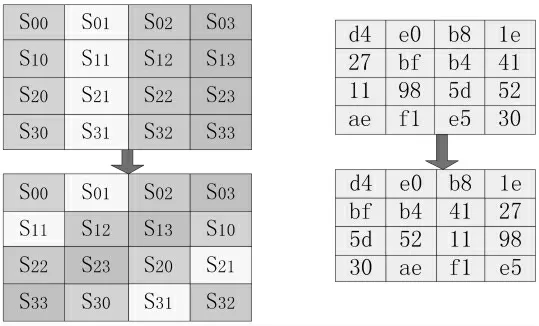

根据矩阵的乘法可知,在列混淆(利用域GF(28)上的算术特性的一个替代)的过程中,每个字节对应的值只与该列的四个值有关系。此处的乘法和加法需要注意以下3 点。

(1)将某个字节所对应的值乘以2,其结果就是将该值的二进制位左移1 位,如果该值的之高位为1,则还需要将移位后的结果异或00011011。

(2)乘法对加法满足分配率,由此可得到乘以3、9、B、D 和E 的结果。

(3)此处的矩阵乘法与一般意义上的矩阵乘法有所不同,各个值在相加时使用的是模2 加法(异或运算)。因为如下。

说明两个矩阵互逆,经过一次逆向列混淆后即可恢复原文。列混淆操作及示例如图8 所示。

图8 列混淆操作及示例

2.4 轮密钥加及其反操作

加密过程中,每轮的输入与轮密钥异或一次(当前分组和扩展密钥的一部分进行按位异或);因为二进制数连续异或一个数的结果是不变的,所以在解密时再异或上一轮的密钥即可恢复输入的数据。

首位使用轮密钥加的理由:若将其他不需要的密钥放在首尾,在不使用密钥的情况下就能完成逆过程,这就降低了算法的安全性。

加密原理:论密钥加本身不难被破解,另外三个阶段分别提供了混淆和非线性功能。但是字节替换、行位移、列混淆阶段并没有涉及密钥,就他们自身而言,并没有提供算法的安全性。如果在上述操作的基础上进行一轮分组的异或加密(轮密钥加),再对该分组进行混淆扩散(其他三阶段),再接着进行下一轮异或加密,如此交替进行,这种方式既有效又安全。

2.5 密钥扩展

密钥扩展过程:将初始密钥以列为主,转换为4 个32bits 的字,分别记做W[0..3];按照如下方式依次求解W[i],其中i 是整数并且属于[4,43]。

(1)将W[i]循环左移一个字节。

(2)分别对每个字节进行S 变换。

(3)变换后与32bits 常量(RC[i/4,0,0,0])进行异或。RC 是一个一维数组,其中RC={01,02,04,08,10,20,40,80,1b,36};轮密钥第1 列求解如图9 所示。

图9 轮密钥第1 列求解

(1)除了轮密钥的第1 列使用上述方法求解,之后的2~4 列使用公式:W[i]=W[i-4]⊕W[i-1]求解,如图10所示。

图10 轮密钥第2~4 列求解

3 软件应用环境

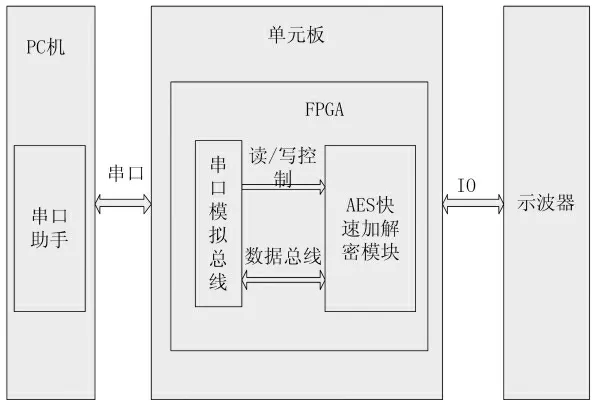

AES 快速加解密软件系统环境图如图11 所示,AES 快速加解密模块软件运行与FPGA 中,可对128bit明密文数据进行加解密操作。软件模块的软件接口为16 位可读写的数据总线及相应的读写控制信号。

图11 AES 快速加解密软件系统环境

该软件用VHDL 语言实现,不依赖特定的FPGA器件,要求SliceLUT 资源>=6000Slice。

4 测试和验证

4.1 仿真验证

验证模块时序及加解密功能的仿真测试环境图如图12 所示,测试使用集成开发环境ISE14.7 及自带的仿真软件ISIM。通过编写testbench 模拟读写控制,验证加解密流程及数据。

图12 仿真验证环境

4.2 单元板验证

单元板验证示意图如图13 所示,测试时用的主用FPGA 芯片为XILINX 的XC6SLX45 芯片。用单元板与PC 机连接,进行加解密功能验证。明文数据包长度128bits×16 包,加密后密文数据可观察数据离散性。

图13 单元板验证

加解密时间、密钥展开用示波器测试测试点。加解密功能用PC 机发送明文数据包经加密模块后,再将密文数据发送至加解密模块进行解密。

测试结果:①实现128bit 明文数据AES128 加密,将128bit 明文数据加密为128bit 密文数据。②实现128bit 密文数据AES128 解密,将128bit 密文数据解密为128bit 明文数据。

在系统时钟频率不小于38.4MHz 的条件下。①密钥扩展时间≤10μs。②加密时间≤5μs。③解密时间≤5μs。