基于C6678的STAP并行处理系统设计

2022-04-27廉志凌

廉志凌

(中国电子科技集团第三十八研究所 合肥 230031)

0 引言

空时自适应信号处理技术(STAP)是1973年由Brennan和Reed提出的,该方法将传统的处理由阵元域推广到了脉冲和阵元二维数据域,性能远优于空时级联处理方法,被认为理论上是最优的。具体工程实现时,根据文献Klemm的研究,要使STAP处理的输出信杂噪比损失小于3dB,用来估计杂波协方差矩阵的独立同分布(IID)训练样本数必须大于处理器维数的两倍。当空域采样数N和时域采样数K较大时,全空时处理很难获得足够的样本,同时空时处理所需的设备量和运算量惊人,从而使得准最优的降维处理成为一种必然选择。

降维处理方法包括固定结构降维处理和自适应降维处理,固定降维处理算法中的比较经典的就是mDT-SAP算法。该算法在时域先对各天线的输出针对不同的多普勒频率用窄带滤波器抑制大量的非同多普勒杂波,剩余同多普勒杂波由后续的空域自适应处理完成,该方法在副瓣杂波区是准最优的。

为了验证mDT-SAP的处理性能,本文搭建了以TI公司C6678处理芯片为主处理器的硬件系统,设计了基于RapidIO通信的核间通信机制,实现了系统的自适应调度和并行处理。

1 硬件平台设计

硬件系统的设计需要综合考虑系统的体积、重量、功耗、处理能力,以及系统可扩展能力。综合以上因素,本系统的设备量包括:一块接口板,一块交换板,以及若干信号处理板。信号处理板的板卡数量可根据实际需求调整,信号处理系统架构图如图1所示。

图1 信号处理系统架构图

接口板的主要作用是将接收到的光信号转换为电信号,然后在FPGA内完成DBF并将合成结果发给信号处理板的第一片C6678。

交换板布有1848芯片,板卡之间大容量的数据交换均需要通过该板卡完成。

每块信号处理板板载4片C6678处理芯片,用来完成所有的信号处理算法实现,主要特性如下:

1) 单片C6678可外挂8GB的DDR3,工作频率为800MHz;

2) 每片C6678通过RapidIO Switch和PCIe Switch分别实现与背板的RapidIO及PCIe的总线互联,构成数据传输通路;

3) FPGA实现背板的RocketIO,Link,板内PCIe以及RapidIO总线的接口转换;

4) 系统可通过CPLD监控单板状态,实现单板配置,复位等。

信号处理板采用的C6678处理器内部包含8个运算核,最高频率可达到1.25GHz。在主频1GHz情况下,其标称的定点运算能力达到256GMACs,浮点运算能力达到128Gflops。每个C6678核内置32KB L1程序Cache,32K L1数据Cache以及512K L2Cache,8个4096KB SRAM。

2 算法原理

2.1 全空时自适应滤波的原理

简单起见,设雷达天线为水平排列的一维线阵,单元个数为,一个相干处理间隔内的脉冲个数为。则第个阵元第次快拍的数据为(,),第个脉冲的阵列数据矢量X()为

()=[(1,),(2,),…,(,)]

(1)

将(),=1,2,…,排成×1的列矢量,即

(2)

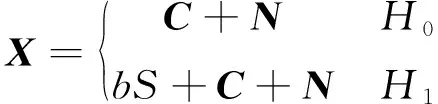

假设表示无目标信号,只有杂波和噪声,表示既有信号,又有杂波和噪声,则有表达式

(3)

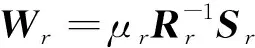

其中为目标回波复幅度;和分别表示杂波和内部热噪声矢量;为归一化信号空时导向矢量。根据最大信杂噪比准则,最优权矢量通过求解如式(4)线性约束最优化问题得到

(4)

解得=μ,其中=1()

2.2 3DT-STAP的原理

3DT算法采用相邻三个多普勒通道作为时域自由度,天线子孔径作为空域自由度,共同构造空时二维导向矢量,再结合杂波协方差矩阵分解获取相应的权矢量,对空时两维数据进行二维滤波,从而抑制杂波,检测动目标。该方法可以在距离-多普勒域形成相对比较窄的凹口,有利于检测地面低速目标,同时由于用了更多的自由度,无论在主瓣区还是在副瓣区都能取得比较好的性能。

从数学的角度,3DT处理可以等效成采样数据矢量通过一个×3的降维矩阵的线性变换过程,其中和3分别为降维前后的数据维数。 降维前后的数据矢量和信号导向矢量有如式(5)关系。

(5)

降维后的杂波协方差矩阵为

(6)

根据线性约束最小方差准则(),相应的最优权矢量为

(7)

图2 mDT-STAP信号处理流程图

3 信号处理软件设计

信号处理的处理架构为1+,即1片C6678负责数据分发,片C6678负责处理,处理芯片之间的任务分配,采用轮询策略。信号处理的软件设计包括数据分发、片间通信和并行处理三个方面。

3.1 数据分发

信号处理板的第一片C6678芯片收到接口板发过来的数据之后,以脉冲为基本单位进行数据分发。由于DSP的最小处理单位为一个波位,第一片6678在进行数据分发时,先判断当前脉冲所在的波序号,相同波序的数据分发给同一处理芯片。

考虑到雷达设计时序时,不同方位的脉冲数不同,从而每个波位的数据量也不尽相同,这样在以波位为单位的调度和处理时,会造成负载的不均衡。因此我们在设计分发策略时,采用自适应调度策略,即每次进行数据分发时,都会判断对应DSP的忙闲状态,并将数据分发给处于‘闲’状态的DSP,具体流程如图3所示。

图3 数据分发流程

3.2 通信机制

为了提高效率,减少不必要的时间和存储空间的开支,信号处理采用裸系统运行,将全部资源用于处理数据。这样也就带来了一个新的问题,如何快速有效地在DSP芯片之间进行通信呢?

我们基于已有的RapidIO协议,建立了一套完整的片间通信机制,该机制已应用于某工程,运行良好,主要工作原理如下:

1)上电后,每块信号处理芯片需要向第一片C6678的固定内存地址发送状态标识1,表示该板卡做好准备接收数据。

2)第一片C6678在分发数据时,只将数据分发给状态标识为1的板卡,若轮循至某板卡,而该板卡状态标识非1,则跳过该芯片,发送给下一芯片。

3)C6678处理芯片接收完一个完整的波位数据时,将其对应内存地址的状态置为0,不再接收数据。

4)处理芯片处理完当前波位数据,将状态标识置为1,准备下一次处理。

3.3 DT-STAP的并行处理

3DT-STAP处理包括脉冲压缩、MTI、多普勒滤波、样本选取、空时自适应滤波处理以及恒虚警检测,流程如图4所示。

图4 处理流程

工程实现时,为了减少系统的设备量,降低成本,我们希望充分发挥C6678的处理能力,采用8核并行处理架构。事实上,由于信号处理为串行处理架构,即必须保证一个节点完成后再进行下一个节点的运算,因此对3DT-STAP整体上进行分解,从而实现8核并行处理,显然不可能。

我们的实现策略是,在每个处理节点,将任务平均分到8个运算核,实现并行处理,然后在每个节点之后再8核同步一下,保证该处理节点任务彻底完成。这样就可以发挥C6678的8核并行处理能力了。

在将每个处理节点数据分解到8个核的过程中,因为每个处理节点的数据处理方式不一样,在分解时需要对数据进行解耦,保证每个核的数据输入对其它核没有依赖,处理结果也不会影响其它核。对3DT-STAP算法进行分析之后,每个处理节点的任务分解策略如下:

1) 脉冲压缩:由于不同脉冲的处理顺序并无要求,且相互独立,可以分核按照脉冲个数进行任务划分,每个核处理总脉冲数的八分之一。

2)多普勒滤波:不同距离单元的数据相互独立,因此按照距离单元进行划分,每个核处理距离单元总数的八分之一。

3)空时自适应处理:因为不同频道之间数据处理相互独立,故自适应滤波的处理分频道进行。

4 实测数据处理

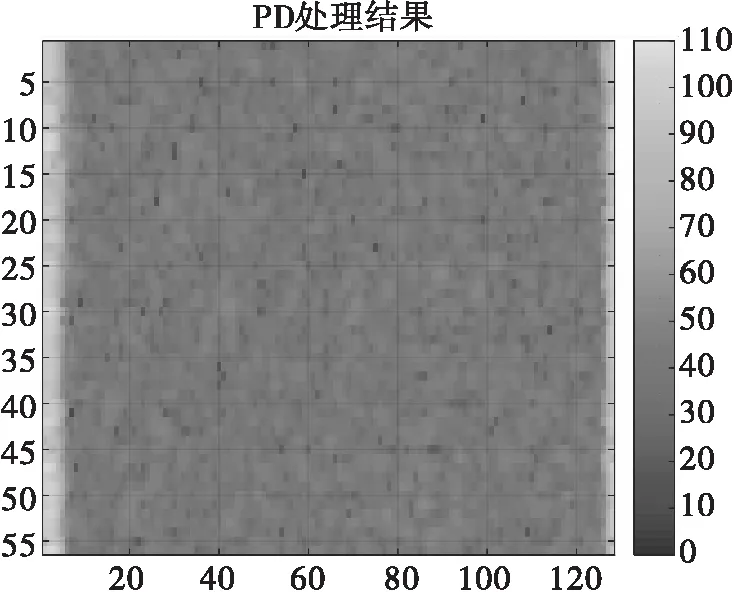

图5为某实测数据经过PD处理后的距离-多普勒二维谱,图6为该批数据经过STAP处理的距离-多普勒二维谱,圆形区域为配试目标所在位置。从两图的对比可以看出,经过3DT-STAP处理之后,主瓣杂波和副瓣杂波区域被明显削弱,使得处于副瓣杂波区域的目标能量显著增强,有效提高了目标的信杂噪比(约为3 dB)。

图5 PD处理结果

图6 3DT处理结果

5 结束语

本文搭建了一套基于c6678信号处理板用于实现3DT-STAP的硬件系统,提出了一套自适应的数据分发机制和芯片之间的通信机制,并在深入理解3DT-STAP算法的基础上,结合C6678的处理器特点,提出了基于处理节点的8核并行处理算法。需要指出的是,本文的处理架构和并行处理思想不仅适用于3DT-STAP处理,对于常规的PD处理及类似算法均可适用。最后,实测数据的处理结果验证了本系统的正确性和有效性。