高速线阵CCD驱动与数据采集系统设计

2022-04-19田又源刘云阳高晨斐

田又源,程 瑶,贾 宁,刘云阳,高晨斐

(重庆理工大学机械工程学院,重庆 400054)

0 引言

CCD具有灵敏度高、动态范围大、功耗低、分辨率高等特点[1-2],在光谱分析、非接触式测量、表面检测等领域应用广泛[3-6]。FPGA产生CCD驱动时序是比较主流的方法[7],因其调试简单,灵活性较高,能通过直接修改驱动程序的方式改变驱动频率和积分时间,缩短开发周期[8]。

虚拟仪器技术利用计算机的资源使硬件软件化,能够实现高速数据处理和海量存储,降低系统成本,增强系统灵活性[9],同时提供了大量的驱动程序和数据分析函数。由此,本文提出一种基于FPGA和虚拟仪器的高速线阵CCD驱动与数据采集系统。

1 系统总体设计

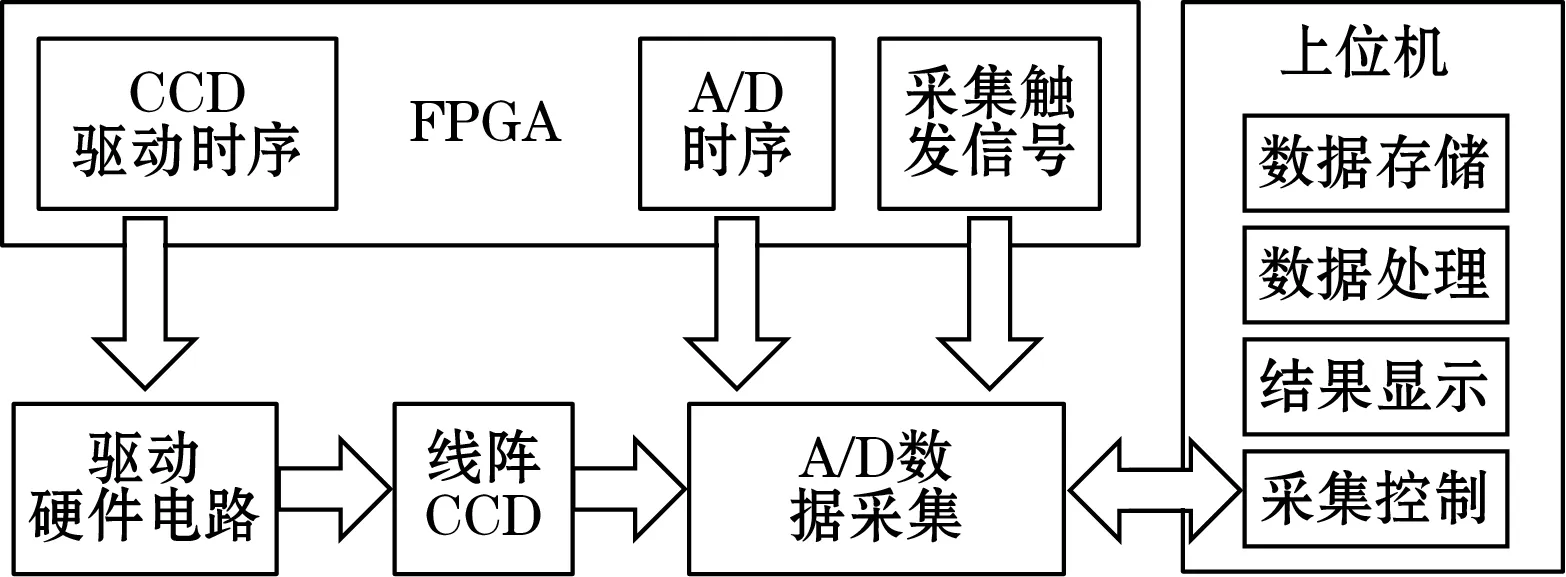

系统原理框图如图1所示,系统由FPGA、驱动硬件电路、线阵CCD、A/D数据采集以及上位机组成。采用FPGA作为主控芯片,控制线阵CCD和提供A/D数据采集的时钟源,负责产生CCD工作所需的驱动时序、A/D采集时序以及采集触发信号;驱动硬件电路驱动CCD工作以及为其提供稳定可靠的电源,保证CCD正常工作;CCD的输出为模拟信号,所以需要A/D采集将输出信号量转化为数字信号方能传输至上位机,此部分须满足大容量数据传输的要求,以便实现高速实时测量;上位机控制A/D数据采集的过程,可实现单帧采集、连续采集以及其他采集配置,采集结果可通过波形图直接显示,采集得到的CCD数据可进行数据分析及图像处理等操作。

图1 系统框图

2 硬件设计

2.1 驱动硬件电路设计

系统采用TCD1708D作为感光元件,它是高灵敏度、低暗电流的线阵CCD图像传感器,采用奇偶双通道输出(引脚分别为OS1和OS2),信号输出速度显著提高,其有效像敏单元高达7 450个,光敏单元中心之间的距离仅为4.7 μm,具有超高的分辨率,适用于高精度、高速率测量系统。系统主控芯片选择的是EP4CE10F17C8芯片,该芯片具有功耗和性价比优势,拥有10 320个逻辑单元和最大179个用户I/O等,满足此次设计需求。TCD1708D需要5路驱动信号,且驱动信号电压典型值为5 V,而主控芯片提供的I/O引脚电压仅为3.3 V左右,所以二者之间需要进行电平匹配,只有驱动信号正常才能保证传感器输出完整、稳定可靠的信息。

驱动硬件电路见图2。电平匹配选用特性双向电压转换器SN74LVC4245APWR芯片实现3.3 V至5 V的电平转换,该芯片转换驱动时序的电压无需反相设计,且该芯片电平的理论上升和下降时间低于2.5 ns,满足本设计高速的需求。另外,需分别提供3.3 V和5 V的基准电压给电压转换芯片,故使用稳压芯片SE8117T33HF将5 V电源转换为3.3 V电压,5 V电压则直接由VCC提供。

2.2 A/D采集设计

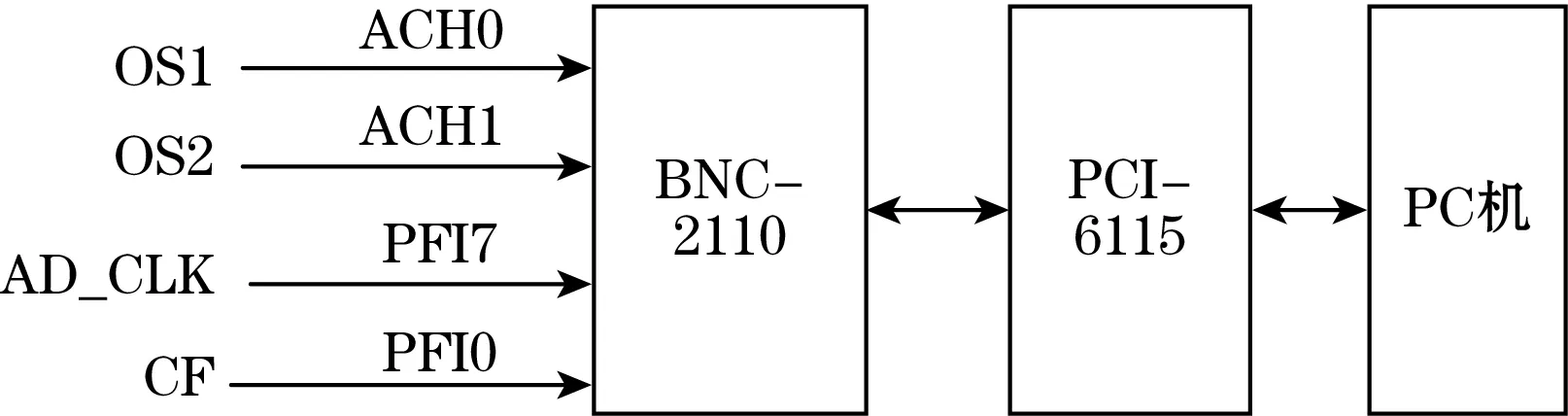

TCD1708D是奇偶双通道同时输出视频信号,信号输出速率的提高对数据采集性能要求也随之提高。本设计中A/D数据采集使用虚拟仪器技术,利用高性能、灵活的标准软硬件平台,针对CCD器件特殊的输出信号进行同步采集。A/D数据采集的硬件由BNC-2110接线盒、同轴电缆、PCI-6115型同步采样多功能数据采集卡及PC机组成。其中,PCI-6115含有4路模拟输入通道,每通道均带有内置防混叠滤波器,10 MS/s同步采样速率,12位分辨率(±42 V),特点之一是拥有大容量的板载SDRAM内存,为测量CCD输出信号提供了稳定可靠的数据采集功能。

虚拟仪器硬件配置如图3所示。CCD输出信号、采集触发信号与采集时钟信号均通过接线盒经同轴电缆接到数据采集卡。CCD 2路输出信号通过同轴电缆分别接入接线盒的ACH0和ACH1端,则系统运行时电压输入通道应选择“ai0,ai1”,接线端配置选择伪差分。触发信号CF正端接PFI0,系统运行时应选择数字触发边沿为rising,触发通道输入PFI0。采集时钟信号AD_CLK正端接PFI7,则系统运行时采样时钟源类型选I/O Connector中的PFI7通道。

图3 虚拟仪器硬件配置示意图

3 软件设计

3.1 CCD时序设计与仿真

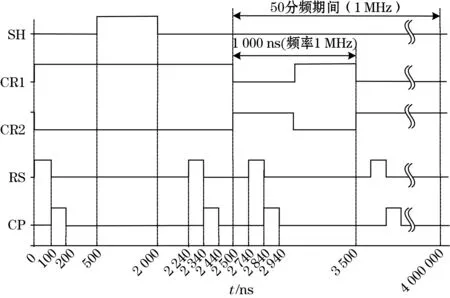

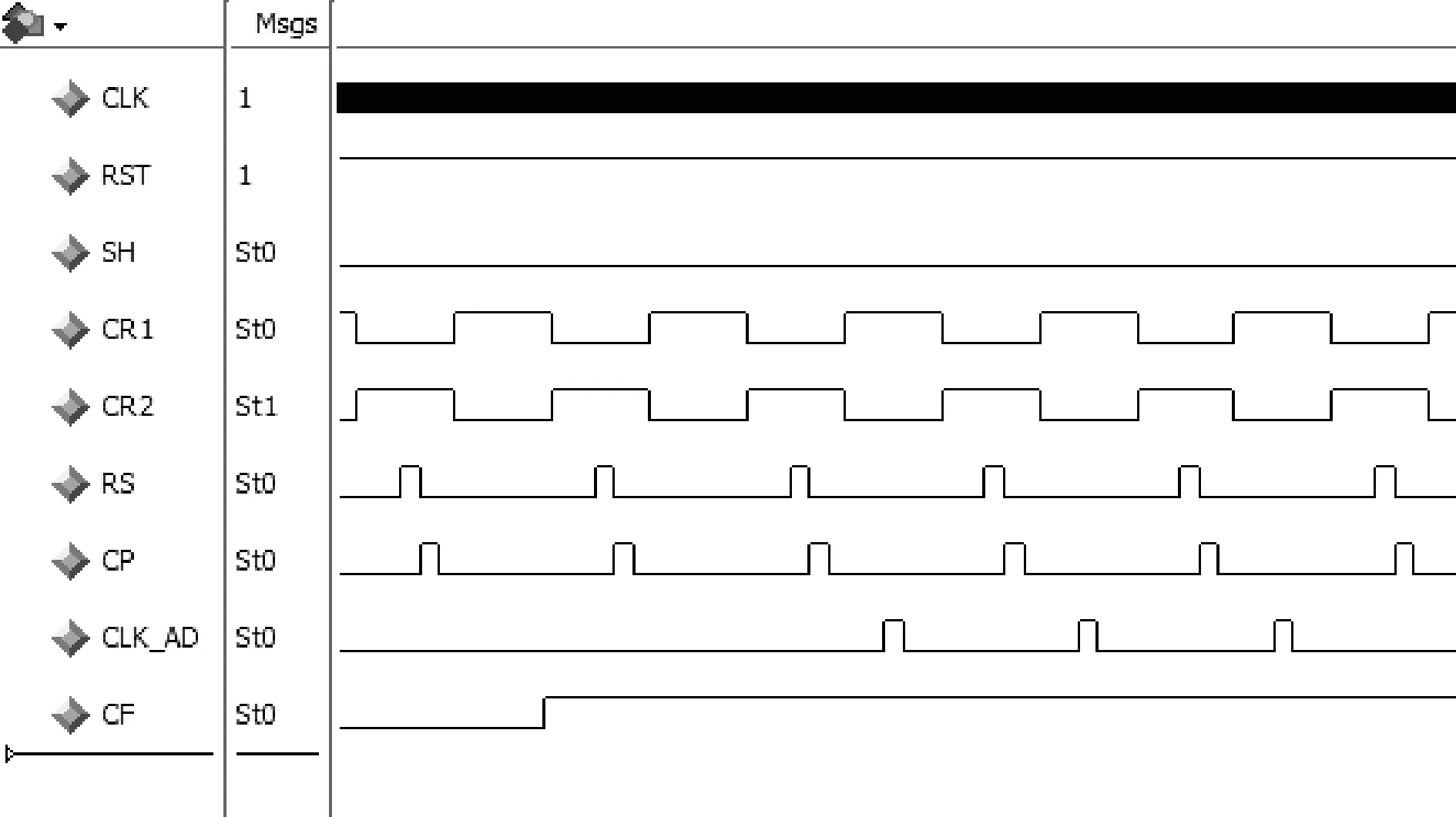

CCD的时序设计使用Quartus II 13.1作为开发平台,用硬件描述语言Verilog HDL进行编程设计。TCD1708D需要5路驱动信号,包括转移驱动信号SH、模拟移位寄存器驱动信号“Ф1E,O”(即CR1)和“Ф2E,O,Ф2B”(即CR2)、复位驱动信号RS、钳位脉冲信号CP。

对照TCD1708D的驱动时序要求,设计时选用主时钟CLK频率为50 MHz,通过对主时钟50分频,利用计数器可将驱动信号CR1、CR2、RS、CP均设计为典型驱动频率1 MHz。奇、偶每个通道都有3 797个像元,驱动脉冲取整设计为4 000个,留有一定的空余。依照各驱动信号的同步时序要求设计如图4所示的对应关系时序图,主频时钟CLK为50 MHz,所以对应的计数器CNT每20 ns累加1次,其中在CNT≤124(2 500 ns)时按照芯片手册的timing chart波形设计,在CNT>125之后则开始设计50分频以便得到频率为1 MHz的计数器,设计CR1和CR2反相且占空比为1∶1、RS和CP信号占空比为1∶9。

图4 驱动信号同步时序设计

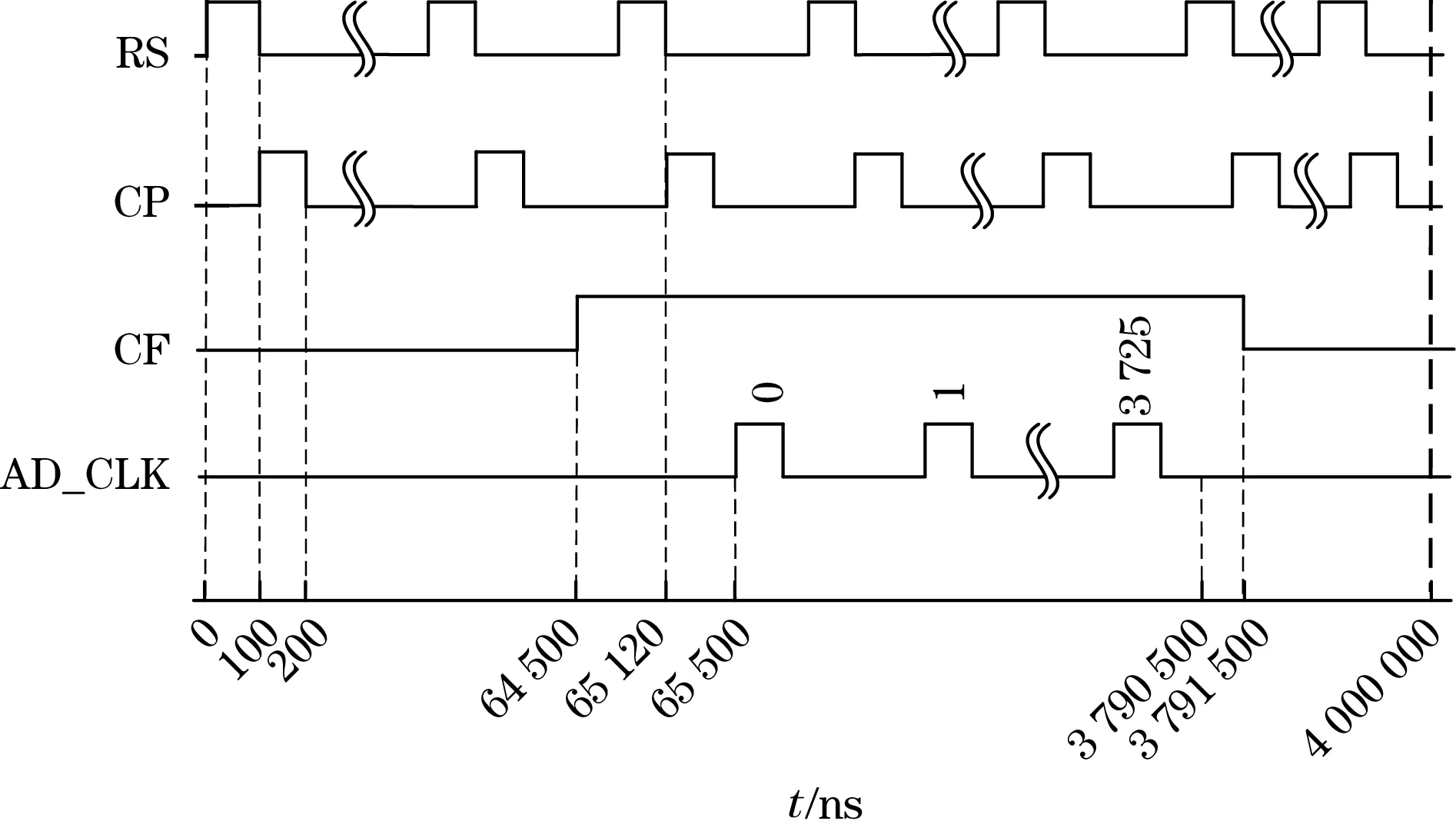

3.2 A/D采集时序设计

TCD1708D每路通道的光敏像元前64个和后8个均为无效像元,有效像元均为3 725个,则设计采集触发信号CF在其输出有效像元时间段拉高,A/D信号同步时序设计如图5所示。在进行50分频之前传感器已输出一个无效像元,故分频后前端只剩63个无效像元,故65 500~3 790 500 ns期间为奇偶双路每路3 725个有效像元输出时间,则在此期间AD_CLK设计为滞后RS信号380 ns拉高,高电平持续时间100 ns,即距下一次复位间隔520 ns,留有充足的时间采集稳定的CCD模拟输出信号。

图5 A/D信号同步时序设计

由Quartus设计的驱动、采集时序程序编译无误后与ModelSim10.1d联合仿真,得到结果如图6所示,对照芯片手册以及设计思路可知仿真结果满足TCD1708D的时序要求。

图6 驱动时序仿真局部放大图

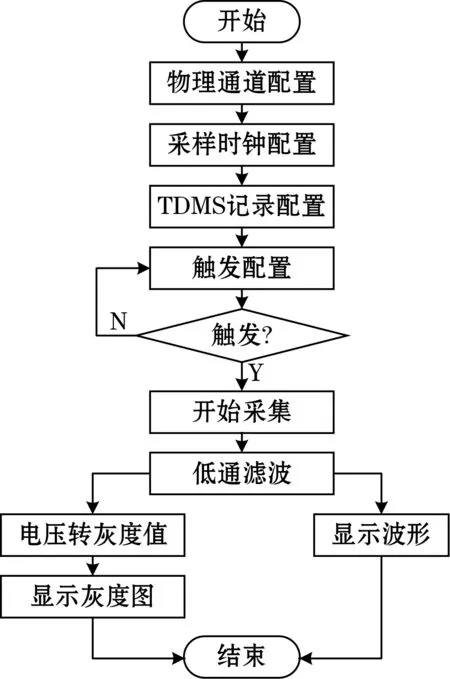

3.3 上位机程序设计

采用LabVIEW设计上位机程序实现对采集卡的控制、数据处理等功能,上位机程序设计流程见图7。使用NI-DAQmx驱动程序和配置实用程序控制采集卡完成CCD数据的采集。首先读取包括物理通道、采样时钟、TDMS记录和触发在内的采集参数配置。配置好后,循环检测等待触发信号CF高电平的到来,检测到触发后,开始采集物理通道的CCD模拟信号,再经过低通滤波滤除部分噪声,得到较好的电压信号。对得到的数据可通过波形图显示,也可以通过编写算法进行一系列的处理,例如电压值转灰度值进行显示,或是编写边缘检测算法实现一些测量等。

图7 上位机程序流程图

4 实验结果

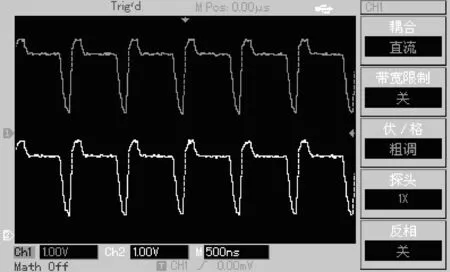

根据TCD1708D的驱动时序要求,将驱动程序下载至FPGA,通过示波器检验无误后,连接驱动电路及CCD,使用示波器观察CCD双路的输出信号如图8所示,对比芯片手册可知CCD正常输出成像信号,光强改变时,CCD输出信号也能随之变化,这验证了驱动电路设计的正确性。

图8 CCD输出信号波形图

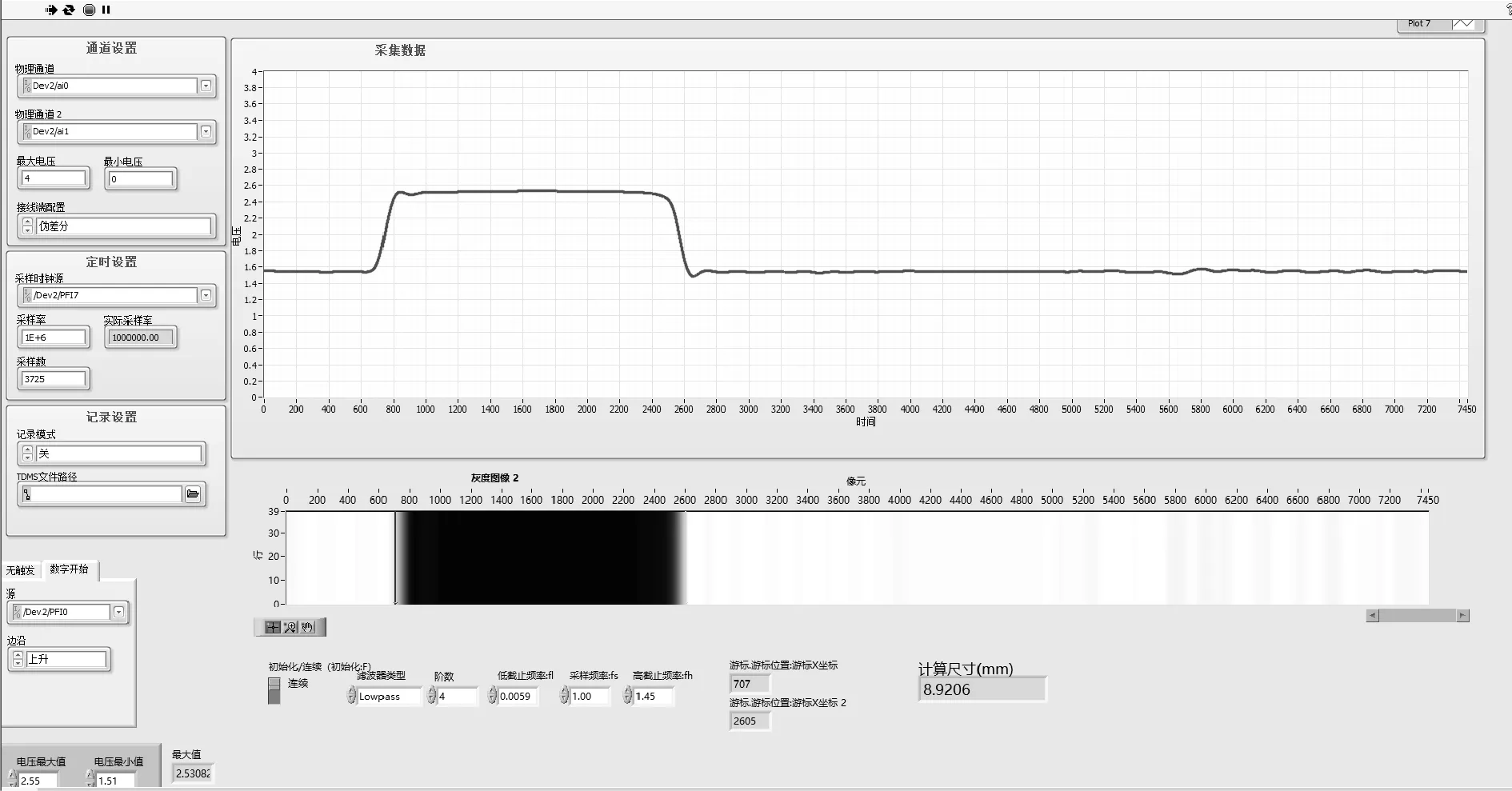

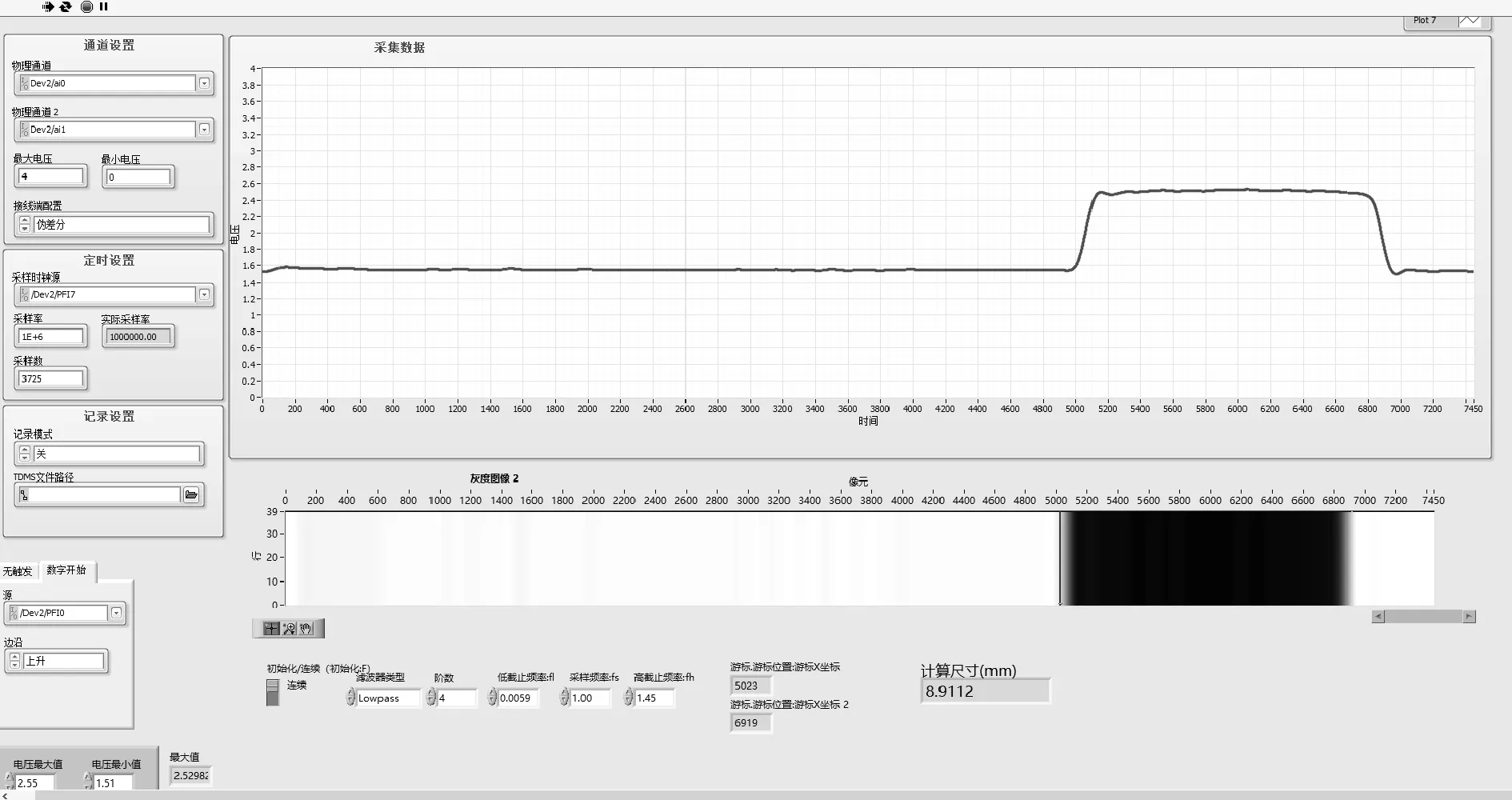

将2路输出信号OS1和OS2与BNC-2110通道ACH0和ACH1接线,触发信号CF接PFI0,时钟源CLK_AD接PFI7。通过NI MAX检查PCI-6115是否已连接成功,按照接线配置程序。在室内使用平行光源照射CCD感光面,再将宽8.92 mm的标准量块置于光源与CCD之间,垂直感光面平行移动量块遮挡CCD左边部分感光面,再将其慢慢移动至CCD感光面的右边位置,结果如图9所示,图中曲线凸起处为量块在感光面上的平行投影,边缘处上升沿和下降沿处清晰,曲线无明显毛刺、噪声,图中下部分为实时图像显示,黑色区域为量块的投影,边缘特征同样分明,在整个移动过程中系统能够实时显示对应的图像画面及波形,测试结果表明驱动硬件电路、数据采集都能正常稳定工作,该系统运行良好,能够高速、准确地采集CCD数据。

(a)左侧遮挡结果

(b)右侧遮挡结果图9 左、右侧遮挡位置系统界面

5 结束语

设计了符合要求的驱动时序,以FPGA作为主控芯片产生驱动CCD的正确脉冲,使用所设计的CCD驱动硬件电路能够使CCD正常工作,经示波器检验得到正确的波形输出。以LabVIEW为开发软件结合PCI-6115采集卡,搭建了一套高速线阵CCD数据采集系统,实验表明该系统能够高速采集CCD数据,具有高速、实时、易修改、传输数据量大等优点,具有FPGA和虚拟仪器技术的优势。