一种低功耗高速率宽电平范围的电平转换单元

2022-04-01胡庆成吴建东万璐绪

胡庆成,吴建东,万璐绪

(中科芯集成电路有限公司,江苏无锡 214072)

1 引言

在复杂的片上系统中,常采用多电压技术来实现低功耗和高性能的折衷,电平转换单元有效地实现了不同电压域之间的数据交互[1-2]。电平转换单元分为从高电平到低电平转换和从低电平到高电平转换两种。高电平到低电平的转换可以通过简单的Buffer驱动器来实现。低电平到高电平的转换由于低电压不能很好地驱动高电压,就无法实现高速率数据的传输,不能在功能、功耗和时序上达到很好的匹配[3-4],因此兼顾高速率和宽电平范围的电平转换单元成为多电压系统设计中的一个重要挑战。

为了解决宽电平范围的电平转换,已有很多电平转换结构的研究。文献[5]中提出的电平转换单元是在传统结构的基础上增加了二极管形式连接的PMOS管以限制上拉电流,同时还增加了两个一直处于截止区的PMOS管用于匹配上拉和下拉的驱动能力,但是由于二极管接法的PMOS管存在电压降,无法保证输出电压全摆幅,限制了输出电压的变化范围。文献[6]中提出了两级电平转换结构,在第一级中引入了二极管接法的NMOS管,该结构原理简单,但二极管连接的NMOS管的引入同样也会限制输出电压的变化范围。文献[7]利用衬底偏置效应调整输入级和输出级晶体管的阈值来实现TTL电平到CMOS电平的转换,电路结构简单,但在低供电电压下电路应用就会受到限制。

本文提出了一种电源电压在1.0~5.5 V范围内,最高支持1 Gbps转换速率的电平转换单元,在保证高速率、全摆幅输出的同时仍具有很短的响应时间。

2 电平转换单元设计

2.1 传统电平转换单元

图1为传统电平转换结构原理图,电路采用单一阈值晶体管。当输入电压高于N1或N2管的阈值电压时可以实现两个电压域之间的数据交互。当输入信号从逻辑低电平变为逻辑高电平时,N2管打开,N1管关闭,此时B结点通过N2管到地的通路被下拉到GND。当结点B的电压低到(VCCOUT-VTHP)以下时(式中VCCOUT为电平转换输出端的电源电压,VTHP为PMOS管的阈值电压),P1管开启将A结点拉高,关闭P2管;当输入信号从逻辑高电平变为逻辑低电平时,N1管打开,N2管关闭,A点被下拉到GND,P2管开启,输出高电平信号,幅度接近于VCCOUT。

图1 常规的电平转换单元

当B点初态为低电平时,P1管处于开启状态,此时若输入信号为低电平,那么N1管也将开启,P1管和N1管之间存在同时开启的状态,无法快速将A点电位下拉到GND;同样的,当A点初态为低电平时,B点电位也无法快速下拉到GND。由此可见,传统电平转换结构中,A、B两点的电位无法在电平转换瞬间实现较快的电平响应,较大的传输延时导致其无法实现高速率的电平转换。此外,单一阈值的MOS管也无法实现较宽电压范围的电平转换。

2.2 本文提出的电平转换单元

为解决传统电平转换电路中高速信号变化瞬间电平响应慢的问题,减小电路的静态功耗和传输延时、拉宽电平转换范围,在0.18μm CMOS工艺基础上进行了电路设计。在传统电平转换单元结构基础上调整N1管和N2管为低阈值管,可有效拉宽电平转换的低输入电压范围;引入与VCCOUT相关的使能信号以及由使能信号控制的P0、N0和N3管以降低电路的静态功耗;引入P3管和P4管以调节高速信号变化瞬间电路的响应速度,从而达到提高电路转换速率的目的。本文提出的电平转换电路结构如图2所示。

图2 本文提出的电平转换电路结构

当使能信号EN为高时,P0管打开、N0管关闭、N3管打开,电路处于关闭工作状态,OUT信号输出低电平,幅值接近于GND,此时静态功耗很低。当使能信号EN为高时,P0管关断、N0管打开、N3管关断,电路处于正常工作状态。

根据MOS管传输特性,当VGS>VTH时,其饱和电流为:

式中IDS为MOS管源漏电流,单位为A;μ为电子/空穴表面迁移率,单位为m2/(V·s);Cox为单位面积栅氧化层电容,单位为F;W为MOS管栅宽,单位为m;Leff为MOS管有效沟道长度,单位为m;VGS为MOS管栅源电压,单位为V;VTH为MOS管阈值电压,单位为V。

假设VCCIN<VCCOUT(式中VCCIN为电平转换输入端的电源电压),当使能有效进入正常工作状态,信号IN输 入 逻 辑 低 电 平 时,VGSN1=VCCIN,VGSP1=VCCOUT,VGSP4=VCCOUT-VCCIN,式中VGSN1、VGSP1和VGSP4分别为MOS管N1、P1和P4的阈值电压,P4管的引入有效减小了传统结构中P1管和N1管之间的中间态时间,在高速信号翻转的瞬间,A点可以根据输入信号的状态快速响应以实现低延时的电平转换,提高转换速率。同理,P3管的引入也可以提高B点的快速响应时间,并且OUT信号可以全摆幅输出。

3 仿真结果与分析

以本文所述电平转换单元结构为模块设计了四通道的电平转换电路,整体功能框图如图3所示,版图如图4所示。

图3 以电平转换单元为主模块的电路功能框图

图4 流片后的芯片照片

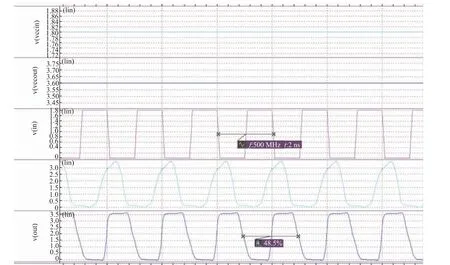

基于0.18μm CMOS工艺模型库,在1.0~5.5 V全电压范围内进行Hspice仿真,转换速率从1 Mb/s覆盖到1 Gb/s。考虑到应用时外围负载的影响,在仿真中加入了寄生参数,负载采用15 pF电容和2 kΩ电阻到GND。图5展示了1.8 V转3.6 V的仿真波形,转换速率可达1 Gb/s。

图5 1.8 V转3.6 V仿真波形

流片的实际电路在V93000系统中进行实测,测试波形如图6所示。测试结果表明,电路的实际转换电压范围为0.9~5.5 V,静态功耗小于2μA,实测最高转换速率为800 Mb/s。

图6 电路在不同电压转换下的测试波形

表1为以本文所提电平转换单元为主体设计的四通道电平转换电路实测值与部分参考文献中电平转换电路的性能参数的对比。从表中可知,本文提出的电平转换单元在引入低阈值NMOS管、加速下拉P管及衬底偏置效应后,电平转换范围、转换速率和传输延时等参数方面均优于现有的其他数据。

表1 本文与部分参考文献中电平转换电路的参数对比

4 结论

本文设计了一种低功耗、高速率、宽电平范围的电平转换单元,采用低阈值NMOS管拓宽了电压范围;采用使能控制降低了电路静态功耗;增加PMOS管改善响应速度提高转换速率。实际流片结果表明,以该电平转换单元为模块设计的四通道电平转换电路静态功耗小,在1.0~5.5 V电压范围内转换速率最高可达800 Mb/s。电压转换范围和静态功耗达到了预期,转换速率略低了一点,还需要进一步优化改善。基于本文提出的电平转换单位进行电路设计,具有低功耗高速率宽电平等特点,在高速电平转换接口领域有较大的优势和应用前景。