一种高速背板连接器的设计

2020-06-29木青峰曹永泉苏文玉

木青峰 曹永泉 苏文玉

要:对一种高速率数据传输连接器进行了理论设计与仿真分析。对连接器的接触件、屏蔽结构等细节进行设计,从时域、频域对该设计进行了电磁仿真分析与优化,信号完整性仿真结果表明:连接器的高速性能满足56 Gb/s的高速数据传输要求。

关键词:高速率;数据传输;连接器;信号完整性

0 引言

基于我国信息化战略的要求,通信领域、消费电子、大数据领域持续快速发展。受益于行业的繁荣,具有“连接器明珠”之称的高速背板连接器占据了大量市场份额。

高速连接器的密度与传输速率越来越高,空间限制与速率提升使得连接器设计和制造难度进一步加大,高速率数据传输在连接器内遇到的信号完整性问题越来越突出,具体体现在因信号耦合而产生的串扰越来越严重。本文根据实际需求,设计一种高速背板连接器,传输速率达56 Gb/s,经信号完整性仿真验证,本设计满足使用要求。

1 高速连接器设计

1.1 设计指标

结合使用要求,连接器设计的技术指标如下:

(1)特性阻抗:(92±10)Ω;

(2)近端/远端串扰≤-30 dB;

(3)插入损耗(绝对值)≤3 dB;

(4)回波损耗≤-10 dB(0.05~

15 GHz)/≤-5 dB(15~28 GHz)。

1.2 整体结构设计

连接器分插头、插座两部分。插座由基座、屏蔽件、信号接触件组成(图1);插头采用wafer(信号模块)阵列排布模块化设计,由基座、wafer、固定件组成(图2),其中wafer包含差分信號对与屏蔽件(图3)。

1.3 连接器footprint设计

连接器的footprint信号针与接地针的布局对串扰影响较大,根据相关研究分析(图4、图5)[1],相邻wafer的差分对交错排列是降低串扰的有效方法。图4所示为差分对两种排列方式,交错型排列的相邻差分对错开一定距离D。图5为两种排列差分对串扰仿真结果,从图5可以看出,交错排列近端串扰优化约20 dB,远端串扰优化约30 dB。考虑到空间限制以及某一差分对受周围差分对的影响,D并不是越大越好,一般小于λ/4(λ为信号波长)。本设计从连接器外形、信号完整性两方面考量,取D=1.1 mm。

1.4 接触件设计

连接器接触区是阻抗失配较为严重的区域。出于可靠性考虑,弹性接触件头部一般伸出一段“短桩(stub)”作为接触件插合的导向,正是这一段“短桩”易造成谐振,我们称之为“短桩效应”。为克服短桩效应,本设计采用图6所示的双触点接触件。经信号完整性仿真验证:单触点接触方式,连接器在27 GHz有谐振点(图7);双触点接触方式消除了27 GHz的谐振点。

1.5 屏蔽结构设计

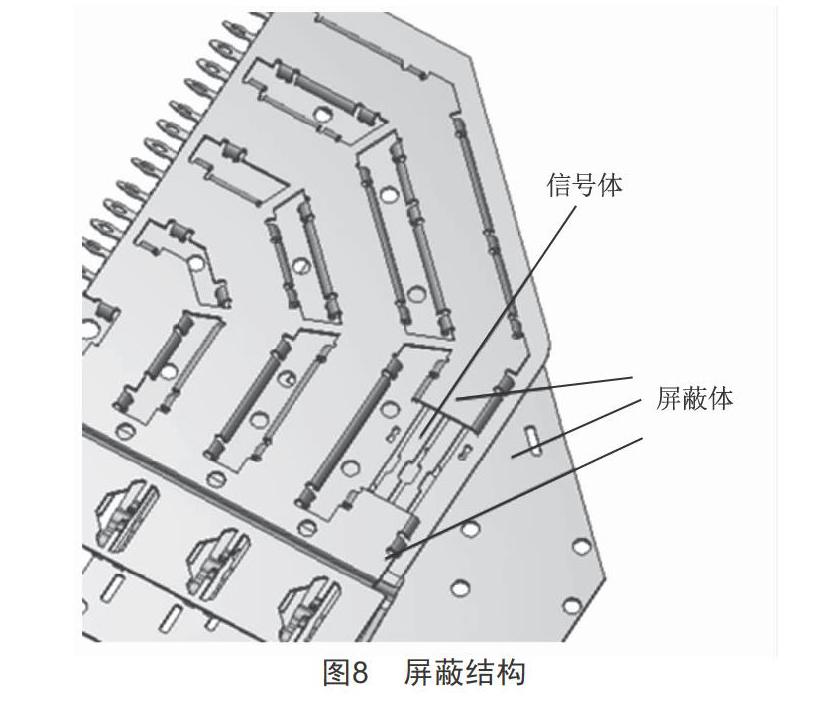

屏蔽结构设计需综合考虑产品空间、零件成本、工艺性、可靠性等多方面因素。本设计为满足56 Gb/s速率传输要求,屏蔽结构将信号传输360°包围,为高速率信号提供完整的返回路径,同时屏蔽不同差分对间的耦合。图8所示屏蔽体零件由卡扣结构铆合固定,差分信号体更靠近平面度易控制的零件。

1.6 差分对等长设计

根据经验,差分信号的相位差不能大于信号周期的1/10。差分对外侧的传输线比内侧的机械长度长,根据电磁波在不同介质中传播速度[式(1)]不同的原理,可通过调整差分对周围介电常数的方法,完成差分对两条线路电气等长设计。

信号在传输线上的传播速度为:

如图9所示,内侧传输线周围介质节点常数大于外侧,使信号在内侧传输线传输速度变“慢”。

2 高速连接器信号完整性仿真分析

高速连接器结构复杂、形式多样,在设计初期用理论分析方法对其性能进行粗略估算。高速连接器的零件一般为开模件,若因信号完整性问题对零件结构、尺寸进行调整,则面临高昂的经济与时间成本。本文采用相关电磁场仿真模拟软件对本设计的高速传输性能加以验证,如图10~14所示。

仿真结果显示:上升沿21.9 ps(10%~90%),阻抗为84~98 Ω;插损优于1.8 dB(0~30 GHz),回损优于-13 dB(0.05~15 GHz)以及-8 dB(15~28 GHz);串扰优于30 dB。仿真结果表明,本设计满足指标要求,并仍有速率升级空间。

3 结语

本文根据实际需求,对高速背板连接器进行结构、信号完整性设计,目前产品处于样品测试阶段,接下来进行产品验证工作。受限于模具加工工艺水平,有些零件结构进行了让步设计。相信随着设计水平和工艺水平的提高,国内将涌现出越来越多性能优异、成本经济的高速连接器。

[参考文献]

[1] 徐斌.高速背板连接器的设计与应用[D].南京:南京邮电大学,2017.

收稿日期:2020-03-18

作者简介:木青峰(1990—),男,湖北襄阳人,助理工程师,研究方向:高速互连。