基于ATE的USB PD快充协议芯片晶圆测试

2022-04-01唐彩彬

唐彩彬

(中科芯集成电路有限公司,江苏无锡 214072)

1 引言

USB功率传输(Power Delivery,PD)协议于2013年的更新标准名为USB PD。USB PD协议是基于USB3.1,在Type-C端口后提出的功率传输概念。USB PD可以为快充技术带来更大的灵活性,可以将充电能力扩大为目前的10倍,最高可达100 W[1]。

OB2613是一款高精度高集成度的USB PD控制器,已于2018年11月获得USB标准化组织(USB Implementers Forum,USB-IF,)的PD3.0+PPS认证,并于2018年12月通过高通QC4+的测试认证,其符合USB PD3.0 V1.1规范,支持PPS模式,支持QC4/4+、BC 1.2协议、MTK PE+、华为FCP协议、Apple快充识别、三星快充识别等[2]。通过预留的GPIO设置可支持A+C口双口快充设计,极具成本优势[3]。

本文针对该款USB PD快充协议芯片,基于Chroma 3380P测试系统,搭建了一套完整的USB PD快充协议芯片晶圆测试平台。该测试方案实现了对该快充芯片晶圆的主要功能与性能参数的测试[4-5],并为快充类芯片测试提供了一种通用方法。

2 Chroma 3380P系统资源配置

2.1 Chroma 3380P简介

Chroma 3380P自动测试系统工作于Windows 7操作系统的环境下,采用CRAFT C/C++程序语言,方便使用Windows所提供的资源。系统采用弹性架构,可根据测试需求选配对应的功能板卡,提供整合密度大、功能强大、具有经济效益的自动测试系统,可满足多种形式的集成电路测试应用。

Chroma 3380P VLSI(Very Large Scale Integration)测试系统机型因其高同测功能(High Parallel Test),除内建的4-wire功能高密度IC电源(VI Source)外,具备any-pin-to-any-site高同测功能(最大支持512 site并行同测),以适应未来IC更高效的测试需求。

2.2 系统资源能力

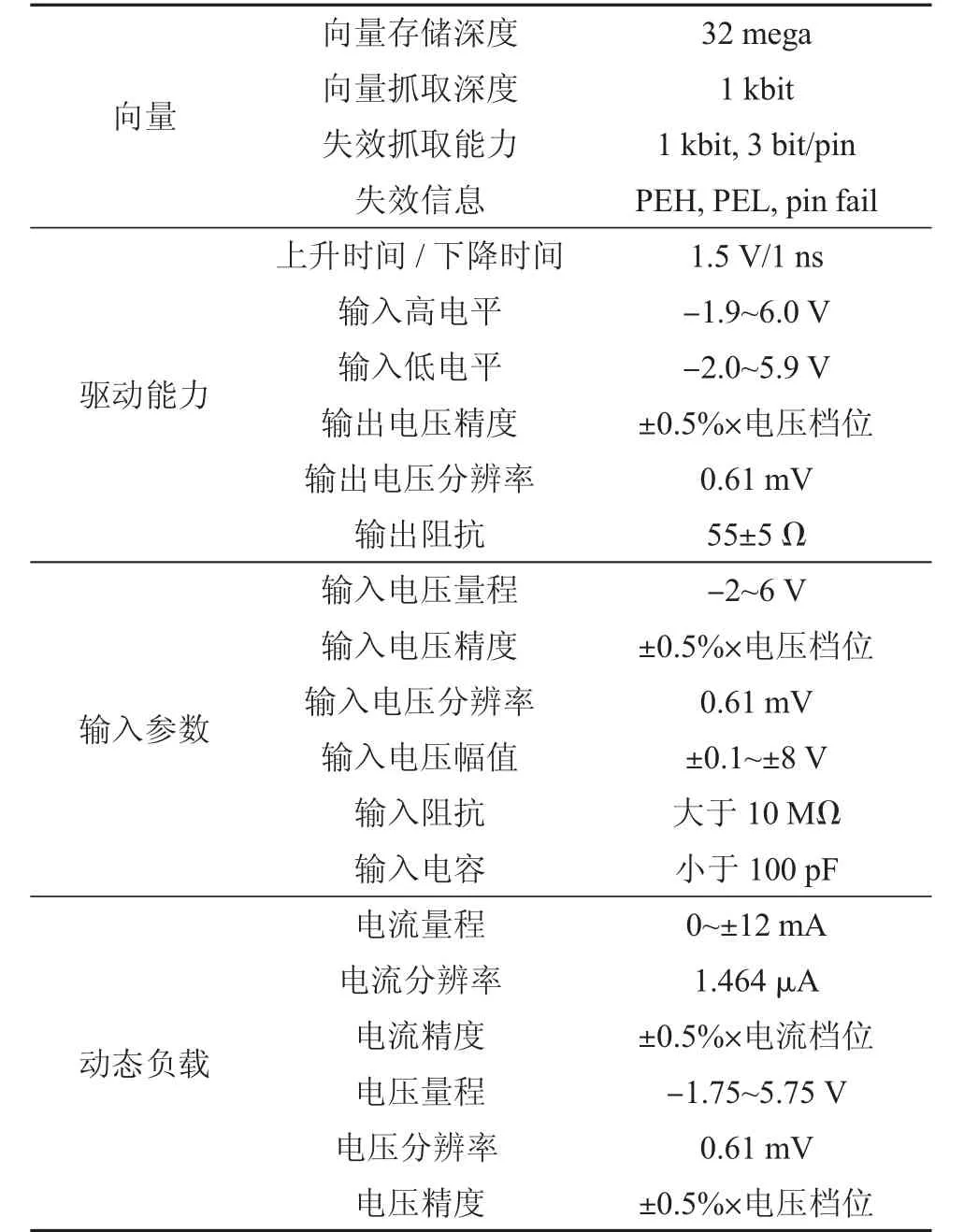

该Chroma 3380P系统可配置MLDPS-16、MLDPS-32、MXREF、MXUVI、MXPMU、PPMU等 板卡,支持gang-mode模式来满足更高的测试要求,板卡资源电流电压能力如表1所示。

表1 卡板资源能力(DPS/PMU/PPMU)

Chroma 3380P每块MXLPC卡板配备64个数字通道,系统最大支持576个数字通道,测试向量最大支持100 MHz测试频率,数字通道的具体参数如表2所示。

表2 MXLPC数字通道具体参数

3 USB PD快充协议芯片测试要求

针对该快充芯片的测试要求,把测试项目拆分成数字参数测试与模拟参数测试两个部分,两部分是相对独立的。

3.1 数字参数测试

1)连接性测试(Continuity Test)也称为开短路测试(Open Short Test),它主要用以确认器件在测试时所有的信号引脚都与测试系统相应的通道在电性能上完成了连接,且没有信号引脚与其他信号引脚、电源或地发生短路或断路。连接性测试能快速检测出被测器件(Device Under Test,DUT)是否存在电性物理缺陷,如引脚短路、bond wire缺失、引脚的静电损坏以及制造缺陷等。

2)SCAN测试是一种结构性测试,它将芯片内部的寄存器替换成专门的寄存器,然后连接成1条或多条链,这种方式只需要在输入端输入pattern,在输出端对比输出即可,它不关心芯片功能,可以节省很多测试开发时间,同时也减少测试时间。

3)BIST (Built In Self Test)测试即内建自测试,BIST是一个专门用于测试的电路模块,能够直接产生测试激励和检测测试响应。芯片内部集成了专门的测试算法,内部也实际集成了测试控制电路、输出结果比较电路等。

4)Bandgap Trim测试。由于工艺的影响,带隙基准电压会有一定的偏差,需要利用trim技术对基准电压进行修调。通过在EEPROM(Electrically Erasable Programmable Read Only Memory)中写入trim code来控制trim电阻以达到修调基准电压的目的;同时采用了自动修调算法,只需要测试基准电压的初始值,就可以自动找出最佳的trim code[6]。

5)针对高电平时的输入电压VIH、低电平时的输入电压VIL、高电平时的输出电压VOH、低电平时的输出电压VOL参数进行的测试。

6)其他功能参数测试。

3.2 模拟参数测试

1)连接性测试(同数字参数部分的连接性测试说明)。

2)基准电压、电流、频率、电阻等参数的测试与熔丝修调。芯片在测试过程中,除了进行直流参数以及功能参数测试外,更为重要的是对芯片进行trim修调[7-8]。因为芯片在制作过程中,由于工艺的影响,其内部的基准电压、振荡器等模块会出现一定偏差,而在芯片大量生产和测试过程中,一旦被测芯片的参数出现偏差,该芯片就会被剔除,这样必然会降低芯片良率,从而增加芯片制造成本[9]。所以,通过对芯片部分参数进行微调,提升芯片的良率就显得十分重要。

3)静态电流与工作电流测试。确保芯片处于低功耗状态与工作状态下的电流消耗在芯片参数手册的范围中。静态电流与工作电流测试是一个至关重要的测试参数,它将直接关系到芯片的功耗,影响终端设备的使用时间。

4)UVLO(Under Voltage Lock Out)测试。当输入电压在标准值以上时,检测输入电压上升,防止芯片误操作而停止电源并发出报警信号,多为系统正常工作时最低输入电压的130%~150%左右;当输出电压在标准值以下时,检测输出电压下降或为保护负载及防止误操作而停止电源并发出报警信号,多为输出电压的80%~30%左右。

5)漏电流测试。通过简单地在被测芯片的输入或输出引脚上施加直流电压,然后测量引脚流入或流出的小电流来测试漏电流。

6)其他模拟参数测试。

4 USB PD快充协议芯片测试实现

测试开发设计时,要根据芯片的测试要求来选择对应的系统硬件资源。根据该快充协议芯片的测试规范,设计了双site并行测试外围。

4.1 芯片测试外围设计

site1的测试原理如图1所示。双site测试方案(不含模拟trim部分)使用了10个DPS源、80个数字通道、11个继电器控制位。

图1 测试外围原理图

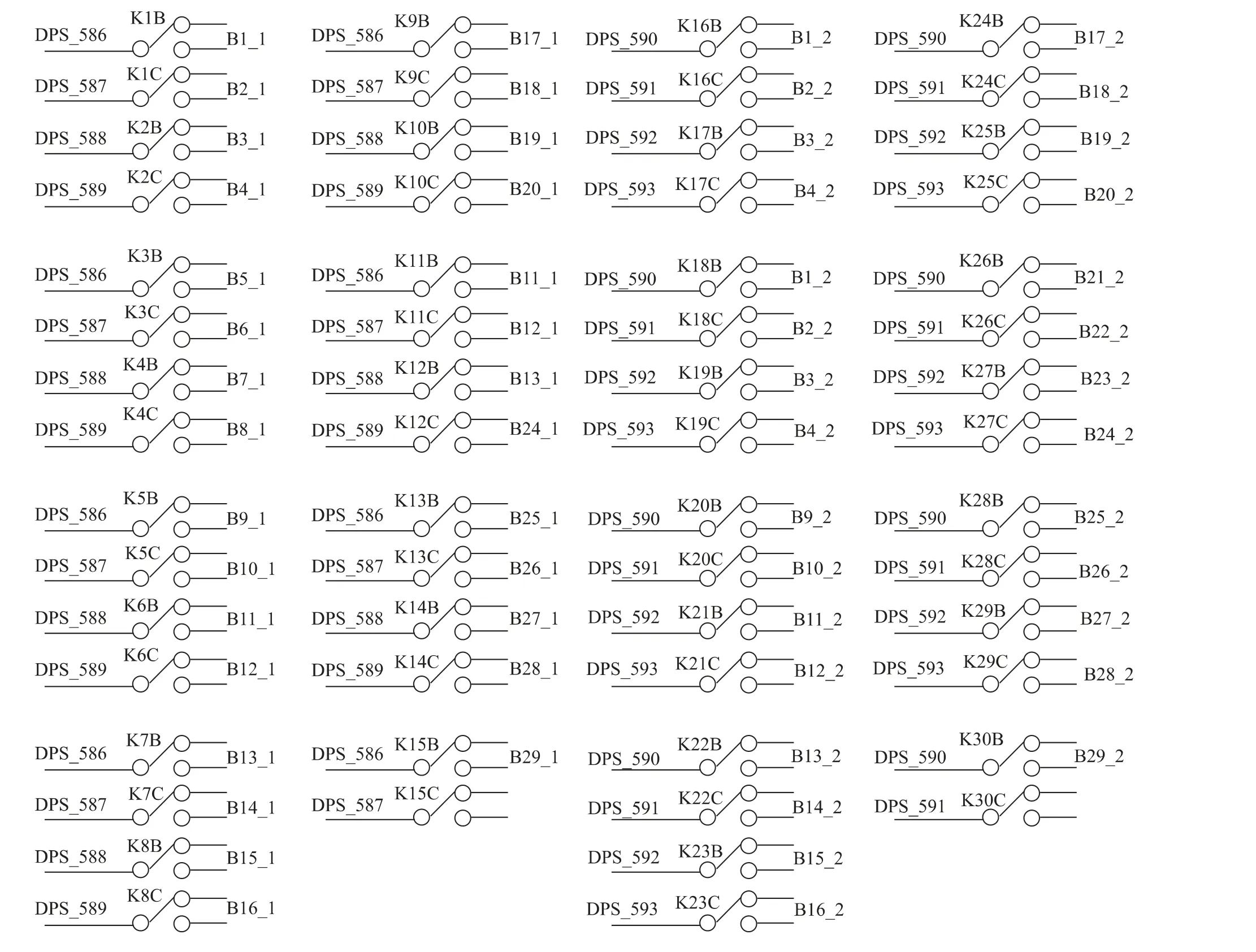

4.2 并行修调电路设计

双site采用并行方式进行熔丝修调,在熔丝两端加5 V电压来熔断,修调电路原理如图2所示。该芯片共29段熔丝,双site熔丝修调部分使用了8个DPS源、30个继电器。熔丝并行修调的方式能够实现多段熔丝一起熔断,能有效提升测试速度,提高测试效率。

图2 修调电路原理图

4.3 测试程序开发

整个测试程序共52个测试项目,其中29个数字测试项目,23个模拟测试项目,基于Chroma 3380P开发了该快充协议芯片晶圆测试方案的测试程序。本方案实现了对该快充芯片基准参数的测试及修调,包括MCU dft测试、Bandgap trim测试、BIST测试、存储器测试、I2C烧写code测试等。

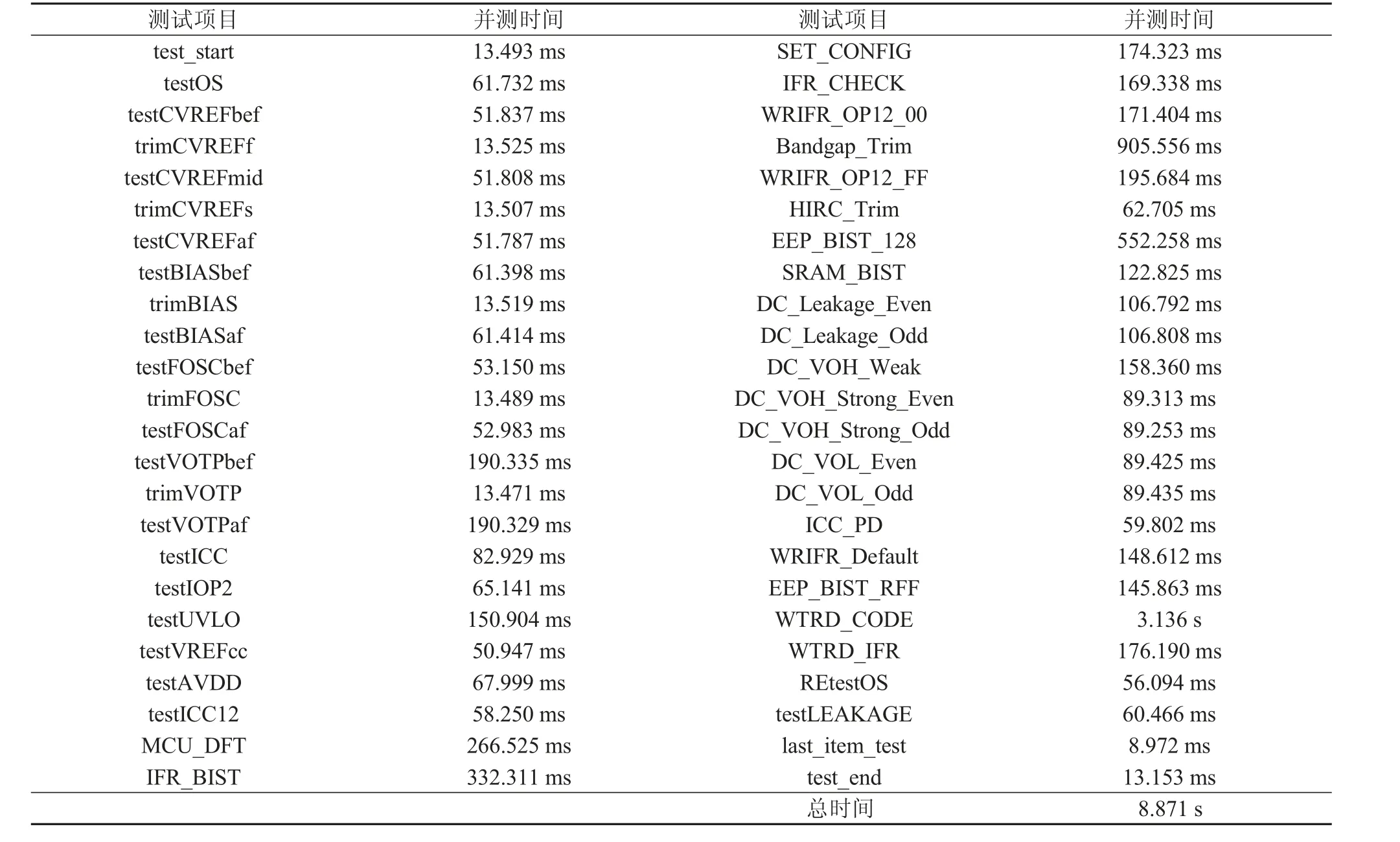

4.4 测试结果

该快充协议芯片测试结果如表3所示,结果显示该方案实现了对该快充电源模块主要性能参数的测试,双site并测时间约8.8 s,满足了该芯片晶圆的量产要求。

表3 测试结果

5 结论

本文提供了一种基于Chroma 3380P的快充协议芯片测试方案,该方案实现了对快充芯片晶圆常规数字参数与模拟参数的测试,双site测试方案在现有的资源下实现高效量产,晶圆封装后FT(Final Test)测试良率等正常,可作为快充芯片测试开发参考。