高集成度射频收发器的差分正交调制解调测试与工程实现

2022-03-30王志强

王志强,丁 丹

(航天工程大学 电子与光学工程系,北京 101416)

0 引言

ADI公司的AD9361集成射频捷变收发器,具有很强的可编程性和宽带能力[1],器件集RF前端与灵活的混合信号基带部分为一体,集成频率合成器,为处理器提供可配置数字接口。AD9361芯片工作频率可达70 MHz~6 GHz,通道带宽可以达到200 kHz至56 MHz,同时支持外部控制,功能强大,因此在3G,4G基站有着广泛应用。文献[2]在自回环测试AD9361功能时只是观察接收端信号的频率,但未考虑到系统时钟误差对接收、发射本振的时域波形带来的影响。文献[3]基于AD9361实现QPSK调制解调,并未考虑到AD9361接收与发射本振的精度。

本文将从工程实现角度出发,发现并解决4个工程问题:1)发现AD-FMCOMMS2输出端在输出70 MHz正弦波时,同时发现100 MHz,150 MHz正弦波谐波分量都非常严重,分析其原因是由于子板的的输出端的输出巴伦匹配频率为2.4 GHz,导致相比较于2.4 GHz低的频率输出谐波分量严重,将输出端的频率设置为1.4 GHz谐波分量将得到抑制;2) AD9361如果系统时钟设置与真实系统时钟频率有误差将会导致发射与接收本振的时域波形扭曲,因此系统时钟应将默认的38.7 MHz修改为40 MHz;3)分析DCXO的频率精度导致的频差大小将不会导致点积叉积解调系统的解调[4];4)分析AD9361接收与发射本振的随机相位差导致接收端的星座图偏移。

1 AD9361配置

AD9361通过一个串行外设接口SPI与FPGA开发板实现通信。该接口可以配置为4线接口,带有专门的接收和发射端口,也可以配置为3线接口,带一个双向数据通信端口。该总线允许BBP通过一种简单地址数据串行总线协议,设置所有器件控制参数。

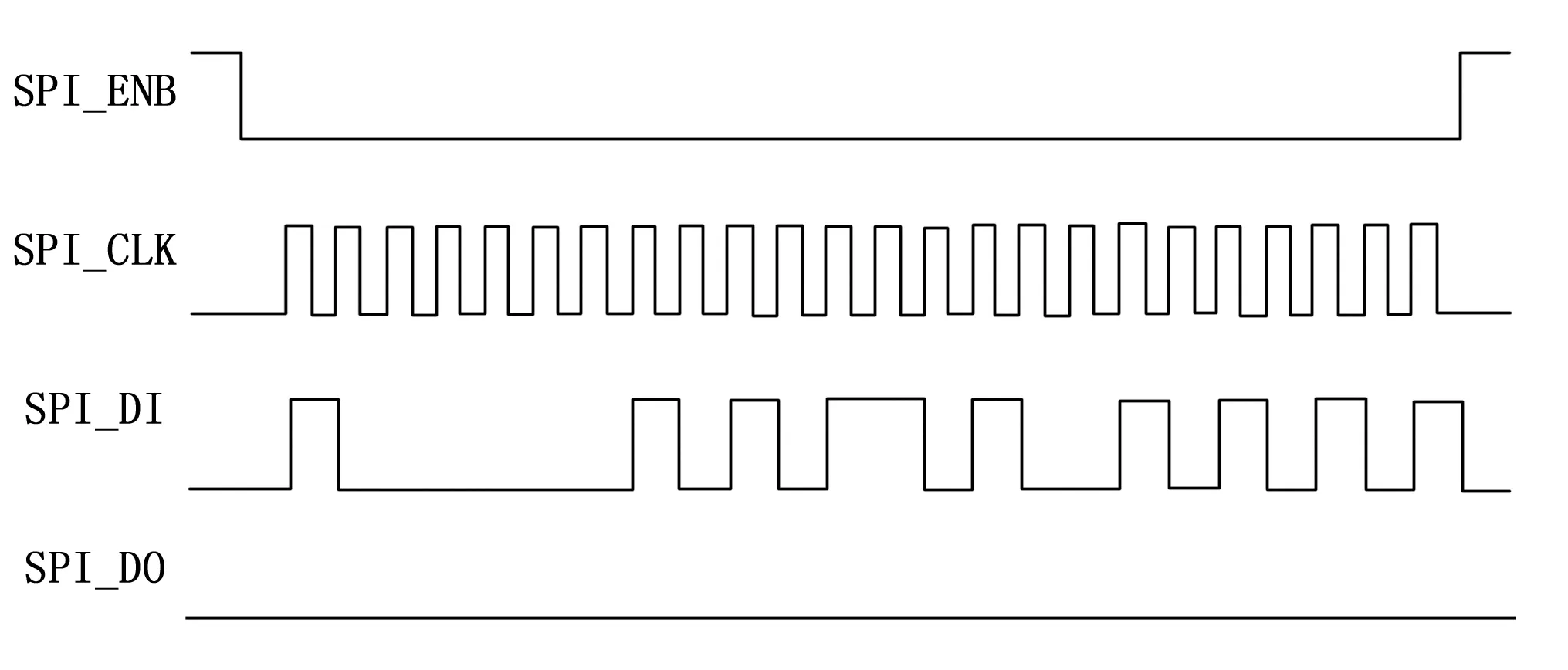

AD9361中SPI接口的写命令遵循24位格式。前6位用于设置总线方向和需要传输的字节数。接下来的10位数据的写入地址。最后8位是将被传输至指定寄存器地址(MSB至LSB)的数据。AD9361还支持LSB优先格式,允许命令以LSB至MSB格式写入。在该模式下,对于多字节写命令,寄存器地址将递增。SPI写时序如图1所示。

图1 SPI时序图

读命令遵循相似的格式,区别在于,前16位在SPI_DI引脚上传输,最后8位从AD9361中读取,如果是4线模式,则在SPI_DO引脚上完成,如果是3线模式,则在 SPI_DI 引脚上完成。这里我们使用默认的 4 线接口模式。

测试SPI接口功能,首先找到AD9361内部可读可写的寄存器位0x3DF,将配置文件载入开发板并与ad9361连接,通过signaltap采样内部开发板管脚,先对寄存器0x3DF进行写入,写入的数据为0x88,再读出寄存器0x3DF的值,再观察sdo管脚,观察SPI_CSN高电平前八位的值对应位寄存器0x3DF的读出值为0x88。

2 AD9361测试验证

2.1 正弦信号自发自收验证

设置AD9361发送端的本振为1.4 GHz,发送带宽为5 MHz,发送端的采样速率为8 MHz,IQ两路发送全“1”,因此发送端将会发送一个1.4 GHz的正弦信号。接收端设置本振为1.399 GHz,接收端的带宽为5 MHz,接收端的采样频率为8 MHz,自回环将发送端的信号接收回来,经过混频,带通滤波器,AD变换后,因此接收端将会得到0.1 MHz的正弦信号,将接收端的IQ两路信号用signaltpa采样保存后用Matlab分析结果如图2所示。

图2 0.1 MHz Matlab分析结果

对接收结果的频率进行验证,signaltap采样时钟设置为125 MHz,因此图中Matlab两个点之间的时间为T0=1/125 000K(s)从图中看出一个正弦时钟周期大约有M=1 250个点,从而得出该时钟的频率F为:

验证此次测试的结果。

2.2 DQPSK自发自收验证

AD9361实现DQPSK,首先基带信号处理的实现由FPGA来完成,设前一时刻发送的相位为π/4,意味着前一时刻FPGA发送给IQ两路数据分别为+1,+1。若此时输入的符号为10,此时刻相位变化π/2,此时刻发送的相位应该为3π/4,对应IQ两路数据应该为-1,+1,前一时刻共4种相位,发送的数据位两位二进制,差分调制发送端共16种情况。设置AD9361的发送端采样速率为8 MHz,为了保证采样的正确性,设置为符号速率为1 MHz,这样每个符号AD9361都会采样八次。FPGA实现框图见图3。发送端的发带宽设置为8 MHz。发送端频率设置为1.4 GHz载频。发送端将得到,中频频率为1.4 GHz,带宽为4 MHz的DQPSK信号。

图3 DQPSK调制FPGA实现框图

DQPSK的解调若采用经典的相干解调法,对于接收端与发射端的频率误差与相位误差的精度要求很高,然而对于AD9361而言首先发送端与接收端的本振是由两个不同的锁相环产生的,两个不同的锁相环很难产生相同的频率,同时两本振之间还存在随机的相位差,采用相干解调法很难实现。针对本系统而言,采用点积叉积方法对DQPSK进行解调,收发本振的偏差对采用点积叉积方法影响几乎可以忽略。与此同时,DQPSK相比较于QPSK而言,发送的信息为前后相差的,抵消了接收与发射本振的相位差随机的影响,但使用点积叉积的方法前提条件为接收与发射本振的频差不会导致对最终的判断结果错误。与发送端的频率设置相同,接收端的采样时钟设置为8 MHz,因此每8个点表示单个符号,具体的FPGA处理如图4所示。

图4 点积叉积解调FPGA实现框图

接收端设置为与发送端的采样速率相同的采样速率,即:采样速率设置为8 MHz通道带宽设置为5 MHz,用Matlab进行分析结果如图5所示。

图5 输出输入对比波形结果

从波形图结果可以看出发送端与接收端的解调结果相一致。

3 工程实现问题及解决

3.1 AD9361锁相环的校准问题及解决

在实现AD9361对于正弦信号的自发自收过程中,先根据AD9361的配置软件AD9361 Evaluation Software产生的配置脚本对AD9361进行初始化,其中脚本中大部分为SPI Write指令,还有部分SPI Read指令,例如SPIRead 05E // Check BBPLL locked status (0x05E[7]=1 is locked)即:只有当寄存器05E第八位读出的结果为1时,初始化才能继续进行。还有一类指令例如WAIT_CALDONE RXCP,100 // Wait for CP cal to complete, Max RXCP Cal time: 460.800(μs)(Done when 0x244[7]=1)此行脚本表示为读取寄存器244的第八位,直到第八位的值为1表示rxcpcal校准成功,同时又具有最大校准时间460(μs),若超过校准时间寄存器244的第八位的值仍为0,初始化继续往下进行。

1)问题描述:AD-FMCOMMS2子板的输入参考时钟为dcxo输入,如果根据配置软件默认设置refclk path为extclk into xtal_n路径,按此方式进行初始化,结果显示初始化未成功。初始化进行到spi接口读出的05E寄存器的bit[7]为0,此结果表明bbpll频率合成器一直不能锁定。

问题原因及解决方式:由于AD-FMCOMMS2的系统时钟输入未DCXO输入,如果配置为内部时钟输入,导致锁相环无时钟源,不能锁定。将AD9361系统时钟输入方式改为xo into xtal_n[5],SPI接口读出05E寄存器的bit[7]为1,判断bbpll频率合成器校准成功。

2)问题描述:为保证ad9361初始化效果,SPI接口时钟频率不宜过高,一般选用10 M及10 M以下的时钟,因此工程中采用10 M的时钟频率。同时,每一次写入寄存器值都要等待2 ms保证校准效果,如果时钟过高,或者写入的太快,将会导致rxcp校准出现问题,初始化不能继续进行。将初始化spi时钟设置为40 MHz,每一个写入寄存器的间隔不设置的结果。按照配置软件产生的配置脚本,寄存器已经配置结束,状态机也处于fdd状态,但频谱仪上没有信号,说明初始化校准不理想。

原因及解决方式:AD9361系统配置时钟应设置为40 MHz以下,保证写入每个寄存器质量。因此将SPI时钟设置为10 MHz,同时按照脚本上的每一写时序之间相隔2 ms写入,初始化可以继续进行。

3)问题描述:按照配置软件产生的脚本进行对AD9361的配置后,iq两路发送全1,发送本振设置为150 MHz,通道衰减[6]设置为0 dB,使用发射通道2即:TX2A使用示波器并未观测到信号。

问题原因:这是由于按照配置软件产生的脚本进行初始化后,AD9361状态机仍工作在alert[7]状态,此状态下对于全双工工作模式AD9361并不能发射与接收信号,所以还需要将状态机转换到fdd工作态。根据spi接口读取到的ad9361内部寄存器014的状态值为01h根据ad9361数据手册,当读取014寄存器的值为01h时表示状态机仍处于altert状态,验证了上述说法。

解决方式:对寄存器014写入值023即;将AD9361状态机转换到fdd状态下,示波器接收到的结果如图6所示,图中为70 M正弦波的接收结果[8]。

图6 频谱仪接收结果

3.2 AD-FMCOMMS2输出匹配频率问题及解决

问题描述及原因:根据图6观察频发现70 MHz的信号谐波分量分量严重。这是由于AD-FMCOMMS2发射与接收端的巴伦匹配频率在2.4 GHz,如果输出端输出的频率过小将会导致谐波分量很高。AD-FMCOMMS2接收端的巴伦[9]如图7所示。

图7 接收端巴伦

解决方式:针对输出端匹配频率为2.4 GHz的输出巴伦,如果采用过小的输出频率将会导致输出端的奇次谐波分量严重,因此提高输出端的匹配频率为1.2 GHz,使输出巴伦抑制谐波分量。

3.3 AD-FMCOMMS2系统时钟问题及解决

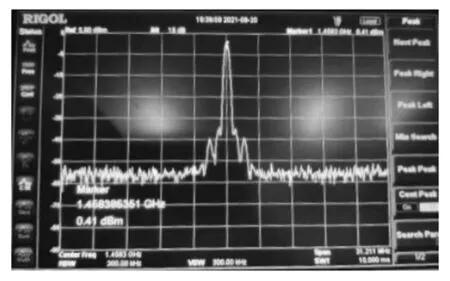

1)问题描述及原因:AD-FMCOMMS2的输入参考时钟为40Mdcxo输入,如果系统参考时钟频率为配置软件软件的默认频率即38.7 MHz将会导致发送端的锁相环存在频偏[10],如果参考时钟设置为40 MHz将会大大降低频偏。效果如图8所示。

图8 参考时钟为默认38.7

按照默认设置的dcxo频率计算,即RFPLL需要将38.4 M的时钟倍频到1 400 M,则倍频倍数M为:

M=FLO÷Fref=1400÷38.4=36.4583

实际上dcxo的频率对于AD-FMCOMMS2而言为40 MHz[11],因此实际值与设置值存在Fdif1.6 MHz的偏差,所以接收端的频差为:

Fincrease=M×Ddif=1.6×36.458=58.3328

验证了存在58.3 MHz的频差。修改方式:将参考时钟频率修改为设置为40 MHz,用频谱仪观测1.4 GHz信号,得到的结果,结果表明修改系统时钟频率后的输出端频率误差很小。

解决方式:参考时钟设置为40 MHz发送端本振设置为1.4 GHz,接收端本振设置1.399 9 GHz,混频滤波后,接收端将会得到0.1 MHz正弦信号,如图9所示。发送带宽与接收带宽都设置为5 MHz将接收到的信号用Signaltap采样,用Matlab分析采样得到的数据结果如下。

图9 0.1 MHz接收正弦信号

2)问题描述:图中signaltap的采样结果存在波形扭曲问题,经过对比分析得出,是由于ad9361时钟源的影响,图上的结果是采样默认时钟源频率38.7 MHz,得到的iq两路信号波形扭曲,而AD-FMCOMMS2的输入参考时钟为40 MHz的dcxo输入,若采用38.7 MHz系统时钟输入将导致输入输出端的锁相环锁定不理想。进而导致了输入输出本振波形的扭曲,因此混频后的波形会扭曲。

解决方式:对配置软件的dcxo的频率修改为40 MHz,得到的新的0.1 MHz频差修改系统参考时钟后的AD9361输出端的波形扭曲问题得到很好的改善[12]。

3.4 AD9361的随即相位差与频差对解调影响

若接收端的采样速率设置为8 MHz,用Matlab进行分析解调时,接收端A/D采样后,FPGA内部I/Q两路数据波形图及星座如图10所示。

图10 星座图

图10显示的接收端星座图为π/2 DQPSK解调出来的结果[13],实际本系统采用的是π/4 DQPSK调制的方式。产生这种现象的原因是由于发射与接收本振的相位差随机性导致的,接收与发射的本振是由相同的系统时钟REF_CLK分别经rxpll,txpll倍频后得来的,在不同的上电时刻对于rxpll,txpll倍频后的接收与发射本振的相位不同[14],导致AD9361的接收端存在不同的相位差。这种随机相位差对解调端不会产生影响,理论分析如下:假设发送端的信号为cos(w0t+θ0)其中θ0为:π/4,3π/4,5π/4,7π/4。以i支路接收端为例,设i支路接收端的本振为cos(wct+θ1)其中θ1为ad9361的发射本振与接收端本振的相位差。对其进行混频结果如下:

cos(w0t+θ0)*cos(wct+θ1)=

cos((wc-w0)t+θ1-θ0)]

经过低通滤波器以后为:

分析频差对星座图影响:除接收信号本身相位变化外,频差将会导致前后两时刻接收信号的相位变化,使得星座图上的点存在发散情况。对于相位差将会导致星座图的整体偏移,例如本次接收结果,发送发送的信号为π/4 dqpsk信号,对于接收端接收到的星座图而言为π/2 dqpsk信号,由于接收端与发送端的本振的行为差导致的[15-16]。

解决方式:为解决发送端与接收端本振的相位差随机性,采用DQPSK的调制方式,这样发送与接收端只需要前后两次信息的相位差信息而不需要具体的相位信息,很好地解决了相位差随机的问题。同时接收与发射端的本振还存在着频差,因此采用点积叉积的方法对接收端进行解调,采用点积叉积的方法前提条件为接收与发射本振的频差不会导致判断的结果的错误。判断分析能否采用点积叉积方法解调,AD9361接收与发射的频差是否在点积叉积频差允许范围内,首先dcxo[17-18]的频率精度是由其电容控制的,电容精度将会导致系统时钟为40 MHz频率偏差范围为0.000 72 MHz,对其进行倍频,因此对于1.4 GHz的本振将会导致0.025 2 MHz频偏,采样频率为8 MHz,根据模拟频率与数字角频率的转换,频差的结果小于四分之pi。因此不会对点积叉积方法进行解调产生影响。

4 结束语

本文针对AD9361芯片测试其自发自收并验证DQPSK。此过程中发现并解决4个疑难问题:1)在对AD9361初始化过程中,由于系统时钟输入方式的设置错误将导致芯片中的锁相环不能锁定或锁定效果不理想,修改系统时钟输入方式后,内部锁相环可以锁定;2)初始化结束后输出端谐波分量严重,这是由于输出端的输出巴伦匹配频率为2.4 GHz[19],因此若输出时钟频率设置的过小输出巴伦不能抑制谐波分量,修改输出端的频率为1 GHz以上,谐波分量将很好的抑制;3)AD-FMCOMMS2系统时钟并非是AD9361配置软件默认的38.7 MHz,若采用此频率配置后,导致AD9361内部锁相环锁定不理想表现为AD9361输出端将会存在频差与波形扭曲,修改系统时钟为40 MHzdcxo[20]输入,解决了输出端频差与波形扭曲;4)进行DQPSK解调过程中发现接收端与发射端存在频差与相位差,同时相位差具有随机性。采用点积叉积的方法进行解调将很好地解决收发本振的频率差问题,但是采用这种方法解调频率差在一定范围内,若果过高将导致解调出错。针对相位差随机性问题,本工程采用的是差分正交调制,发送的信息为前后两次相位差,很好的抵消本振相位差带来的影响。