三维集成技术在红外探测器中的应用

2022-03-18喻松林

谭 振,聂 媛,于 艳,田 震,喻松林

(华北光电技术研究所,北京 100015)

1 引 言

在半导体和微电子领域,垂直堆叠集成电路的趋势已成为满足诸如高性能、多功能、低功耗、小型化电子设备要求的可行的解决方案,实现此目的的各种方法和过程称为三维集成技术(3D integration)。通常,三维集成是一个广义术语,其技术可分为三维晶圆级封装、基于三维中介层(interposer)的集成、三维堆叠式集成电路(3D stacked IC,3D-SIC)、单片三维集成电路、三维异构集成等。

三维晶圆级封装的操作对象是晶圆,它通过采用重分布层(Redistribute layers,RDL)和凸点工艺(bumping process)来形成互连;基于中介层的三维封装其特点是芯片被贴装在中介层(中介层的材料可以是硅、玻璃或者有机材料)的两端,通过硅通孔(Through Silicon Vias,TSVs)实现电学连接;三维堆叠集成电路是通过TSV将集成电路(Integrate Circuit)之间进行互连;单片三维集成电路是利用代工厂的工艺,在单个芯片上堆叠多器件层,在这个过程中,非常精细的TSV并不是其实现电学互连的必选手段;三维异构集成是指基于不同半导体材料体系,进行单片级(如异质外延集成)或者晶圆级集成,如将氮化镓高电子迁移率晶体管(High electron mobility transistor,HEMT)器件、磷化铟异质结双极晶体管(Hetero junction bipolar transistor,HBT)和硅MEMS器件封装在CMOS晶圆上。

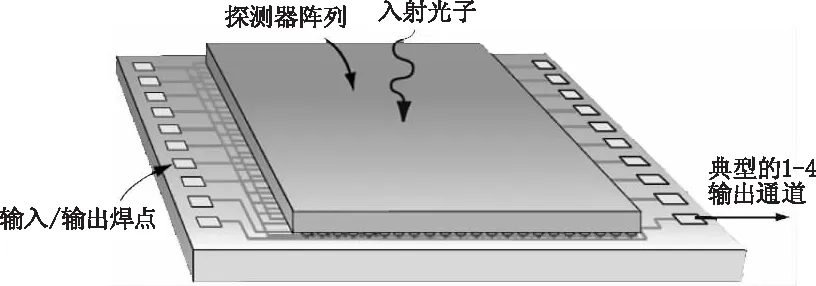

红外焦平面探测器是一种可处理大量并行信号的器件,在一帧周期内,焦平面阵列上的每个像元都在处理入射到探测器上的光子信号。对于像元数量巨大的大规格焦平面阵列,所有像元同时工作的这种机制只能通过在像元级将光电二极管和读出电路进行垂直互连来实现。图1展示了最简单的垂直集成,即焦平面阵列堆叠在单片硅电路之上,这也是传统的红外焦平面探测器互连形式。

图1 传统的红外探测器结构示意图

在很长的一段时间内,传统红外焦平面探测器的发展都是以光电二极管阵列的发展为主线,但是随着红外焦平面探测器技术发展,读出电路的发展也逐渐凸显出其重要作用。趋势之一是探测器像元尺寸的减小,这意味着在同样的焦平面规格下可以获得更多的场景内容;趋势之二是在像元内增加信号处理能力,这使得全数字化焦平面成为可能。在此趋势下,红外探测器将向着小体积、重量、功耗;高可靠性、高稳定性的集成化智能化系统发展。

然而,这两个趋势的发展对读出电路设计提出了难题:在更小的像元面积内集成更多的电路功能。克服这个难题的措施之一就是采用更先进的CMOS设计节点,但是研究发现,超过28 nm后,先进设计技术的成本优势开始下降[1]。因此,研究人员开始转向三维读出电路(3D ROIC)的研发。

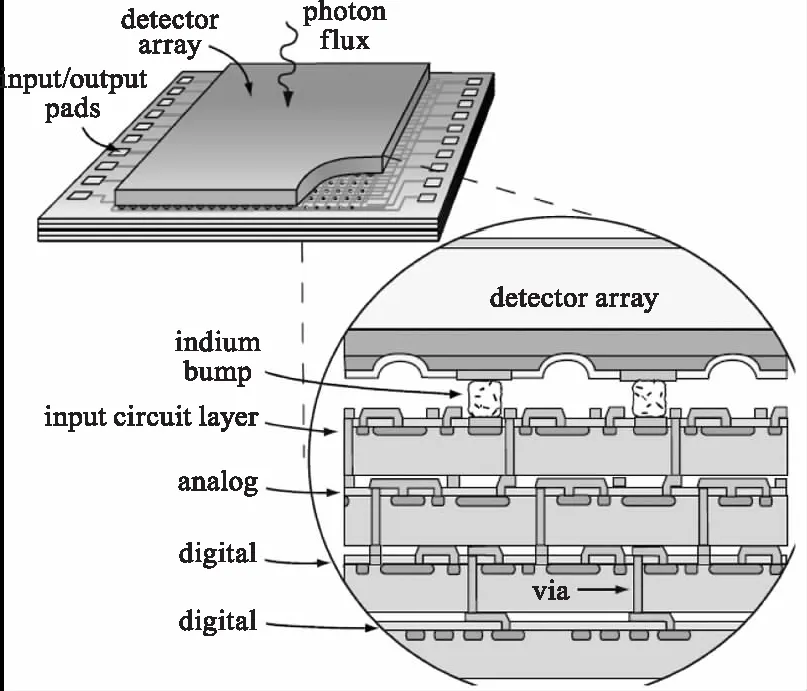

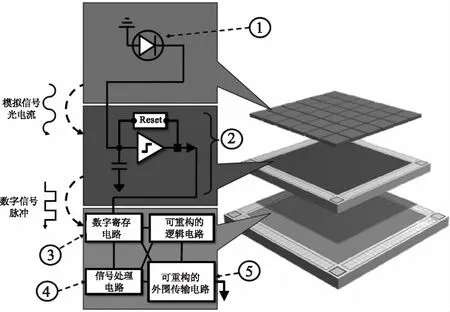

传统的二维电路结构限制了像元级电路功能,三维电路集成显示出了其不受像元尺寸限制的优越性。积分电容作为读出电路中的关键参数之一,不再支配电路可用面积,这就允许在像元级额外增加信号处理功能,比如片上A/D转换、数据压缩、原位信号处理等功能[2]。同时,三维集成电路将允许在相互独立的层内布局模拟电路和数字电路,如图2示意,这就可以充分利用模拟和数字电路各自的最佳设计规则和工艺技术,从而降低噪声、功耗并且提高产出率。

图2 三维垂直集成示意图

美国 DARPA(Defence Advanced Research Project Agency)在2001年就提出了VISA(Vertical Integrate Sensor Array)项目研究,旨在提高光电探测器性能,拓展光电探测器功能。参与该项目的研究结构包括DRS Infrared Technology、MCNC、Rockwell Scientific、Raytheon Vision Systems、University of NY at Albany以及Lincoln Laboratory。项目分两个阶段,第一个阶段是研究通孔互连方法的可行性,同时研究大动态范围的A/D电路;第二个阶段是将通孔互连技术和电路技术进行集成,从而获得基于垂直集成技术的高性能传感器[3]。

从DARPA提出上述研究计划,至今已近20年,本文对上述研究机构的公开报道的相关研究结果进行了总结,同时探讨了三维集成技术在红外探测器研制中面临的挑战及发展趋势。

2 红外焦平面探测器中的三维集成工艺

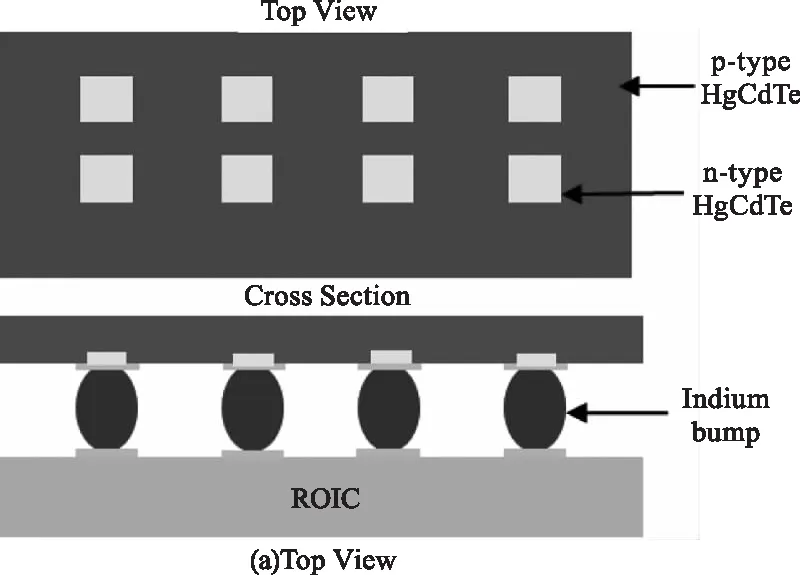

红外焦平面探测器芯片由光电二极管阵列和读出电路芯片互连形成。根据互连形式可以分为两种,其一是采用In柱的互连结构,该结构是国内外绝大多数研究机构的技术方案(图3(a));其二是采用通孔的互连结构(图3(b)),是美国DRS公司独有的技术方案,称之为HDVIP(High Density Vertical Integrated Photodetector)[4],本质上也是垂直集成技术的应用,得益于光电二极管的特殊结构,DRS公司在红外探测器三维垂直集成技术方面的研究一直处于行业领先水平。

图3 In柱互连和通孔互连结构的红外探测器示意图

综上所述,红外探测器中的三维集成可以分为读出电路的三维集成以及探测器的三维集成,由于摒弃了In柱互连,后者集成度更高。但是无论哪一种集成结构,采用通孔互连都是必备的技术途径。

TSV是三维集成电路的一种主流技术。它是一种系统级架构的新方法,内部含有多个平面器件层的叠层,并经由TSV以垂直短线方式取代传统的芯片互连线方法,无需外部引线键合。采用TSV技术集成相同类型的红外探测器信号处理电路,可以提高单位面积/体积上的电容值或者功能模块,因此能够显著提升红外探测器的电荷处理能力或者增加电路功能,并且可减少信号传输的延迟并能增加带宽。采用TSV技术集成不同类型的红外探测器信号处理电路,如将信号处理、图像处理和数据存储等芯片集成,可以降低红外系统体积重量和功耗,提高系统集成度。

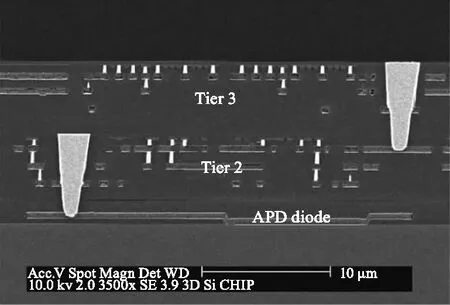

美国MIT林肯实验室,将绝缘物上硅(Silicon On Insulator,SOI)晶圆作为转移晶圆,每两层芯片通过低温氧化物-氧化物键合后,将SOI晶圆处理掉,在顶层芯片上干法刻蚀出直径1.5 μm的TSV,进行标准的通孔填充,实现与下面相邻层芯片的连通。重复该过程,完成了两个CMOS电路与一个雪崩光电探测器(Avalanche Photo Detector,APD)芯片的三维集成,其工艺过程如图4所示。

图4 MIT林肯实验室3D集成工艺步骤

由于采用了SOI技术,不仅可以降低Si衬底上的寄生电容,降低功耗,提高运行速度,同时,在多层电路通孔互连时,通孔之间是绝缘的,每个通孔可以直接进行金属沉积,简化了工艺。

美国DRS公司的三维集成工艺过程如图5所示。在模拟电路上进行深硅刻蚀、深孔钝化层沉积,形成键合对准标记,接下来,采用机械研磨、化学机械抛光等工艺将模拟电路减薄到30 μm左右,露出键合标记;在数字电路上进行金属沉积、TSV焊盘成型等工艺。之后,将两个电路芯片对准键合,接着制备TSV,然后沉积金属,经光刻刻蚀成型,完成模拟电路数字电路的连接。碲镉汞红外探测器与两层电路的键合,DRS依旧采用其传统的HDVIP工艺,采用三维集成工艺后,DRS科研人员验证了该结构可以承受2000余次温度冲击(室温到77 K温差)[5]。图6为扫描电镜下3D读出电路和红外探测器剖面图。

图5 DRS公司模拟电路和数字电路的三维集成示意图

图6 扫描电镜下3D读出电路和红外探测器剖面图

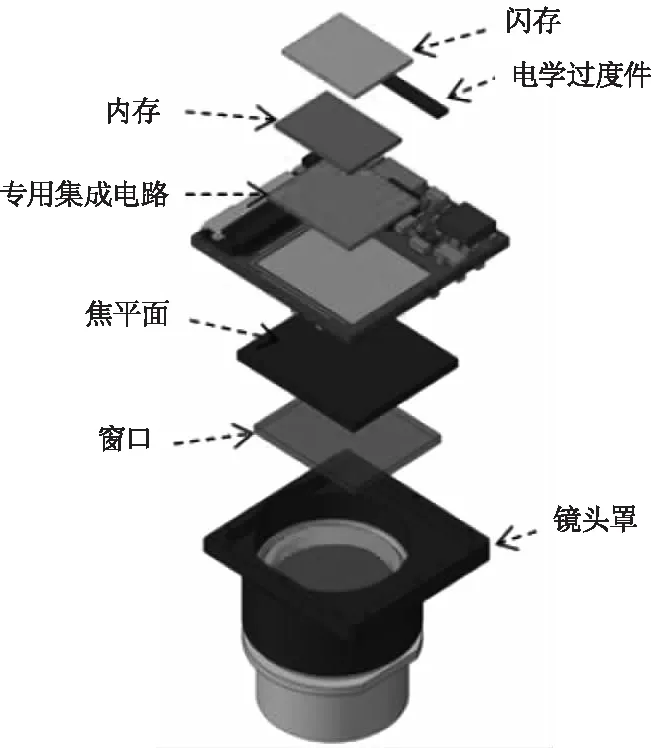

英国BAE公司提出的解决方案是基于中介层的(3D interposer)的三维垂直集成,研发人员利用双面电路板卡(Double Sided Circuit Card Assembly)作为中介层,图像传感器在电路板的一侧对辐射进行响应,产生的信号在电路板的另一侧由专用集成电路、内存进行处理和存储。

内存和闪存芯片被减薄到330 μm,然后贴装到专用集成电路上,并且通过引线键合连接;接下来,集成电路、内存和闪存被粘接到中介层的一面,焦平面阵列器件粘接到中介层的另一面,各个分立器件之间通过引线进行键合,从而完成多种器件的三维集成,如图7所示。

图7 SMART芯片双面电路板集成的实物图

3 三维集成红外探测器芯片的应用

随着光电系统应用需求的牵引,红外探测器正在向着缩小体积、重量和功耗,同时提高功能集成度的方向发展。如,针对远距离、复杂背景下探测应用,需提高红外探测器阵列规格、缩小像元尺寸,从而形成高分辨率识别能力,同时还需提高红外探测器灵敏度、帧频及动态范围,以实现在复杂背景下快速、准确的探测并跟踪目标;针对激光雷达应用,要求探测器读出电路具备高精度信号捕捉能力以进行目标测距,同时还须具备传统读出电路视频信号处理能力;在无人机、单兵手持热像仪等应用中,为了降低红外系统的体积重量和功耗,探测器芯片和外围图像处理芯片要尽可能集成在一起,单片读出电路已经难以实现系统要求的诸多功能。采用三维集成技术实现多电路集成,可突破传统单片读出电路对红外系统性能和功能的限制,提高系统极限性能、扩展系统功能并且提高其集成度,满足对远距离弱小目标探测、高精度激光雷达成像等需求。针对以上应用,国外已经开展了相关研究。

3.1 主/被动成像探测器

主/被动成像探测是随着光电对抗、光电隐身的发展而出现的新型成像探测技术,它可以将大范围被动成像侦查与小范围主动成像跟踪结合起来,同时获得目标距离像、强度像、距离-角度像等多种信息,可以广泛用于天文观察、卫星跟踪、洲际导弹预警、激光武器以及常规防空武器预警等领域[6]。

采用同一焦平面和同一光学系统,通过改变读出电路的工作模式,可以使其在主动和被动模式之间切换,适应主被动成像探测双模需求。由于主动、被动两种工作模式下,读出电路发挥的功能不同,其电路设计也存在很大差异,无法在单片电路上实现。因此,三维集成电路成为切实可行的解决方案。

2006年,美国的MIT林肯实验室,开发了基于全耗尽SOI CMOS的制造工艺和技术,通过堆叠SOI晶圆上制造的电路来形成三维集成电路,依靠微米尺度通孔来互连多层电路结构。他们研制出了三层集成的64×64、 50 μm像元间距的激光雷达成像芯片,用于三维互连的通孔直径为1.5 μm,每个像元上有6个TSVs。第一层是30 V工作的盖革模式APD阵列;第二层是基于3.3 V、 0.35 μm SOI工艺制备的电路,用于APD施加偏压,在APD雪崩时产生停止信号;第三层是基于1.5 V、 0.18 μm SOI工艺制备的电路,是计时电路[7]。具体结构如图8所示。

图8 3D-LADAR的通孔扫描电镜图以及电路构成图

测试结果表明3D-LADAR芯片的时间分辨率达到2 ns。该芯片是第一个包含有源电路和器件的三层结构芯片,第一次验证了三种不同工艺集成在一个三维芯片上的可行性[8]。

3.2 高性能红外探测器

红外焦平面探测器的读出电路方式多采用模拟电路,其中电容部分占据了大部分的像素面积。通过三维集成技术,可以在像素单元上增加积分电容的面积,在长波波段,可以将NETD提升接近一个量级,中波波段也有小幅度提升;由于增加了积分电容面积,场景动态范围可以提升到120 dB。这将允许同时探测高温目标和常温背景。ROIC将具备更多功能,更加智能化,例如校正、盲元替代、帧平均等都可以在片上完成。

美国DRS公司D.S.Temple等人报道了采用高密度3D集成制备红外探测器工作。基于标准CMOS技术设计了模拟和数字两款电路,在不同的工厂完成流片之后,两片电路通过256×256阵列的TSV连接,直径4 μm,深度30 μm,像元间距为30 μm。经测试,3D互连的连通率超过99.9 %[5]。三维集成碲镉汞红外探测器的结构如图9所示。

图9 三维集成碲镉汞红外焦平面探测器扫描电镜图

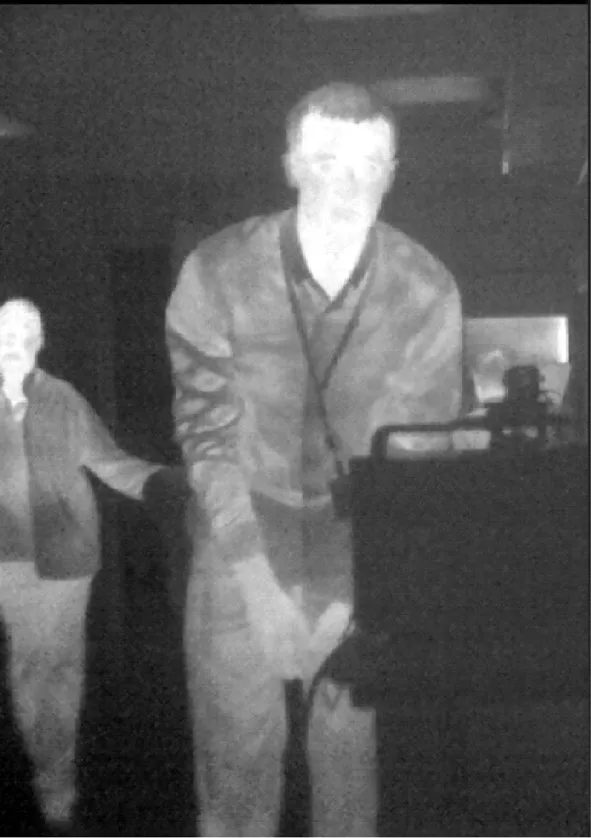

与中波HgCdTe焦平面阵列互连后(HgCdTe的膜厚为7 μm),测试了探测器噪声等效光通量(Noise Equivalent Flux,NEΔΦ),其直方图如图10,整体呈高斯分布,表明集成后无明显的过剩噪声机制引入,有效像元率为97.5 %,大部分盲元来源于接触孔开孔工艺,而不是3D电路集成工艺。研究人员利用该器件进行了热成像演示,如图11所示,三维集成过程没有引入盲元簇,也没有明显的串音,证明了三维集成结构可以将光子信号较好的从像元传输到底层电路,并且没有引入明显的噪声。

图10 三维集成中波红外探测器噪声等效光通量测试图

图11 三维集成中波红外探测器热成像图

中国电科11所正在开展三维集成长波碲镉汞红外探测器研究。将模拟电路与数字电路分开,基于后穿孔(TSV-last)工艺,将两层及以上的处理电路进行集成,可以有效降低模拟信号噪声,提高单位像素上积分电容面积。目前在研三维集成长波碲镉汞红外探测器阵列规格为640×512,像元间距为25 μm,响应波段8~10 μm,具备18 bits的数字信号处理能力,动态范围能够达到100 dB,NETD达到3 mK。该技术突破后,将为更小间距更大阵列规格的高性能长波碲镉汞红外探测器奠定良好基础。

3.3 片上相机

通过三维集成技术,可以将传统的热像仪大多数后端信号处理电路集成到读出电路一端,从而缩小热像仪的体积重量和功耗,实现片上相机(Camera-on-Chip)。

2015年,美国BAE公司在DARPA支持下开展了低成本热像仪(Low Cost Thermal Imager,LCTI-M)项目研究,提出了SMART(Stacked Modular Architecture High-Resolution Thermal)片上相机,基于12 μm中心距的长波640×480非制冷红外探测器,采用多电路集成、光学集成的方案,实现了体积2.9 cm3,探测器重量5.1 g的片上相机,其帧频可达60 Hz,功耗不到500 mW[9]。图12是片上相机的结构模型图,图13是片上相机集成到手机上的成像图。

图12 BAE公司片上相机的概念图

图13 片上相机在手机上的成像

3.4 可重构成像

当下探测成像系统只能执行单一或有限的光信息探测,如强度和偏振探测,这是由于探测器读出电路是针对特定探测器、特定模式和特定任务设计的,只对感兴趣的信号进行采样传输和处理,本质上是专用集成电路(Application Specific Integrated Circuit,ASIC)。如果在强度探测的基础上增加对目标相位、偏振、距离、光谱等信息的探测,能显著提高对目标的探测和识别能力,这是未来光电探测器的发展方向之一。

2016年9月,DARPA启动了可重构成像(Reconfigurable Imaging,ReImagine)项目,目的是创建一种类似现场可编程门阵列(Field Programmable Gated Array,FPGA)的结构,结合理论和算法的开发,当探测器具备对多种光信息的感知能力时,使探测器学会收集最具价值的信息。ReImagine项目的目标是阐明单一的,可重构的读出电路结构能够适应多模式成像任务。比如,以不同的空间或时间分辨率进行探测,以同帧或异步模式工作,对主动飞行时间进行采集等。

在该项目中,三维集成技术成为像素级自适应读出电路的实现手段。模拟信号和数字信号处理电路从物理上实现了隔离,分布在上下两层。上层为模拟电路,专注光电信号的转换;下层为数字电路,基于像素级前端电路的设计,可由用户了灵活配置工作模式。图14是可重构成像探测器芯片的结构示意图。

图14 可重构成像探测器芯片结构示意图

该项目由DRS、BAE、LockHeed Martin、Voxtel公司承担,目前已经验证了二维成像雷达系统(LIDAR)在成帧(framing)或者异步(asynchronous)模式下可以获得3D图像。也验证了直接探测和同步接收阵列,在不同应用下具有明显的优势。

4 三维垂直集成技术应用于红外探测器芯片面临的挑战

目前,三维集成技术在制冷型红外探测器中已经获得了初步验证,不少研究机构均完成了各自的集成工艺开发,集成过程的主要难点包括:

集成方式:减薄、表面金属沉积、对准标记等工艺可以晶圆级操作,提高效率;多层电路集成时,采用芯片级集成,可以提前选定合格芯片,避免晶圆集成时带来的良品率降低问题。但是,对于芯片级集成,引入了更多的手工操作,因此颗粒污染等控制难度增加。

电路减薄:晶圆级减薄,要对晶圆边缘进行研磨,避免减薄过程中裂片;对减薄过程以及减薄后硅的厚度进行测试,保证晶圆级厚度可控;减薄后芯片厚度很小,易出现弯曲和变形。综上,在减薄电路芯片操控上需开发对应的工艺。

电路键合:考虑到键合精度影响TSV的对准,因此要求键合精度微米量级,像元越小,要求越高,对于30 μm间距的器件,对准精度要保持在3 μm以内[8]。对于工作在低温环境的红外探测器,还要求键合具备良好的可靠性,因此,需考虑电路之间的键合强度、键合应力,这对键合材质提出了较高要求。

TSV制备:硅基电路上的TSV工艺相对成熟,但是对于工作在低温环境的红外探测器,在TSV制备中,应当考虑大量TSVs中金属引入的应力。集成密度增加意味着像元间距缩小,最小像元间距受到TSV对准精度和全局金属焊盘宽度的综合影响。

5 结 论

本文对红外探测器中的三维集成技术进行了总结介绍,国外研究机构开发了各自适用的三维集成工艺,已经完成了主被动成像探测、高性能红外探测器、片上相机等原理样品的研制,相关测试结果表明,三维集成技术在提高红外探测器极限性能、提升功能集成度方面可发挥重要作用,突破该技术将有助于缩小红外探测器系统体积重量和功耗,提升红外探测器系统灵敏度、动态范围等指标,提升红外探测器片上处理能力,是未来红外探测器技术发展的重要方向之一。