22 nm低压差线性稳压器的设计

2022-03-04郭苹苹

郭苹苹

(上海电力大学 电子与信息工程学院,上海 200090)

集成电路的核心器件特征尺寸越来越小,传统体硅器件的短沟道效应变得越来越不可控,文献[1]中提出,当工艺节点进入到28 nm后,全耗尽绝缘体上硅器件凭借其优越的栅极控制能力和较低的漏电流,成为了替代体硅器件的一种选择。该器件为平面型晶体管结构,具有超薄顶层硅(SOI)和埋氧化层(BOX)结构,BOX的存在使FDSOI器件有了更多的优势,主要包括4个方面:(1)衬底电容可忽略不计,因此可降低电源电压,降低功耗;(2)没有闩锁效应(Latch-up),电路不需要特殊布局;(3)具有理想的器件隔离,器件布局更加紧密;(4)具有较低的漏电流,可降低功耗。

Global Foundries 22 nm FDSOI工艺是目前较先进的制造工艺,使用全耗尽绝缘体上硅器件,具有射频、体偏压和集成的优点,为减小电路尺寸,提高电路性能,设计一款22 nm高性能低压差线性稳压器是必要的;低压差线性稳压器以其功耗低、压差低、面积小和成本低等特点,被广泛用于各种电子设备中[2]。本文基于该先进工艺,设计了一款输入电源电压为1.8 V、输出电压为0.8 V、负载电流范围为1μA~30 mA的可以为低压低功耗模块提供电源的低压差线性稳压器。

1 电路系统结构与原理

本次设计的LDO电路的原理如图1所示。

图1 LDO整体架构图

LDO利用负反馈系统对输出电压进行实时控制,输出稳定的直流电压的电源模块,主要由基准电路(Reference)、误差放大器(EA)、功率器件(Pass Element)和反馈网络构成[3],实际工程中根据需求一般还会包括栅极驱动、频率补偿、过温保护与过流保护等其他模块[4]。

在LDO电路中,带隙基准电压源的作用是提供稳定的参考电压,带隙基准电压源是将正温度系数的电压与负温度系数的电压以不同的权重相加得到零温度系数的电压[5];误差放大器将基准参考电压VREF和反馈电压VFB进行比较得到误差信号,并将误差信号放大后控制功率管的栅极电压,改变流过功率管发电流大小,控制LDO输出电压的大小;采样电阻比例的调整可实现不同的电压输出,一般采样电阻的阻值都较大,可降低功耗;功率管决定LDO的驱动能力,同时用来调节输出电压的变化让其维持在一个恒定不变的值[6]。

LDO上电完成后电路启动,带隙基准电压源产生基准参考电压VREF,反馈网络通过采样为误差放大器提供反馈电压VFB,VFB与采样电阻R1和R2的关系如式(1)所示:

当VFB小于VREF时,通过环路控制作用,功率管的栅极电压被拉低,使更多的电流流过负载,提高输出电压;当VFB大于VREF时,功率管的栅极电压被抬高,限制流过负载的电流大小,降低输出电压;当VFB等于VREF时,反馈系统进入稳定状态[7],此时,输出电压不变。

2 LDO电路设计

2.1 误差放大器

LDO电路中的误差放大器采用两级运放结构,相比于折叠运放、套筒运放,两级运放的开环增益更高,功耗和噪声较低[8]。如图2所示,第一级为典型的电流镜负载差分放大器结构,由NM0、NM1、NM2、PM0和PM1 5个管子构成,用来提供更高的增益,第二级采用NMOS输入共源放大结构,由PM2、NM3构成,用于放大输出摆幅[9]。

图2 两级运算放大器

第一级差分放大增益AV1:

式(2)中,gm1为NM1管子的跨导,rp1为PM1管子的输出电阻,rN1为NM1管子的输出电阻。

第二级共源级放大器的增益AV2:

式(3)中,gm3为NM3管子的跨导,rp2为PM2管子的输出电阻,rN3为NM3管子的输出电阻。

两级运放的增益AV:

两级运放的增益在低频处可达60 dB以上。

2.2 功率管

PMOS功率管可以使功率级作为一个共源放大器结构,为LDO环路提供增益,同时,PMOS管漏源电压VDS为LDO的压差,当PMOS管处于饱和区时,很小的漏源电压VDS就可以产生足够的输出电流[10]。若功率管采用NMOS管,NMOS管构成的是源级跟随器结构,不能为LDO环路提供增益,LDO的压差是NMOS管的栅源电压VGS,LDO的压差大于NMOS管的阈值电压VTH才能输出较大的电流,这个数值通常很大。所以本文采用PMOS管作为功率管。

最大负载电流、版图面积,漏失电压都影响功率管尺寸的大小,PMOS功率管尺寸的选择不仅要满足所需要的负载电流,而且要尽可能减小功率管的尺寸来减小版图面积,同时可以减小功率管的寄生电容,使环路更容易稳定,功率管宽长比的计算公式为:

式(5)中,IOUT,MAX为输出负载电流最大值,μPOW为载流子的迁移率,Cox为单位面积栅氧化层电容,Vdsat为过驱动电压。

3 电路仿真

基于Global Foundries 22 nm FDSOI工艺完成LDO设计,在该工艺下,采用Cadence中的Spectre仿真工具对该电路的功能进行了仿真。

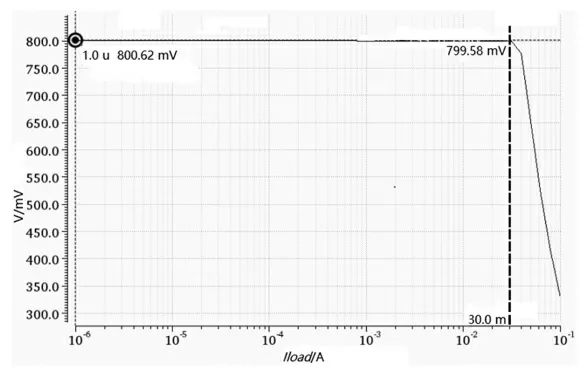

3.1 LDO负载调整率仿真

负载调整率是指当输出负载电流变化时,LDO输出电压仍然能够保持稳定的能力,负载调整率越小越好。负载调整率仿真波形图如图3所示,当输出负载电流从1μA扫描到30 mA,LDO输出电压从800.62 mV变化到799.57 mV,变化了约1.1 mV,误差很小,根据负载调整率的公式可以计算出该LDO的负载调整率:

图3 LDO负载调整率仿真波形图

3.2 LDO线性调整率仿真

线性调整率反应的是LDO的低频电源增益,是描述当直流输入电源电压变化时,LDO是否能抑制这种变化仍然保持输出电压的稳定。在负载电流ILoad=20 mA,温度为25℃的情况下进行仿真,仿真波形图如图4所示,从图中可看出,当电源电压从1.1 V变化到2 V时,LDO的输出电压变化范围很小,约为1.7 mV,由此可计算出LDO的线性调整率:

图4 LDO线性调整率仿真波形图

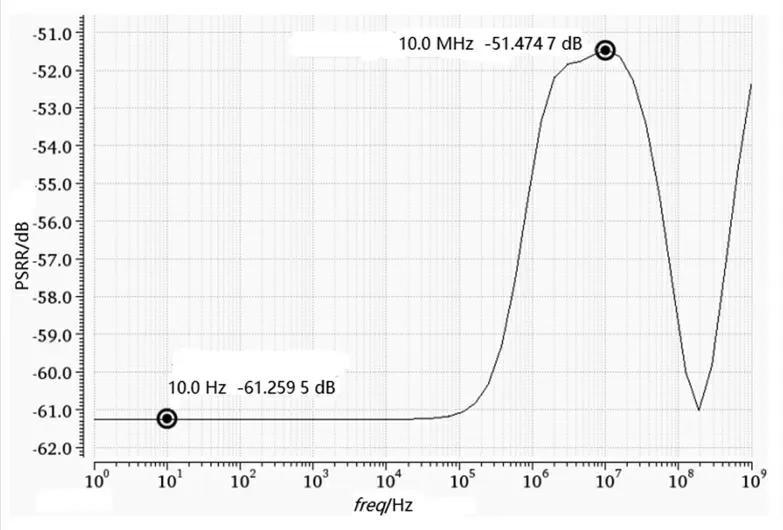

3.3 LDO电源电压抑制比(PSRR)特性仿真

电源电压抑制比是描述输出电压随电源电压变化而变化的特性,电源电压抑制比越高,表明该LDO的抑制纹波能力越强。仿真结果如图5所示,频率从1 Hz扫描到1 GHz,在频率为10 Hz时,对应的PSRR为61.26 dB,在10 MHZ对应最低点,可达到51.47 dB,在高频时PSRR会略有下降,这是因为高频时运放对电路有抑制作用。

图5 LDO电源电压抑制比仿真波形图

3.4 LDO环路稳定性仿真

LDO系统是一个负反馈系统,环路稳定性对于LDO是极其重要的,一般要求相位裕度要在60 dB以上。因此需对其稳定性进行仿真,在负载电流为30 mA的条件下,LDO的stb仿真波形如图6所示;在负载电流1μA的条件下,仿真波形图如图7所示。

根据图6和图7的仿真结果,当负载电流为1μA时,LDO的低频增益约为100 dB,相位裕度为86.31°,环路稳定;当负载电流为30 mA时,LDO的低频增益约为69.68 dB,相位裕度为76°,环路稳定;随着输出负载电流的增大,相位裕度下降,低频增益降低,在1μA~30 mA时,相位裕度在76°~86.31°,低频增益在69.68~100 dB,因此,在1μA~30 mA时,环路都有足够的低频增益且都保持稳定。

图6 负载电流30 mA时LDO稳定性仿真波形图

图7 负载电流1μA时LDO稳定性仿真波形图

4 结论

本文基于Global Foundries 22 nm FDSOI先进工艺设计了一款22 nm的低压差线性稳压器,该LDO结构简单,易于实现,性能良好,通过将传统的五管运算放大器与共源放大器级联组成了LDO的误差放大器,该误差放大器具有较高的增益且稳定性好,仿真结果表明:在温度为25℃,输入电源电压为1.8 V,LDO电路稳定输出电压为800 mV,电路在1μA~30 mA都有较好的稳定性,并且在负载调整率、线性调整率和电源电压抑制比方面都表现良好。