基于FPGA的在线调试软件设计

2022-03-03董志丹

李 卿,董志丹,惠 锋

(无锡中微亿芯有限公司,江苏无锡 214072)

1 引言

目前,赛灵思(Xilinx)与阿尔特拉(Altera)占据近90%的现场可编程逻辑门阵列(Field-Programmable Gate Array,FPGA)电路市场份额,形成垄断的格局[1],而国内FPGA技术还处于起步阶段,因此,FPGA国产化迫在眉睫。国产FPGA的推广与使用必然离不开在线调试软件的支撑,在线调试软件作为FPGA应用开发软件的重要组成部分,能有效提高用户调试效率,缩短设计开发周期,对国产化FPGA产业起到积极的推动作用。

传统的调试设备因其价格昂贵、需引出的输入输出管脚受限等因素已无法满足日益发展的FPGA需求[2-3],因此,世界领先的FPGA厂商在推出FPGA产品的同时也推出了相应的系统逻辑分析仪,如Xilinx公司的Chipscope片上逻辑分析仪、Altera公司的Signal TAPII嵌入式逻辑分析仪、爱特(Actel)与新思科技(Synopsys)联合推出的Identify AE在线调试工具[4-7]。它们均通过软核实现芯片内的信号采集,然后使用计算机软件实时监测FPGA芯片的内部信号变化。该方式操作方便、价格低廉,能快速实现复杂FPGA的在线调试[4]。本文设计的在线调试软件也是基于软核实现,与Xilinx调试软件相比具有更好的用户体验、调试效率和调试准确度。目前,该软件已成功应用于国产FPGA芯片中,大大推动了国内FPGA技术的发展。

2 软件设计流程

本文设计的在线调试软件采用软核-嵌入式逻辑分析核(Integrated Logic Analyzer,ILA)实现芯片内的信号采集,然后通过用户图形界面显示FPGA内部的调试信号。它由ILA核属性配置软件和信号分析软件组成。ILA核属性配置软件主要用于参数配置,并根据用户配置生成在线调试的软核。信号分析软件则对触发信号、捕获条件等进行设置,并以波形图显示调试结果,供用户调试参考。

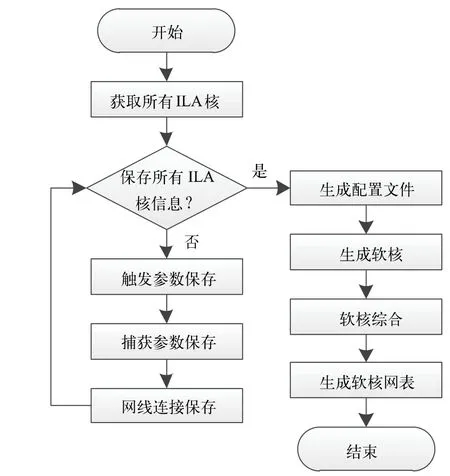

2.1 ILA核属性配置软件设计流程

ILA核属性配置软件流程如图1所示,ILA核属性配置软件对调试所需的信息进行配置。通过该属性配置,一方面生成反映用户配置的配置文件,另一方面生成用户配置的软核网表文件;根据用户配置的连接关系将软核网表文件插入用户源网表文件中,生成含有调试信息的网表文件;最后执行装箱、布局布线、位流生成。本软件在执行FPGA流程时采用自主FPGA应用开发软件。

图1 ILA核属性配置软件流程

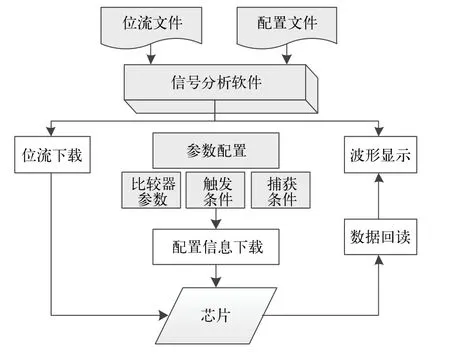

2.2 信号分析软件设计流程

位流文件生成后即可启动信号分析软件,其将位流下载至目标芯片后,便可开始调试工作。信号分析软件图形化显示ILA核配置信息,供用户配置触发参数、捕获参数等;将配置信息通过调试接口(Joint Test Action Group,JTAG)下载到目标芯片,用户电路在芯片运行的过程中,当满足触发条件时,ILA核采集信号并存储在芯片内的随机存取存储器块中,并通过JTAG将采集到的信号上传至信号分析仪软件;该软件将显示回读数据的波形图,方便用户查看调试信息。信号分析软件设计流程如图2所示。

图2 信号分析软件流程

3 软件设计实现

本软件由自主FPGA应用开发软件集中调度管理。根据用户逻辑综合后的网表文件,用户可创建ILA核、配置参数信息、生成在线调试的软核,并执行装箱、布局布线、位流生成,最后下载至芯片,通过信号分析软件观察调试信息,完整地实现FPGA项目设计开发的整个流程,有效地满足了用户创建、编译和调试FPGA应用开发的需求。

目前,用户广泛使用Xilinx ISE工具进行FPGA应用开发与调试,为便于用户理解以及代码移植,本软件在模块划分与命名上尽量与Xilinx Chipscope保持一致。在线调试软件由ILA核属性配置软件和信号分析软件组成,并通过FPGA应用开发软件编译生成位流文件。

3.1 ILA核属性配置软件

用户可自主创建所需的ILA核,并根据需求配置每个ILA核属性。ILA核属性配置软件根据用户配置生成相应的软核,并将软核与源用户网表合并,生成含有调试信息的网表文件,设计流程见图1。软件主要由软核、属性配置、网表合并三大模块组成。

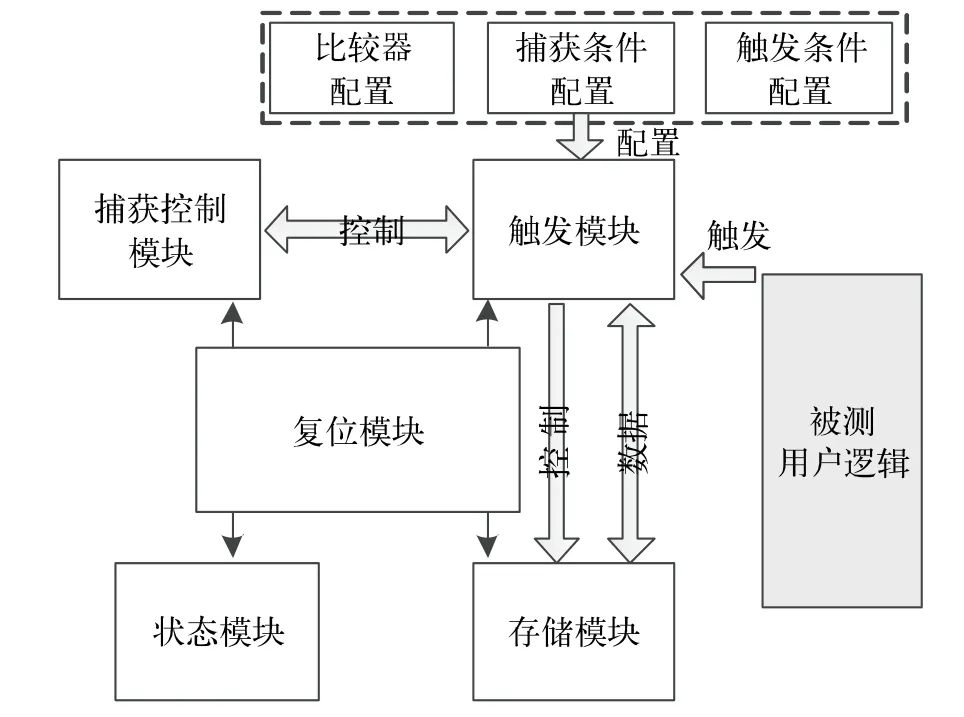

3.1.1 软核

软核实现了芯片内的信号采集,是在线调试软件的基础。它主要由复位模块、触发模块、捕获控制模块、存储模块、状态模块组成,其模块划分如图3所示。复位模块用于产生8路复位信号,分别送给其他不同模块;触发模块负责匹配比较器、触发条件以及捕获条件的配置,当满足条件时给出检测成功的标志信号;捕获控制模块负责在数据捕获阶段产生存储逻辑所需要的写使能以及写地址信号,同时需产生捕获结束的标志信号;存储模块负责在捕获模块的写控制下将捕获数据写到芯片内存块中;状态模块负责记录用户配置的静态信息和捕获过程的动态信息。

图3 软核模块划分

触发模块为软核的核心模块,只有满足触发条件时才捕获被测用户逻辑数据,而触发条件的比较基于比较器实现。与Chipscope一致,本软件共支持Basic、Basic edge、Extend、Extend edge、Range、Range edge 6种比较器,不同比较器类型实现功能不同。比较器实现的最小单元是逻辑簇(SLICE),不同位宽的比较器需要不同数量的SLICE来实现。下面以Basic比较器为例讲述软核中比较器设计实现原理。

Basic比较器如图4所示,用来比较输入数据和预设的向量是否一致,一致则输出为高电平,否则为低电平。该比较器通过移位寄存器(SRL)实现,一个SLICE可比较19位,由3个SRL 32和1个SRL 16组成。为了简化,3个SRL 32记作SRL 32_C,SRL 32_B,SRL 32_A。当配置数据时,需要将预设的向量编码进查找表(LUT)中,即数据[4:0]分配到SRL 32_A上,数据[9:5]分配到SRL 32_B上,数据[14:10]分配到SRL 32_C上,数据[18:15]分配到SRL 16上;然后分别计算出对应的SRL编码,SRL 32的编码长度是32位,SRL 16的编码长度是16位,要匹配的数据选中位为1,其余位为0;最后将SRL编码按照低位组在前、高位组在后的顺序拼接,即:

图4 Basic比较器

这样当LUT地址选择端为预设的向量时,LUT就会输出1,从而实现了电平比较的功能。

3.1.2 属性配置

用户可自主创建所需的ILA核,本软件最多支持16个核的创建。针对每个ILA核用户可配置其属性,主要包括触发参数、捕获参数、信号连接。触发参数主要是对比较器参数、触发类型进行配置,如比较器位宽、比较器类型、是否使能比较器计数器、是否使能序列触发等;捕获参数主要包括数据捕获宽度、捕获深度、时钟采样方式;信号连接主要是对时钟信号端口、触发信号端口、要观测的数据信号端口进行配置。

ILA核属性配置较多、特别是用户逻辑较为复杂时,快速连接待测信号并非易事。为提高软件的用户体验度,本软件在信号连接模块提供了查找过滤功能,根据用户输入进行快速匹配。此外,还增加了批量信号连接、删除、上移、下移等操作,方便用户配置。

当用户属性配置完毕后,即生成在线调试的软核。此外,软核生成时还保存了反映用户配置的配置文件,该文件主要用于指导用户源网表与软核网表文件合并,以及信号分析软件配置界面的展示。软核生成流程如图5所示。

图5 软核生成流程

3.1.3 网表合并

软核网表文件生成之后,即可根据用户配置的ILA核信号连接关系与源用户网表文件进行合并,生成含有调试信息的新网表。新网表作为FPGA编译流程的输入,最终生成含有调试信息的位流文件,其流程如图6所示。

图6 网表合并流程

3.2 在线调试编译流程

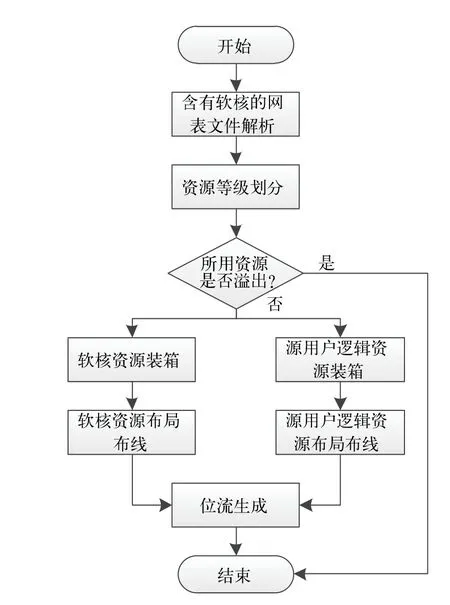

含有调试信息的网表文件生成之后,即可执行FPGA全流程,生成含有调试信息的位流文件,并通过JTAG下载至芯片中运行。该流程采用自主FPGA应用开发软件执行。因软核插入至源用户逻辑中,占用芯片内部资源,后续布局布线容易导致源用户逻辑行为发生变化,进而影响调试的准确性[8-9],故FPGA应用开发软件针对在线调试设计了一种高准确度的在线调试编译方法,其流程如图7所示。对芯片所用资源进行等级划分,并分别对源用户逻辑资源和软核资源进行装箱、布局布线,最终生成含有调试信息的位流文件。经验证,该方法能确保在加入软核前后,源用户逻辑行为不发生变化,从而使调试更加准确。

图7 在线调试编译流程

3.3 信号分析软件

信号分析软件图形化显示其配置页面,用户可根据需求自主配置比较器参数值、触发条件、数据捕获条件,并动态生成相应的配置数据,通过JTAG[10]将配置数据下载至芯片中。当满足触发条件时,芯片捕获数据并回传至信号分析软件。信号分析软件对捕获数据进行整理并以波形图显示调试信息,方便用户进行问题分析。整个软件设计流程见图2。

信号分析软件的核心为将图形界面的用户参数转换为芯片对应模块的配置信息,完成对芯片模块的配置,达到测试的目的。对每个模块的配置都可以分成两步走:

(1)发送预选命令,使能该模块(链)的配置使能信号;(2)根据配置算法计算出该模块(链)的配置数据,然后加入同步头进行发送,当同步成功,该链的配置使能变高,开始配置,当配置结束时,配置使能也变低,精确控制配置链的移位。

值得注意的是同一条配置链的模块需要一起配置,ILA核中包含的配置链如下:

(1)比较器0→比较器0计数器;

(2)比较器1→比较器1计数器;

……

(16)比较器15→比较器15计数器(最多16个比较器);

(17)布尔触发条件模块→捕获条件模块;

(18)序列触发条件模块;

(19)窗口控制模块。

配置数据下载流程如图8所示。经验证,配置数据下载和波形图显示回读数据效率较高,较Chipscope效率显著提升,大大缩短了调试周期。另外,波形图可通过滚轮直接进行缩放,操作简单、舒适,并提供多种进制的数据显示,方便用户进行数据分析。

图8 配置数据下载流程

4 测试结果与分析

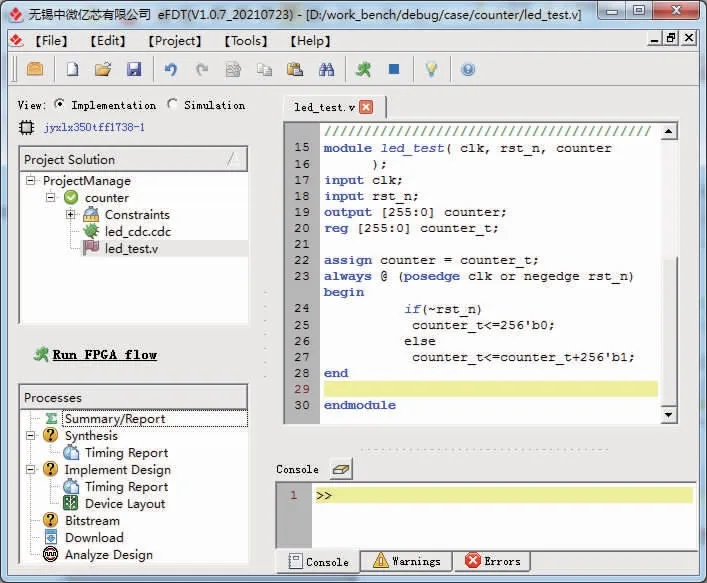

本文所述的在线调试软件已应用至国产FPGA芯片应用中。经用户试用反馈,与Xilinx Chipscope相比,本软件具有较大的优点:(1)较好的用户体验度,如波形图缩放、信号连接等;(2)较高的调试效率,如配置数据下载和波形图显示结果的效率大幅度提升;(3)较高的调试准确度,确保软核的加入不影响源用户逻辑行为。对国产化FPGA产业起到积极的推动作用。现以实现计数器功能的用例(见图9)进行说明,用户在FPGA应用开发软件中编写逻辑代码。

图9 用户逻辑

逻辑代码编写完毕,用户便需利用在线调试软件验证代码功能的正确性。ILA核属性配置软件如图10所示,在触发参数配置页面中设置使用一个Basic比较器,比较器位宽为10,不使能比较器计数器;在捕获参数配置页面中设置数据捕获深度为1024,数据捕获宽度为10;在信号连接属性页中配置要调试的信号为counter_r<0>~counter_r<9>。属性配置完毕即可生成在线调试的软核,其与源用户网表合并后生成含有调试信息的网表文件。

图10 ILA核属性配置软件

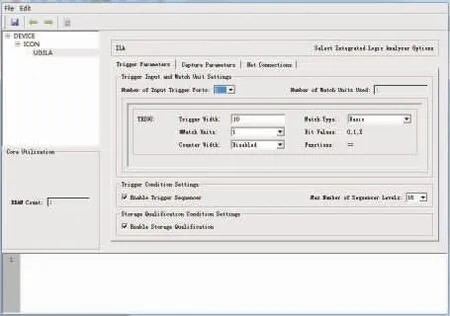

含有调试信息的网表文件执行FPGA流程后,生成用于调试的位流文件,该位流文件经JTAG下载至芯片中即可通过信号分析软件查看调试信息。在信号分析软件中设置触发条件如图11所示,比较器的值设置为40,捕获深度为1024,捕获位置为10。

图11 信号分析软件——触发条件

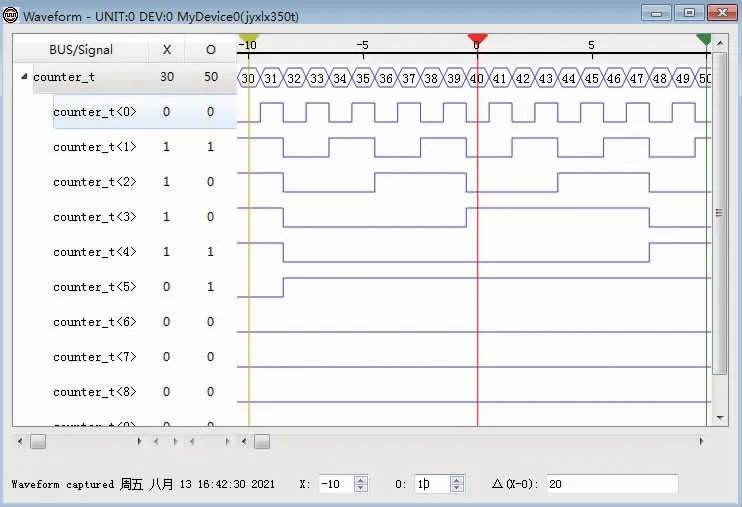

波形图展示芯片捕获的数据如图12所示。经分析发现,芯片共捕获1024个数据,触发点值为40,触发位置前捕获了10个数据,且捕获的数据正确实现了计数功能。因此,用户设计的逻辑代码功能正确。

图12 信号分析软件——波形

5 结束语

随着FPGA的飞速发展,其设计越来越复杂,致使调试工作也越来越繁重。本文设计的在线调试软件由ILA核属性配置软件生成用于调试的软核,经FPGA全流程生成含有调试信息的位流文件并下载至芯片中运行,通过信号分析软件查看调试结果。经验证,本软件可有效提高调试效率,缩短设计开发周期,对国产化FPGA产业起到积极的推动作用。但是,软核占用芯片内部资源,使用芯片资源较多的用户逻辑将增加调试难度,故软核优化将是今后研究的重点。